A protection circuit and protection method for a reliability test structure of a semiconductor device

A technology for protecting circuits and test structures, applied in semiconductor devices, semiconductor/solid-state device parts, emergency protection circuit devices, etc., can solve problems such as inaccurate test results, inaccurate TDDB life, and influence of reliability test structures

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0041] A specific embodiment of the present invention will be further described below in conjunction with the accompanying drawings.

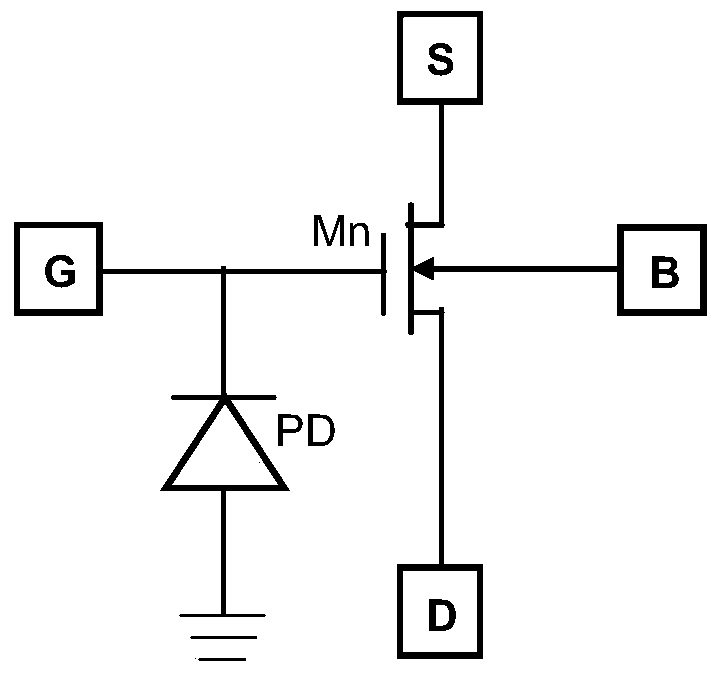

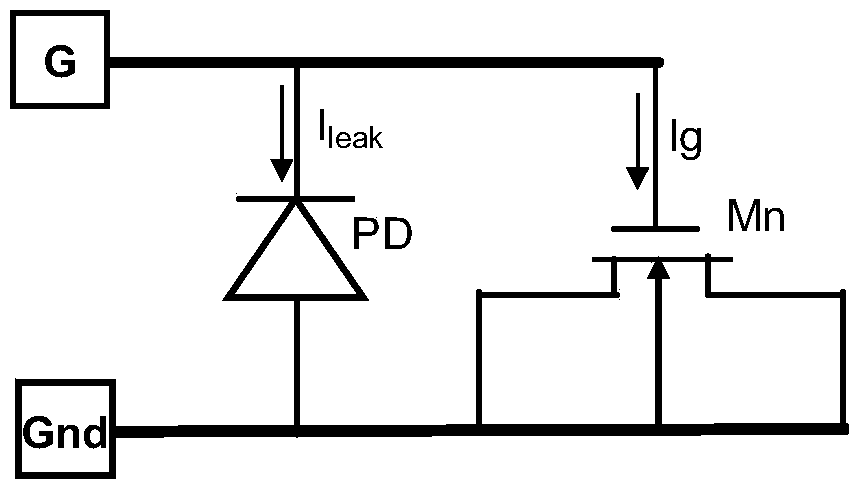

[0042] Among them, the image 3 It is a schematic diagram of the protection circuit of the improved circuit according to the present invention. As shown in the figure, the MOS device in this figure is an NMOS transistor, and the NMOS transistor includes a gate and a source and drain located on both sides of the gate, wherein the protection circuit includes a diode and a fuse structure connected in series, wherein the protection The anode of the diode is connected to one end of the fuse structure, the cathode of the protection diode is connected to the gate of the MOS device to be tested, and the other end of the fuse structure is grounded.

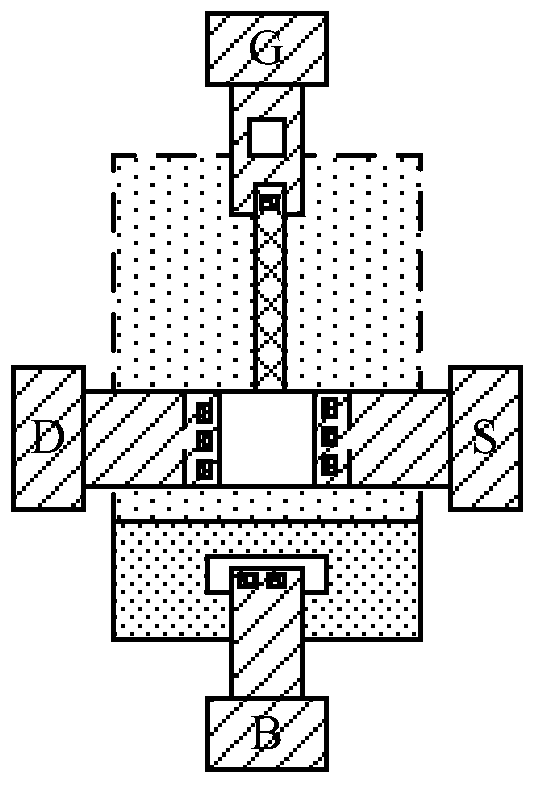

[0043] Preferably, the protection diode is a PN junction, and in the NMOS transistor, the protection diode is a PN junction formed by N-type doping and a P well, wherein 4a-4c are the detection devices des...

Embodiment 2

[0051] A specific embodiment of the present invention will be further described below.

[0052] Wherein, in this embodiment, the MOS device is a PMOS transistor, and the PMOS transistor includes a gate and a source drain located on both sides of the gate, wherein the protection circuit includes a diode and a fuse structure connected in series, wherein the protection diode The anode of the protection diode is connected to one end of the fuse structure, the cathode of the protection diode is connected to the gate of the MOS device to be tested, and the other end of the fuse structure is grounded.

[0053] Preferably, the protection diode is a PN junction. In the PMOS transistor, the protection diode is a PN junction formed by P-type doping and an N well, and its layout structure is the same as that shown in 4a-4c in Embodiment 1. The layout structure schematic diagram of the protection circuit of the detection structure is similar.

[0054] Preferably, the source and drain of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More