Semiconductor device, diagnostic test, and diagnostic test circuit

A diagnostic test and semiconductor technology, which is applied in the field of diagnosis of multiple CPU cores, can solve problems such as operational performance deterioration, and achieve the effect of preventing deterioration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

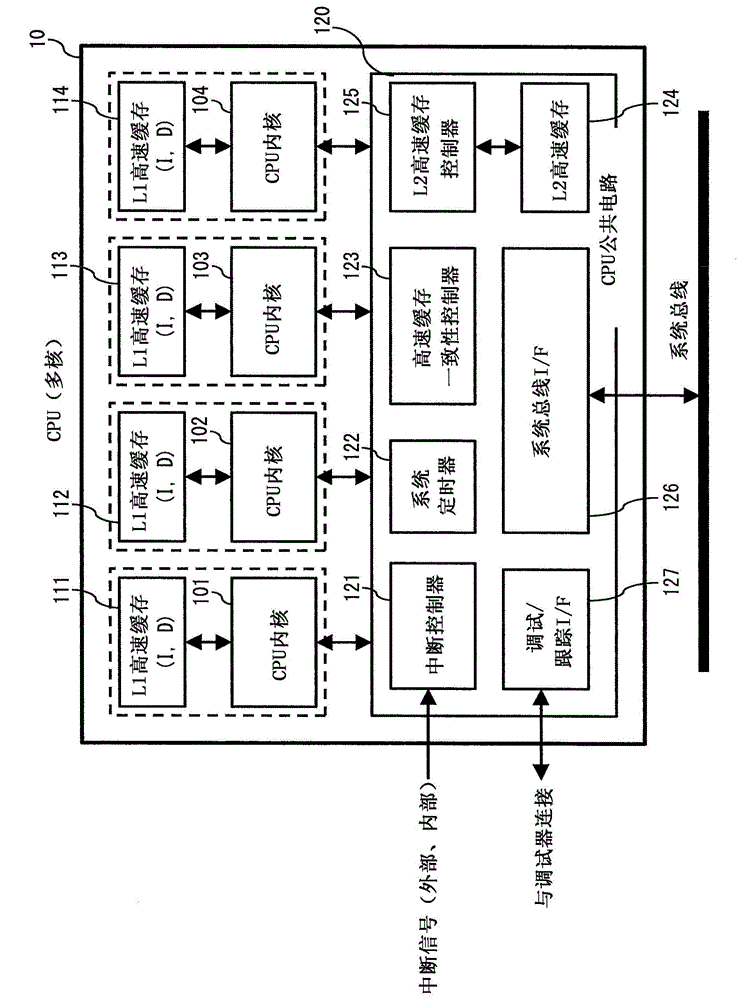

[0046] First, the configuration and operation according to the first embodiment will be described with reference to the drawings.

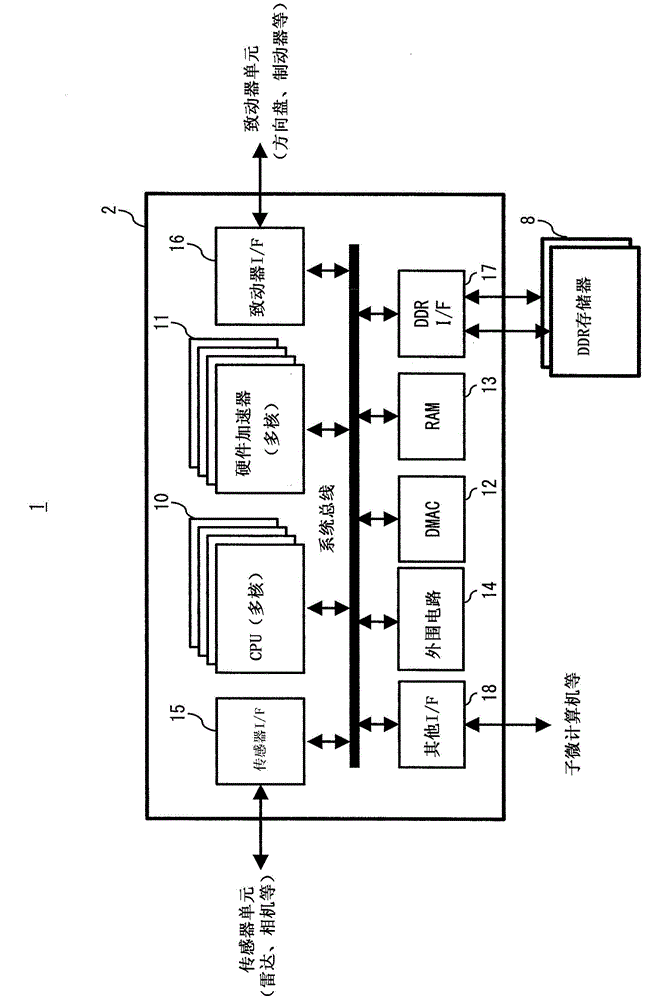

[0047] figure 1 is a block diagram showing an example of a configuration of a CPU system 2 for an ADAS (Advanced Driver Assistance System) of an in-vehicle ECU (Electronic Control Unit) 1 that requires high operational performance. The on-vehicle ECU 1 includes a CPU system (main microcomputer) 2 and a plurality of DDR (Double Data Rate) memories 8 as external memories. The CPU system 2 includes an internal processing circuit, a CPU (multi-core) 10 with a multi-core architecture, a hardware accelerator (multi-core) 11 with a multi-core architecture, a DMAC (Direct Memory Access Controller) 12, a RAM (Random Access Memory) 13, and others Peripheral Circuitry 14. Also, the CPU system 2 includes a sensor I / F 15 , an actuator I / F 16 , a DDR I / F 17 , and other I / F 18 as circuits for external interfaces.

[0048] These circuits 10 to 18 are connected...

no. 2 example

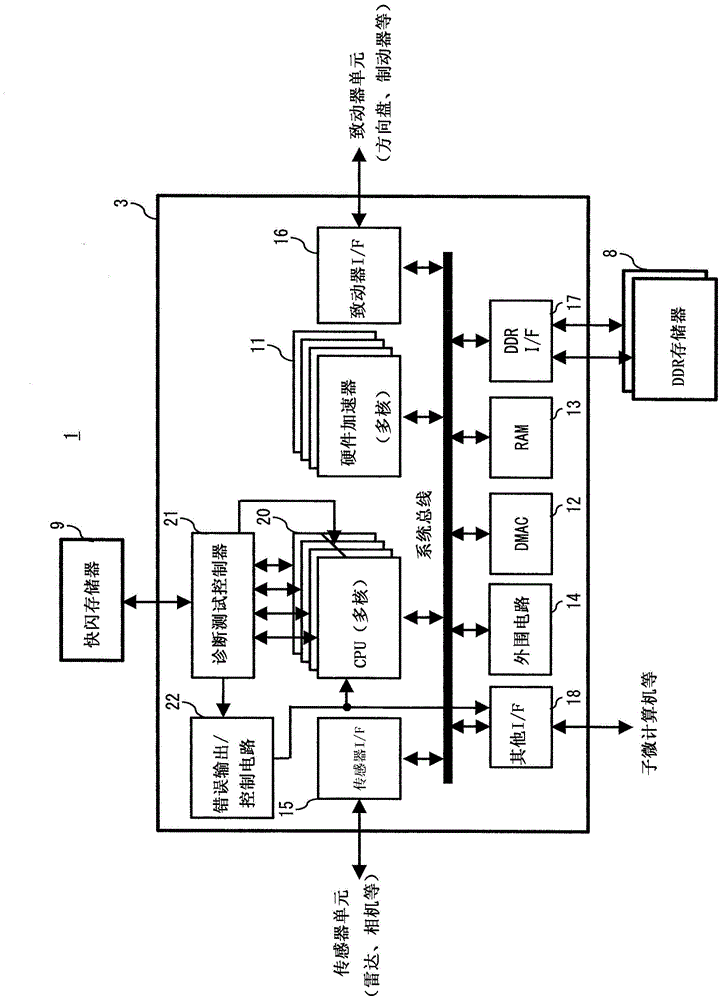

[0109] Next, the configuration and operation according to the second embodiment will be described with reference to the drawings.

[0110] The configuration and operations of the second embodiment are basically similar to those of the first embodiment. That is, the components of the second embodiment are the same as those in image 3 Basically similar to those in the CPU system 3 shown in the CPU system 3 included in Figure 4 The CPU shown in 20 and the Figure 5 The CPU core 101 (each of the CPU cores 102 to 104 is similar to the CPU core 101 ) and the scan test circuit 201 (each of the scan test circuits 202 to 204 is similar to the scan test circuit 201 ) are shown in . Also, execution of diagnostic tests for the CPU cores 101 to 104 according to the second embodiment is also similar to that in Figure 6 and 7 Execution of the diagnostic tests for the CPU core shown in .

[0111] However, the input test pattern for the scan test input to the CPU cores 101 to 104 has 8...

no. 3 example

[0125] Next, the configuration and operation according to the third embodiment will be described with reference to the drawings.

[0126] Figure 14 is a block diagram showing the configuration of the CPU system 4 according to the third embodiment. with in image 3 The CPU system 3 according to the first embodiment shown in is different in that the CPU system 4 additionally includes a startup time test circuit 24 that performs a diagnostic test for a diagnostic test controller 25 when the system is started.

[0127] When the CPU system 4 is started, the startup time test circuit 24 executes a diagnostic test for the diagnostic test controller 25 before the diagnostic test controller 25 starts execution of the diagnostic test for the CPU cores 101 to 104 . Note that the diagnostic test controller 25 according to the third embodiment is obtained by adding a circuit for performing a diagnostic test for the diagnostic test controller 25 in the diagnostic test controller 21 . De...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More