Backside illuminated image chip module structure and fabrication method thereof

A technology of chip module and manufacturing method, which is applied in the direction of radiation control devices, etc., can solve the problems of high packaging cost, difficult to meet, and high cost, and achieve the effect of realizing packaging product cost, simplifying circuit design, and realizing overall cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0050] The technical solutions of the present invention will be further described below in conjunction with the accompanying drawings and through specific implementation methods.

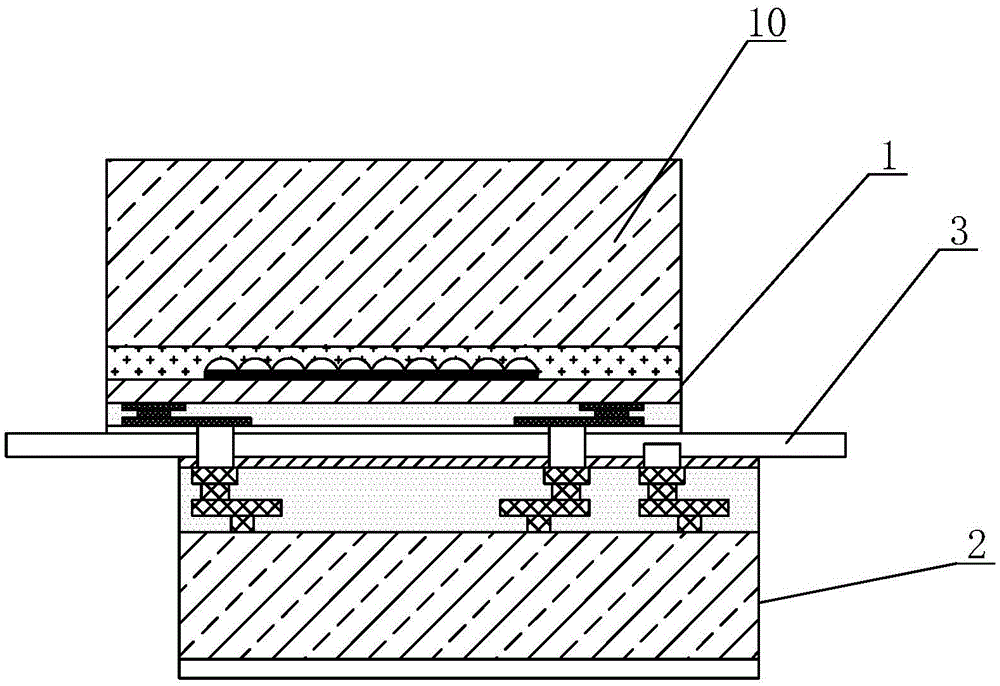

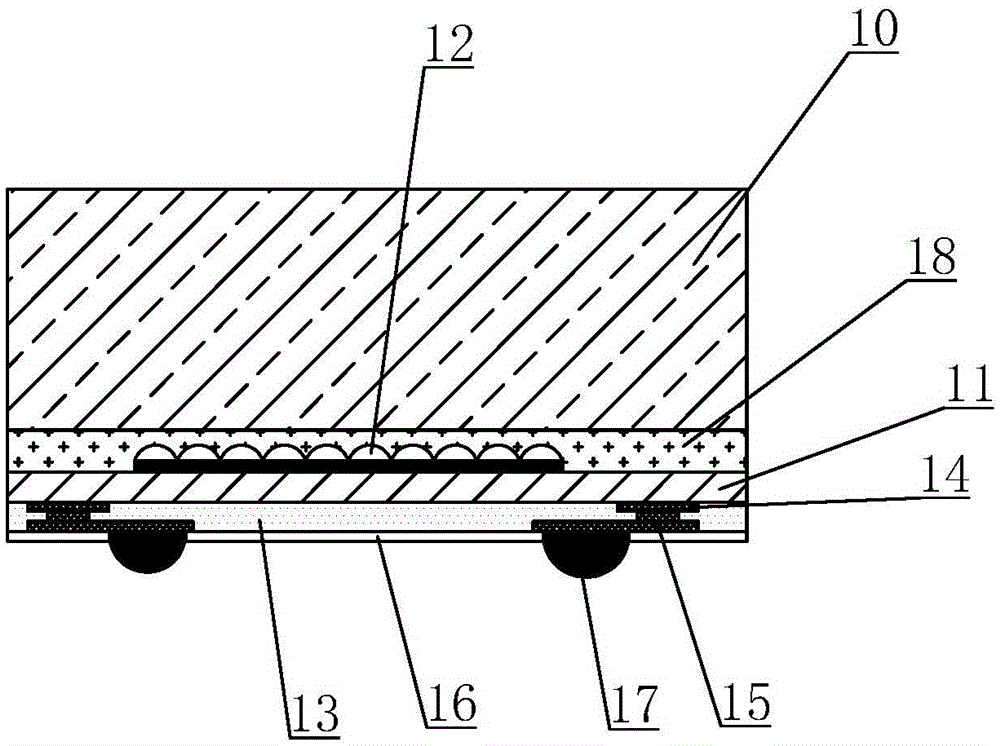

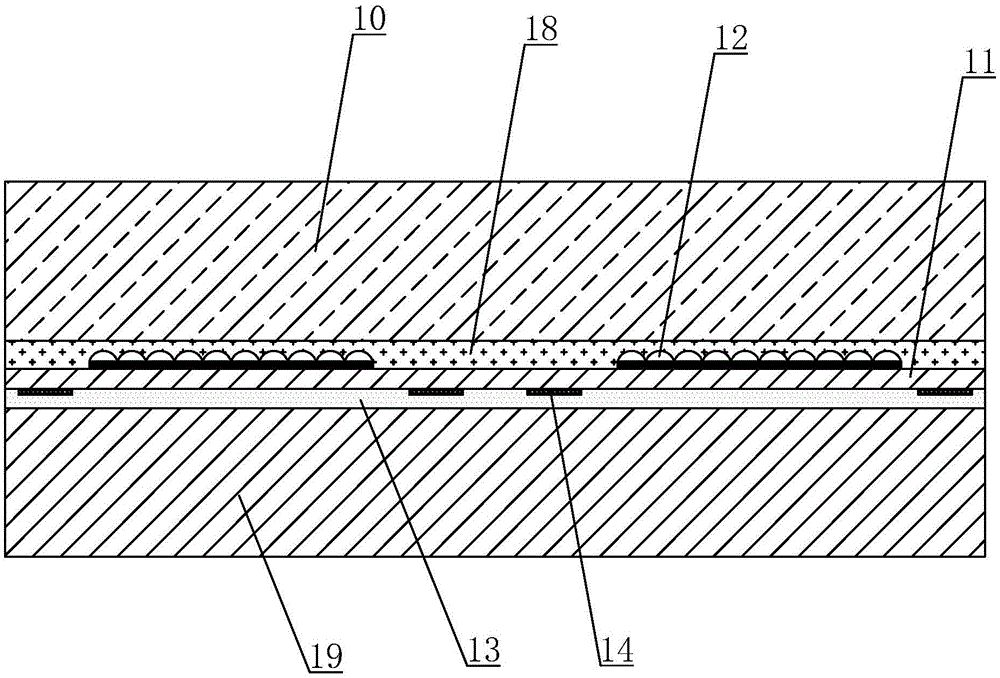

[0051] see Figure 1 to Figure 13As shown, in this embodiment, a back-illuminated image chip module structure includes a BSI chip 1, an ADC chip 2 and a soft board 3, and the ADC chip 2 is arranged under the soft board 3 and is connected to the The flexible board 3 is electrically connected, the BSI chip 1 is arranged on the top of the flexible board 3 and corresponding to the ADC chip 2, and the BSI chip 1 and the ADC chip 2 are directly connected through pads on both.

[0052] The BSI chip 1 includes a cover glass 10 and an image chip, the image chip includes a silicon wafer 11, the surface of the silicon wafer 11 is provided with several micro-convex mirrors 12, and its back is provided with a first insulating layer 13 , the first insulating layer 13 is provided with an internal interconnection ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More