Method for Improving Contact Hole Morphology of Semiconductor Devices

A contact hole and semiconductor technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as adverse effects on product reliability, achieve low cost and improve reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

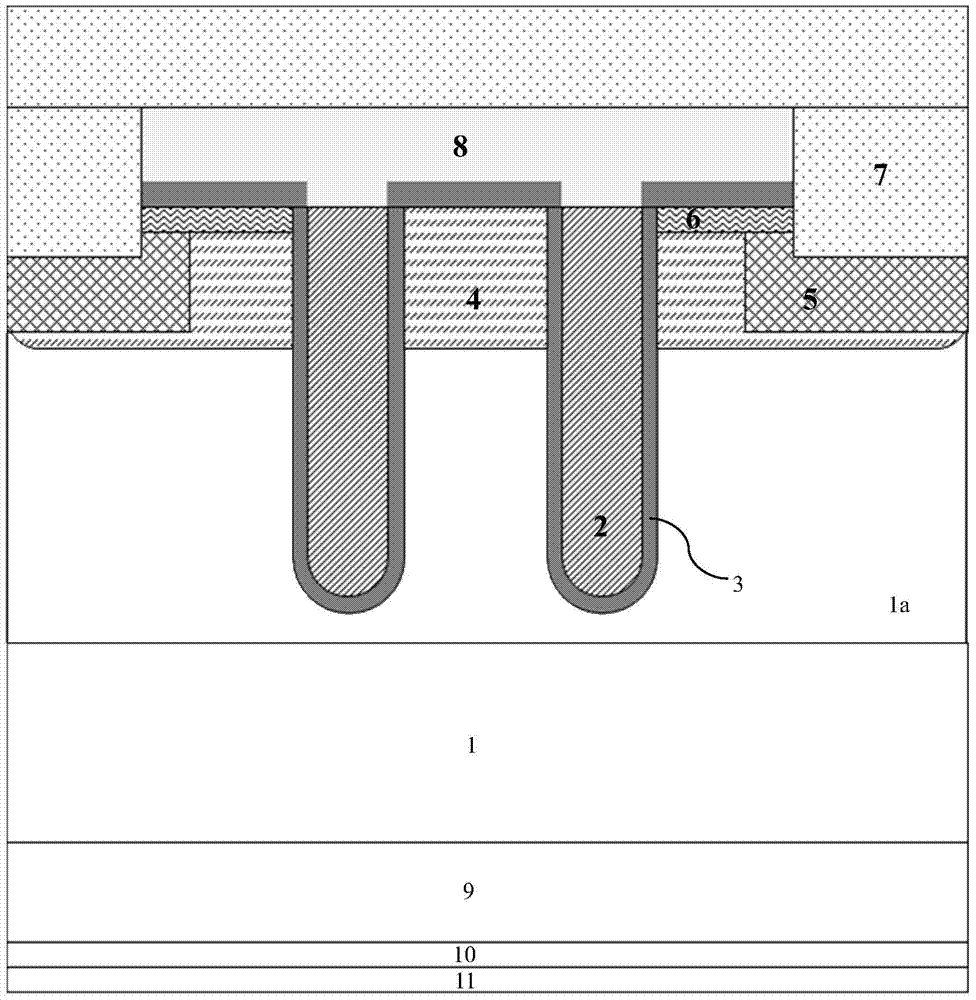

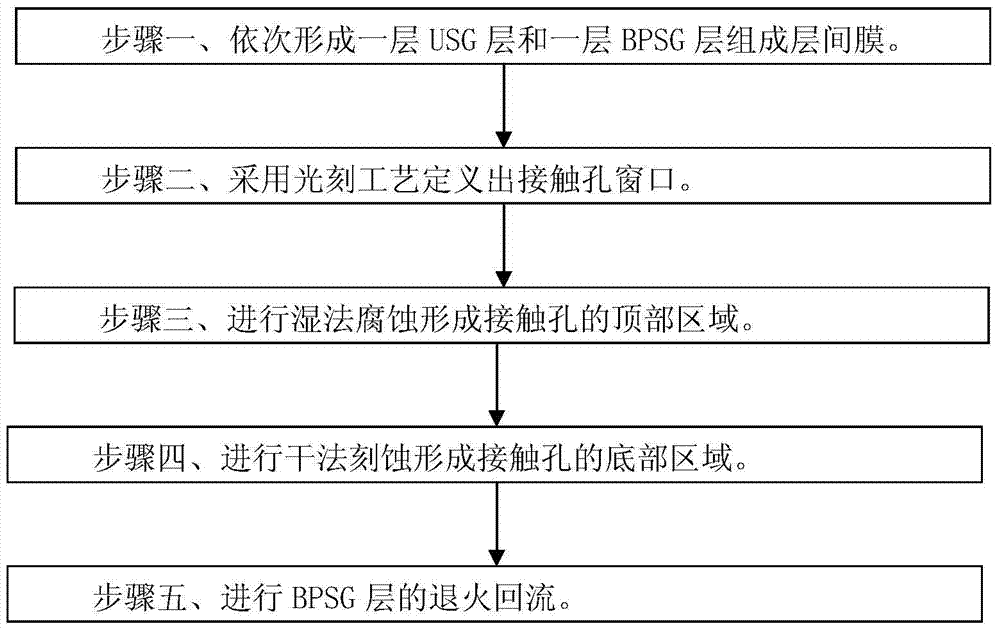

[0033] Such as image 3 Shown is the flow chart of the method of the embodiment of the present invention; in the embodiment of the present invention, the semiconductor device is as figure 1 The IGBT device shown is illustrated as an example for forming figure 1 shown in the contact hole 7. The method for improving the morphology of a contact hole of a semiconductor device in an embodiment of the present invention includes the following steps:

[0034] Step 1, on the semiconductor substrate where contact holes need to be formed, namely figure 1 A USG layer and a BPSG layer are sequentially formed on the surface of the N-type substrate 1 shown, and an interlayer film 8 is formed by superimposing the USG layer and the BPSG layer, which is performed before annealing and reflowing the BPSG layer. Follow steps 2 to 4.

[0035] In the embodiment of the present invention, the thickness of the USG layer is 2000 angstroms, and the thickness of the BPSG layer is 9000 angstroms.

[0...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More