Preparation method of N-type silicon chip a-Si:H film for heterojunction with intrinsic thin layer (HIT) battery

An a-si, N-type technology, used in circuits, photovoltaic power generation, electrical components, etc., can solve the problems of lack of preparation technology, difficult to meet the quality of thin films, etc., and achieve the effect of improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

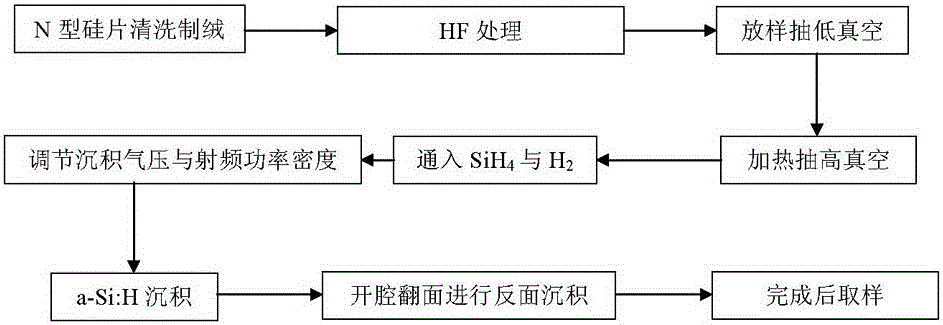

[0025] A kind of preparation method of N-type silicon chip a-Si:H film for HIT battery of the present invention, technological process is as figure 1 shown, including the following steps:

[0026] (1) N-type silicon wafer cleaning and texturing: N-type silicon wafers used for HIT cells are cleaned and textured, mainly to complete the removal of the mechanical damage layer on the surface of the silicon wafer and the preparation of the pyramid texture, and remove the damaged layer on the surface of the silicon wafer on one side 18μm, the diagonal size of the pyramid is 5-8μm.

[0027] (2) Deoxidation layer treatment (HF treatment): After the N-type silicon wafer is cleaned and textured, it is placed in an HF solution with a volume concentration of 2.5% and reacted for 16 seconds to mainly remove the natural oxide layer on the surface of the silicon wafer, and the process is completed. Take it out and rinse it with deionized water, N 2 blow dry.

[0028] (3) Deposition of a-Si...

Embodiment 2

[0036] A kind of preparation method of N-type silicon chip a-Si:H film for HIT battery of the present invention, technological process is as figure 1 shown, including the following steps:

[0037] (1) N-type silicon wafer cleaning and texturing: N-type silicon wafers used for HIT cells are cleaned and textured, mainly to complete the removal of the mechanical damage layer on the surface of the silicon wafer and the preparation of the pyramid texture, and remove the damaged layer on the surface of the silicon wafer on one side 22μm, the diagonal size of the pyramid is 6-10μm.

[0038] (2) Deoxidation layer treatment (HF treatment): After the N-type silicon wafer is cleaned and textured, it is placed in an HF solution with a volume concentration of 3%, and reacted for 10s to mainly remove the natural oxide layer on the surface of the silicon wafer, and the process is completed. Take it out and rinse it with deionized water, N 2 blow dry.

[0039] (3) Deposition of a-Si:H thin f...

PUM

| Property | Measurement | Unit |

|---|---|---|

| size | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More