Planar split dual-gate thin film transistor and preparation method thereof

A thin film transistor, plane separation technology, applied in transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problems of narrow dynamic range of automatic gain control, threshold voltage drift, large signal blockage, etc., to solve threshold voltage drift, The effect of simplifying the circuit and expanding the scope of application

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

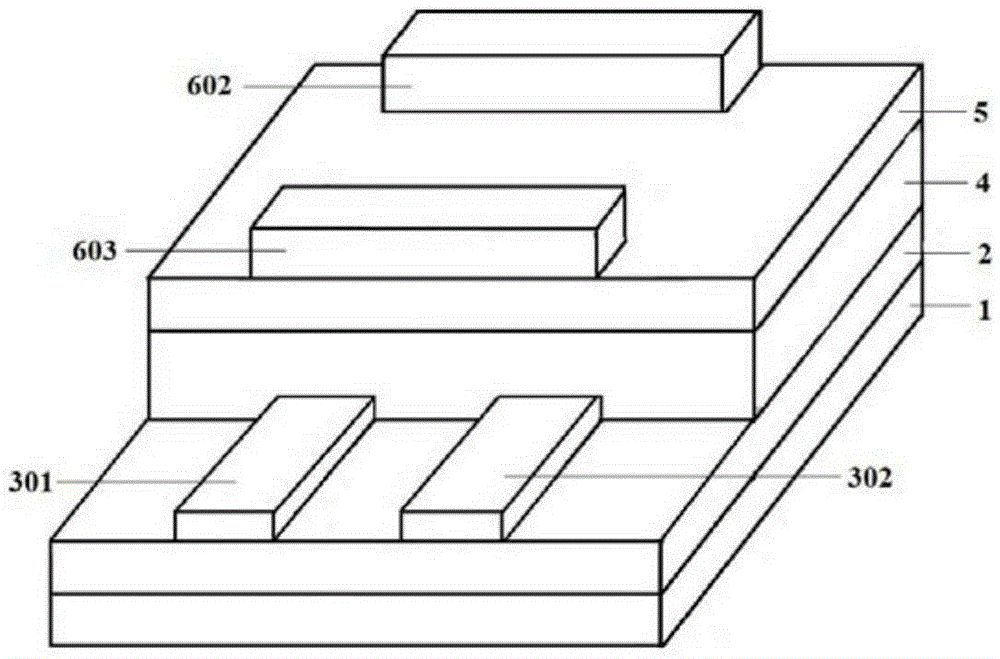

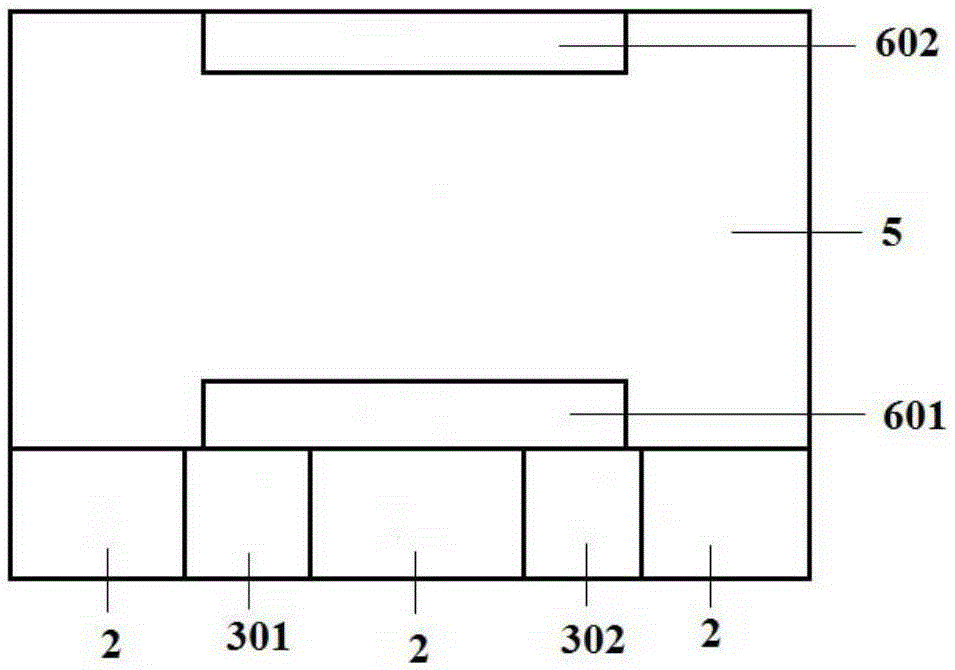

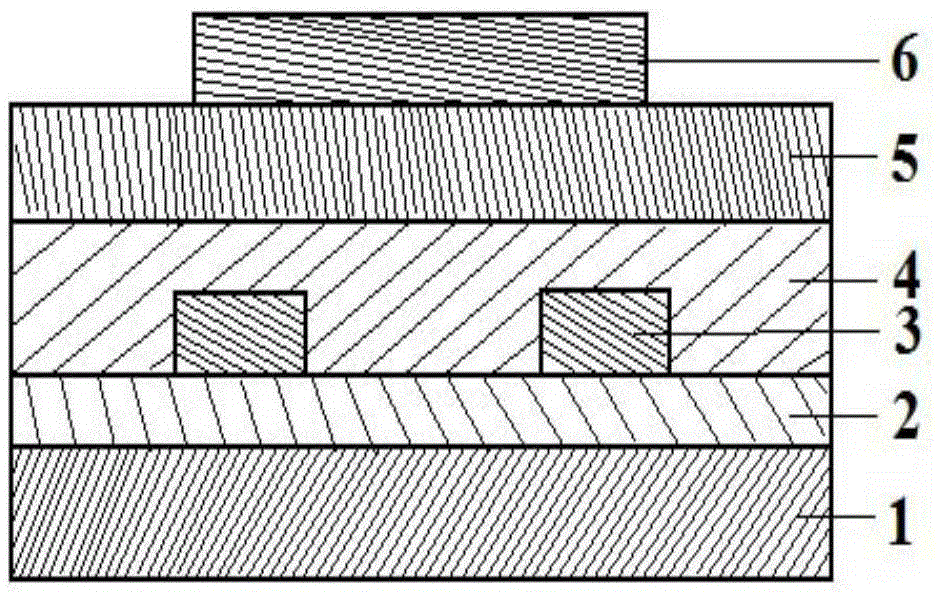

[0034] The planar separation dual-gate thin film transistor of this embodiment adopts a bottom-gate structure, and sequentially includes a substrate 1, a transition layer 2, a gate electrode layer 3, an insulating gate dielectric layer 4, a semiconductor active layer 5, and a source electrode / drain layer from bottom to top. Pole 6; the gate electrode layer is composed of two gate electrodes, and the two gate electrodes are arranged relatively parallel on the transition layer; the connection direction of the two gate electrodes is perpendicular to the source electrode / drain electrode connection direction, and its structure and Functionally equivalent; the source / drain electrodes are relatively parallel.

[0035] The substrate in this embodiment may be a glass substrate or a plastic substrate.

[0036] The semiconductor active layer in this embodiment is a 30-80 nanometer indium-doped gallium zinc oxide (IGZO) semiconductor thin film.

[0037] The insulating gate dielectric lay...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More