Method for forming gate structure and gate structure

A gate structure and gate technology, which is applied in the formation of gate structure and the field of gate structure, can solve the problems of complicated steps and the influence of CMOS device manufacturing, and achieve the effect of speeding up the process progress, reducing the influence, and easy etching

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

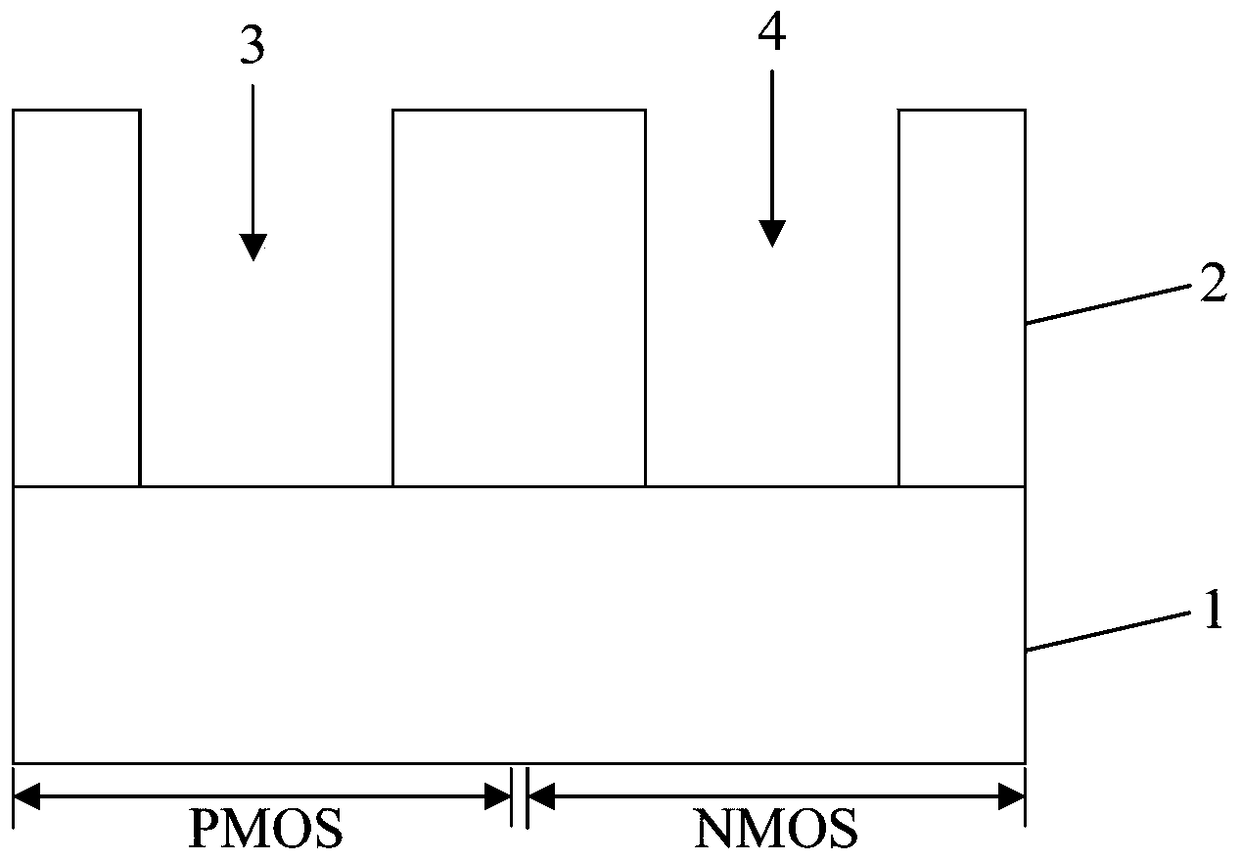

[0041] Since the properties of the PMOS device and the NMOS device are different, in the prior art, gate structures of the PMOS device and the NMOS device need to be formed separately. refer to Figure 1 to Figure 5 It is a structural schematic diagram of each step when forming a gate structure of a CMOS device in the prior art. First, refer to figure 1 A dielectric layer 2 having openings 3 and 4 is formed on the substrate 1, and the openings 3 and 4 are used to respectively form gate structures of PMOS devices and NMOS devices in subsequent steps.

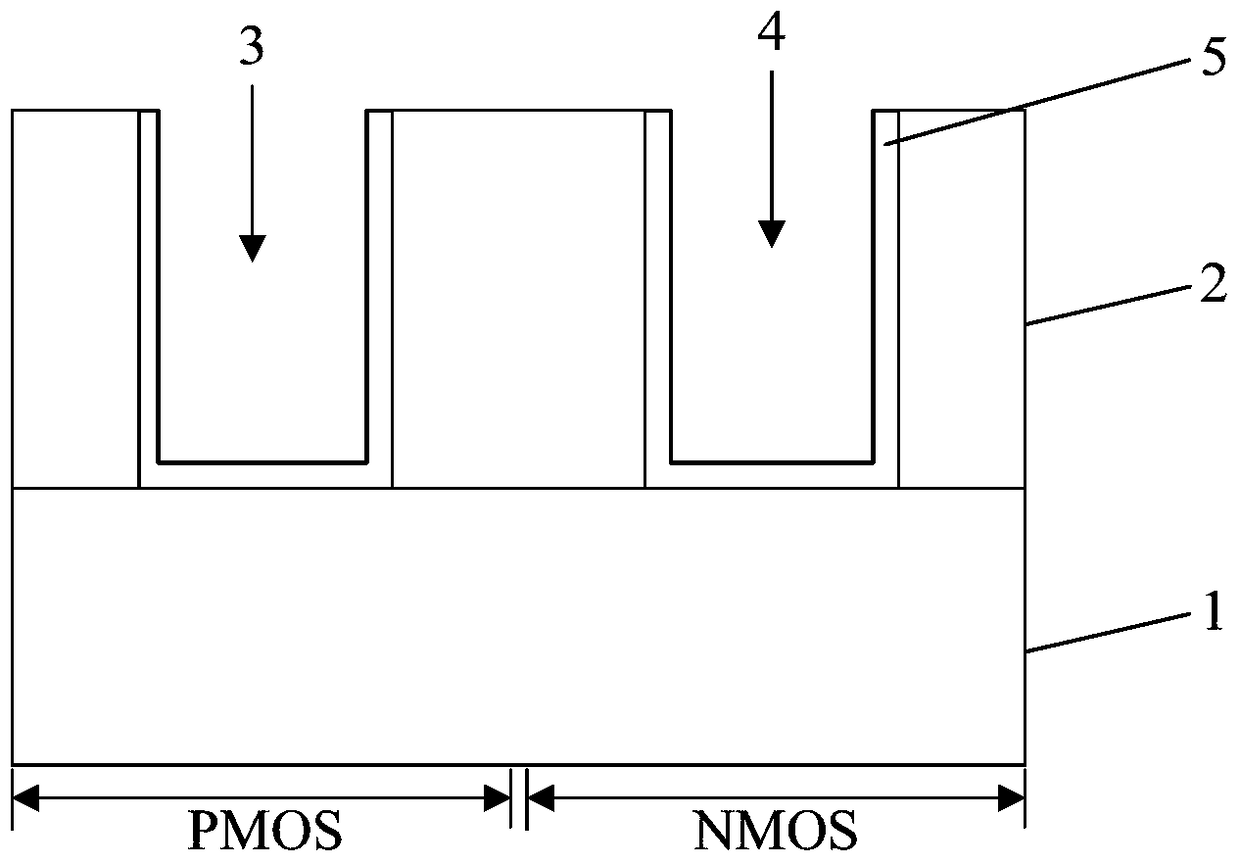

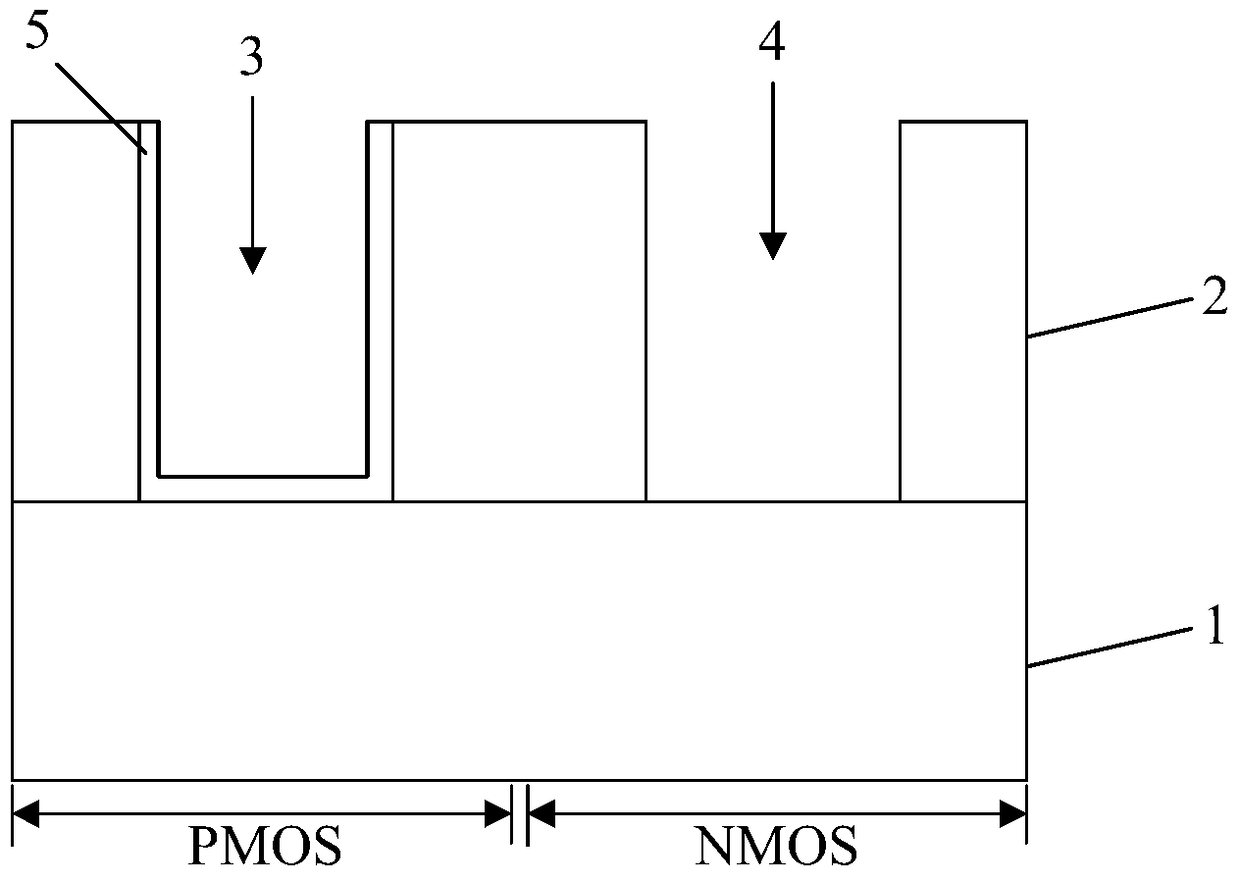

[0042] continue to refer figure 2 as well as image 3 , forming a PMOS work function layer 5 in the openings 3 and 4, and then removing part of the PMOS work function layer 5, leaving only the PMOS work function layer 5 in the opening 3 corresponding to the PMOS region. Specifically, in the prior art, an etching mask such as photoresist is generally formed on the PMOS work function layer 5 that needs to be preserved, and the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More