FPGA-based BCH encoding and decoding device and encoding and decoding method thereof

An encoding and decoding method and encoding and decoding technology are applied in the field of error checking and correction and verification of storage system data, and can solve the problems of fewer coded bits of error correction code data, fewer error correction bits, and random errors of storage media, etc. Achieve the effect of reducing cycle, reducing complexity and improving portability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

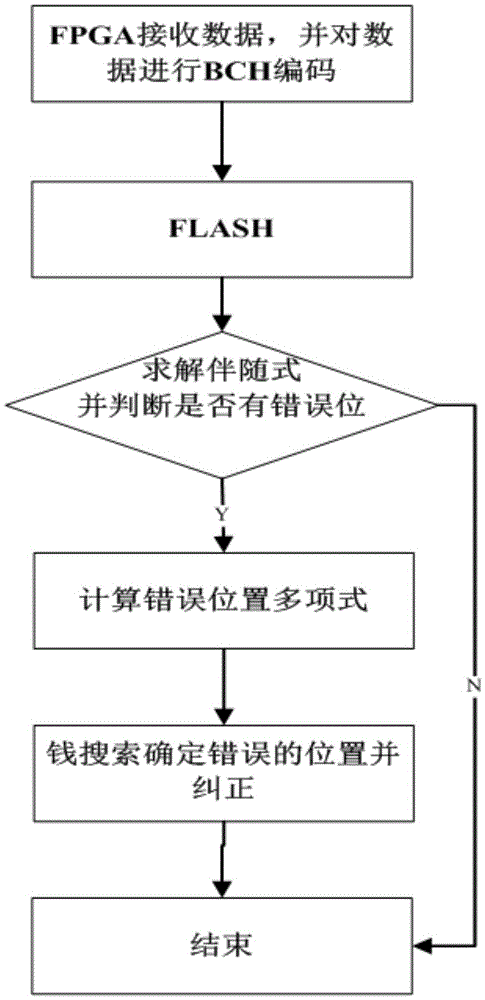

[0025] A kind of BCH codec device based on FPGA of the present invention is built on the FPGA chip, comprises: receiving module, BCH encoding module, storage module and BCH decoding module; The output end of described receiving module is connected the input of described BCH encoding module end, the output end of the BCH encoding module is connected to the input end of the storage module, and the output end of the storage module is connected to the input end of the BCH decoding module;

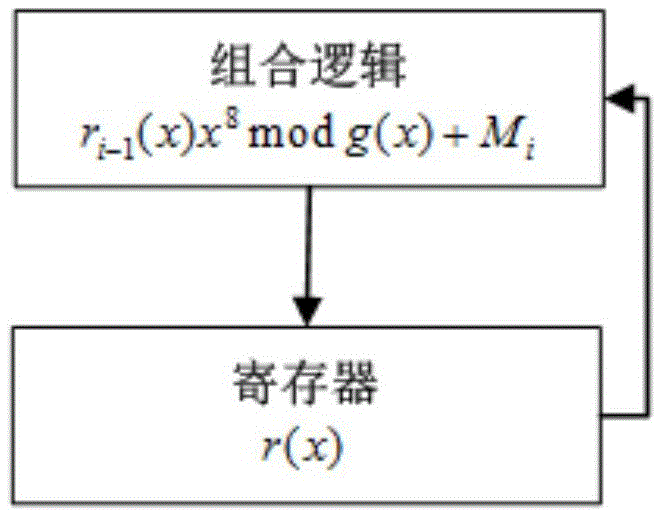

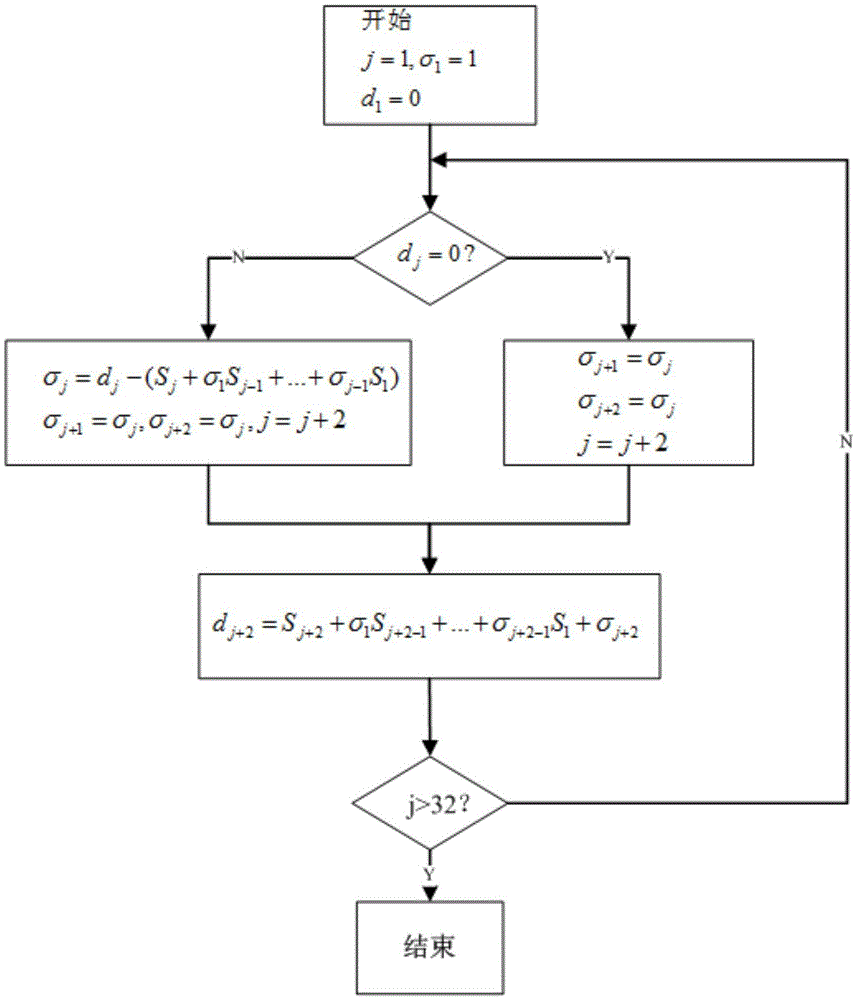

[0026] The receiving module receives the signal data, and sends the signal data to the BCH encoding module, and the BCH encoding module encodes the signal data, and sends the encoded signal data to the storage module for storage, and the BCH decoding module acquires and stores in the storage module The coded signal data in the coded signal data is then decoded to obtain the coded signal data after decoding; the present embodiment utilizes verilog language to realize BCH coding and BCH decoding r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More