How the transistor is formed

A transistor and stress layer technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as poor conductivity and large series contact resistance, and achieve enhanced conductivity, reduced series contact resistance, and reduced interface. The effect of the barrier

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] As described in the background, in prior art transistors, the quality of the metal silicide layer on the stress layer is poor and the resistance is high, and the series contact resistance at the interface between the metal silicide layer and the stress layer is relatively large, so that the conductive plug The conductivity between the source, the conductive plug and the drain is poor.

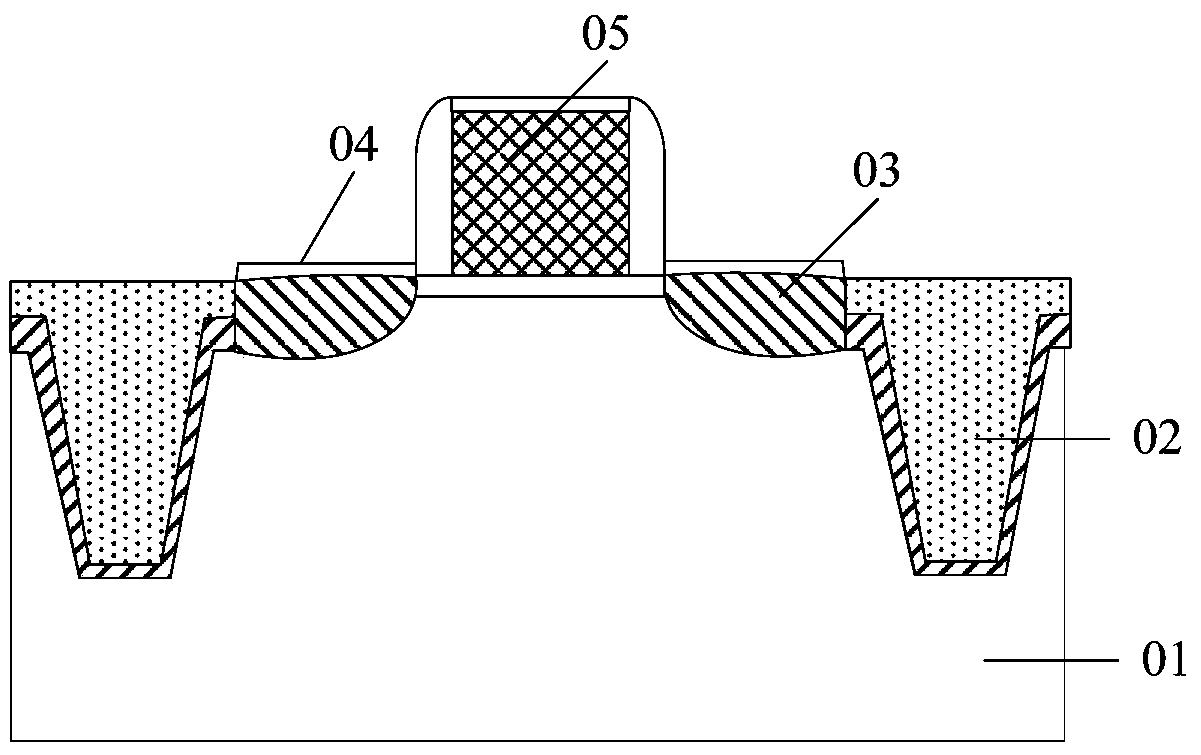

[0038] Analyze the reasons for the large series contact resistance at the interface between the metal silicide layer and the stress layer, continue to refer to figure 1 As shown, the usual method of forming the metal silicide layer 04 is to form a metal material layer on the SiC stress layer 03 and anneal the metal material layer. During the annealing process, the metal atoms in the metal material layer diffuse into the SiC stress layer Inside 03, it reacts with the silicon atoms in the SiC stress layer 03 to form a metal silicide layer 04. Due to the existence of carbon atoms in the Si...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More