Three-dimensional stackable phase change storage array device and preparation method thereof

A phase-change storage, three-dimensional stacking technology, applied in semiconductor/solid-state device manufacturing, electrical solid-state devices, semiconductor devices, etc., can solve the problems of high manufacturing cost of three-dimensional PCRAM structure, low reliability of high-density storage architecture, etc., to improve storage Density, reduce process cost, solve the effect of high density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0099] The invention provides a method for preparing a three-dimensional stacked phase-change memory array device, comprising the following steps:

[0100] Step S1 : providing a driving array; the driving array includes a plurality of discrete driving units, and the tops of the driving units are connected with first conductive pillars.

[0101] Specifically, the driving unit includes at least one of a diode, a field effect transistor and a bipolar transistor.

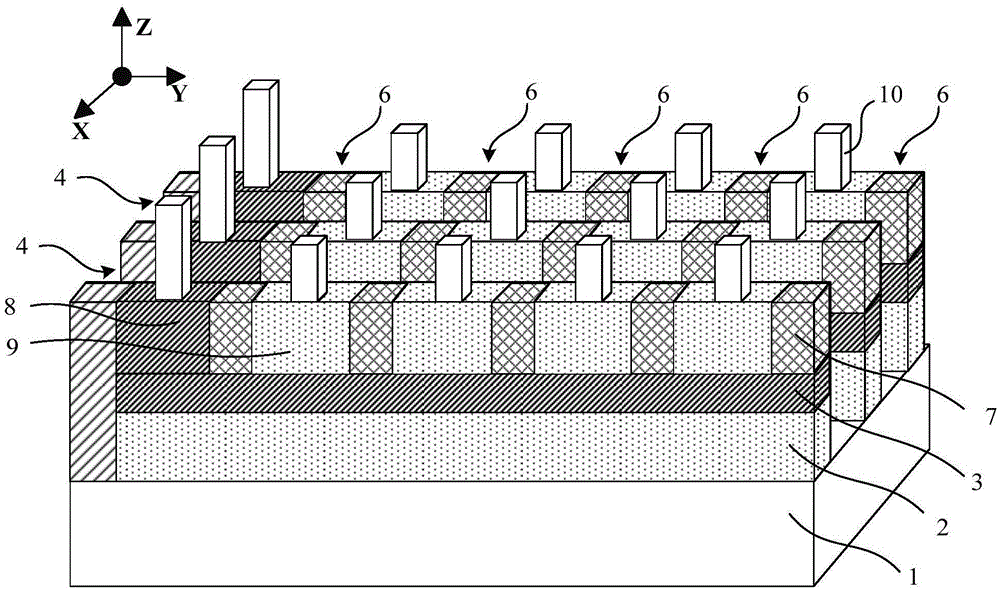

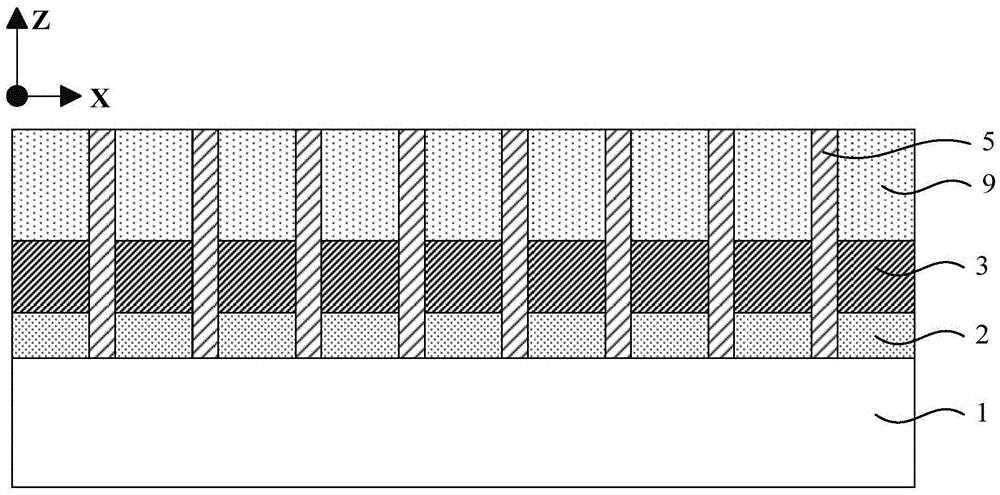

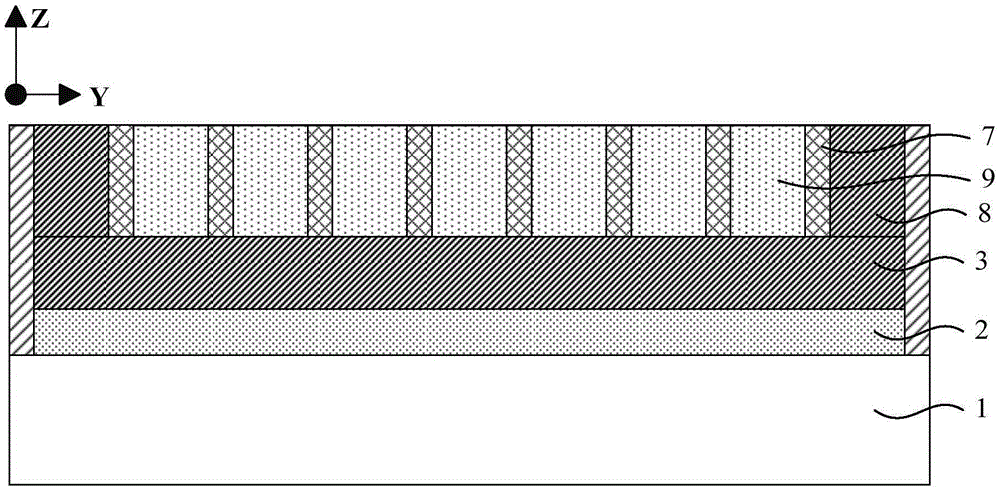

[0102] In this embodiment, the driving unit preferably adopts a diode. As an example, an X-Y-Z coordinate axis is established, wherein the X axis is parallel to the bit line direction, the Y axis is parallel to the word line direction, and the Z axis is perpendicular to the X-Y plane. see Figure 1-Figure 3 , which is a schematic diagram of a driving array. In this embodiment, the driving array preferably adopts a double shallow trench isolation epitaxial diode array structure, wherein, figure 1 It is shown as a sche...

Embodiment 2

[0140] The present invention also provides a three-dimensional stacked phase-change memory array device, please refer to Figure 10-Figure 12 ,in, Figure 12 It is shown as a perspective view of the three-dimensional stacked phase-change memory array device, Figure 10 shown as Figure 12 The Y-Z plane sectional view of the partial area of the structure shown, Figure 11 shown as Figure 12 The Z-Z plane sectional view of the partial region of the structure shown, as shown in the figure, the three-dimensional stacked phase-change memory array device includes:

[0141] A drive array; the drive array includes a number of discrete drive units, the top of which is connected to a first conductive column 10;

[0142] A plurality of multi-layer grid strip structures formed above the driving array and parallel to the direction of the word lines; the multi-layer grid strip structure includes at least two layers of gate material layers 11, and the adjacent two layers of gate mater...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More