Transverse SOI power LDMOS

A lateral and power technology, applied in electrical components, circuits, semiconductor devices, etc., can solve the problems of charge imbalance sensitivity, substrate auxiliary depletion, device breakdown voltage drop, etc., to reduce on-resistance, reduce channel Channel resistance, drift region resistance, and on-resistance reduction effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

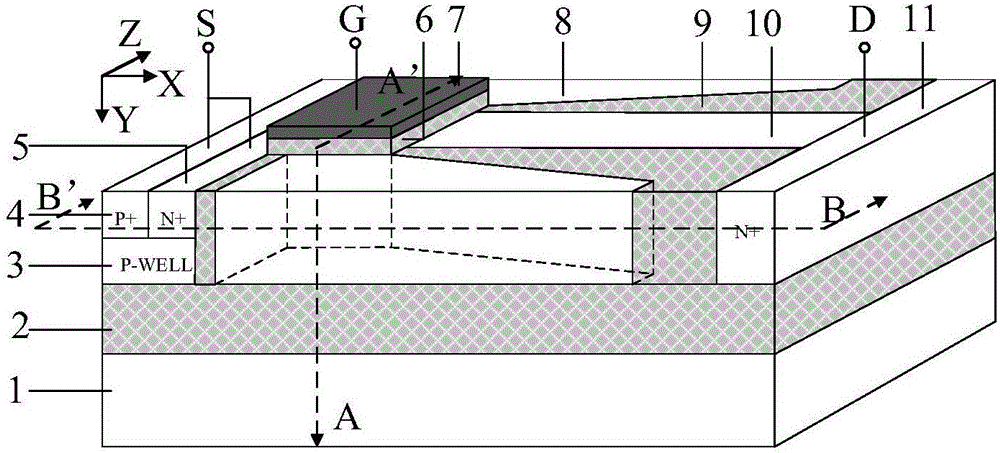

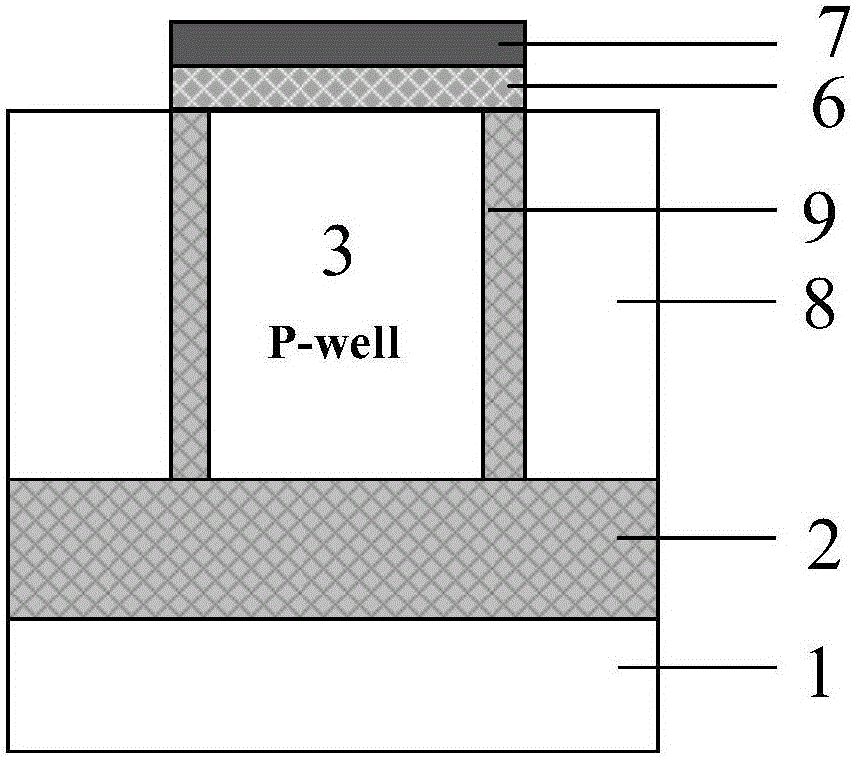

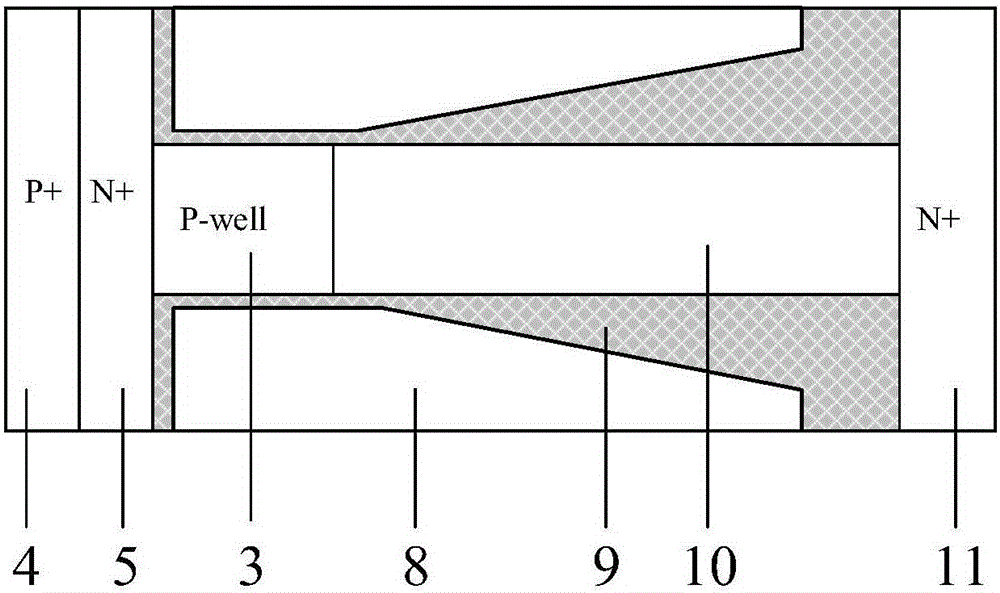

[0031] Such as figure 1As shown, the structure of this example includes a substrate layer 1 and a dielectric buried layer 2 positioned on the upper surface of the substrate layer 1; one end of the upper surface of the dielectric buried layer 2 has a P-type semiconductor body region 3, and the other end of the dielectric buried layer 2 upper surface One end has an N-type semiconductor drain region 11; the upper surface of the dielectric buried layer 2 between the P-type semiconductor body region 3 and the N-type semiconductor drain region 11 has a drift region 10; the upper surface of the P-type semiconductor body region 3 is far away from the drift region One side of 10 has a P-type semiconductor heavily doped contact region 4 and an N-type semiconductor heavily doped source region 5, the P-type semiconductor heavily doped contact region 4 and the N-type semiconductor heavily doped source region 5 are independent of each other and the N-type semiconductor The heavily doped sou...

Embodiment 2

[0035] Such as Figure 4 As shown, compared with Embodiment 1, the composite gate structure of this embodiment extends to the drift region in a stepped shape. It is beneficial to reduce the process difficulty of the composite groove structure.

Embodiment 3

[0037] Such as Figure 5 As shown, compared with Embodiment 1, the drift region 10 of this example is not uniformly doped, and its doping concentration gradually increases from source to drain. The structure of variable doping in the drift region is beneficial to improve the withstand voltage of the device.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com