Multi-core multi-threaded processor with precise performance control function

A multi-threaded processor and thread processing technology, which is applied in the direction of program control design, multi-program device, electrical digital data processing, etc., can solve the problem of difficult monitoring and management of the actual running status of multi-core multi-threaded processor chips, lack of monitoring and Control mechanisms and methods, lack of system-level collaborative design, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

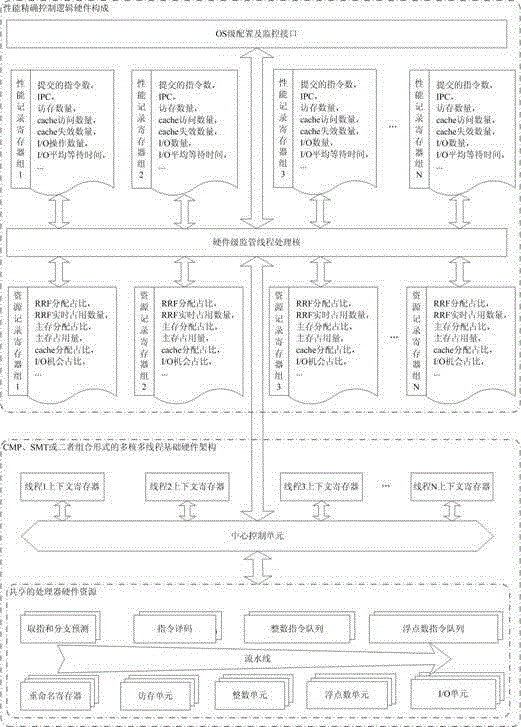

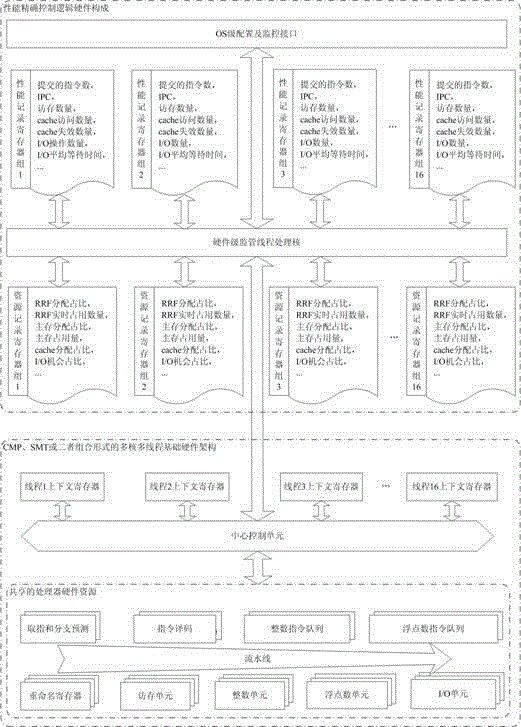

[0020] figure 1 It is a logic block diagram of a multi-core multi-thread processor whose performance can be accurately controlled by N threads. Its structure includes two parts and a general interconnection bus between them: 1) The logic part of precise performance control, specifically including N performance record register groups, resources N recording register sets, 1 hardware-level supervision thread processing core, 1 OS-level configuration and monitoring interface, and a general bus connection running through each component; 2) Multi-core and multi-thread basic hardware architecture in the form of CMP, SMT or a combination of the two Part, as the basic operating environment of multi-thread parallelism, includes the context registers of N threads, the central control unit, and shared hardware processing logic, wherein the shared hardware processing logic includes instruction fetching and branch prediction, instruction decoding, integer instruction queue, Floating-point n...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com