Method for optimizing finite difference algorithm in heterogeneous many-core framework

A technology of finite difference and optimization method, applied in the field of high-performance computing, can solve the problems of limited simulation range and simulation time, and low performance of finite difference numerical algorithm, so as to reduce the generation of bubbles and speed up the execution of instructions.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

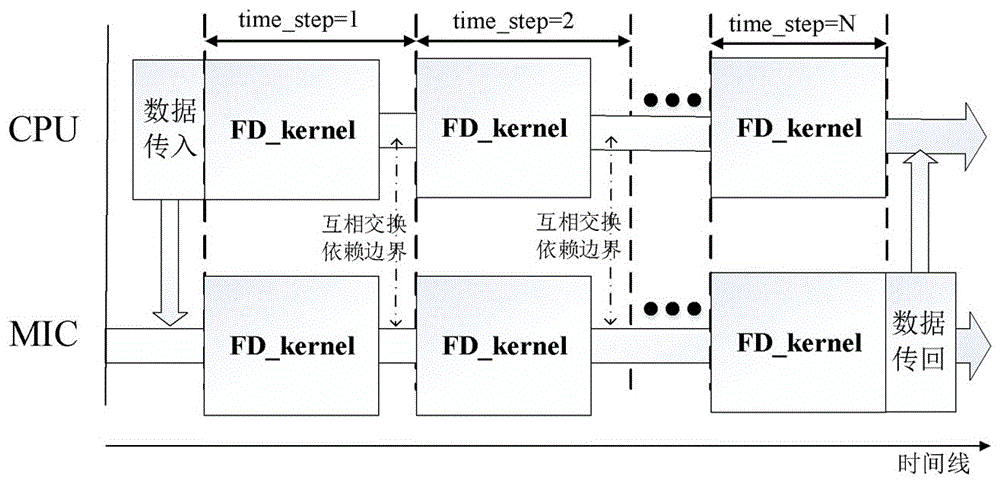

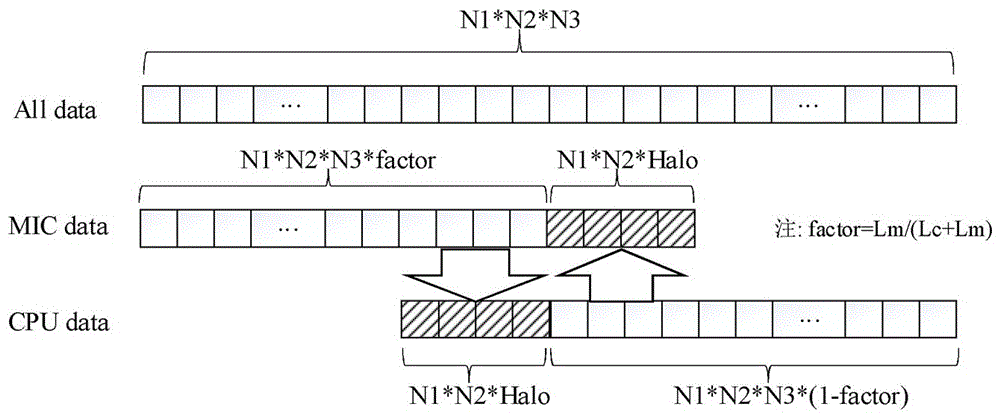

[0026] Example 1: Combining Figure 1-Figure 2 , an optimization method for a finite difference algorithm in a heterogeneous many-core architecture, the finite difference algorithm is optimized using a three-step progressive optimization method, and the specific steps of the three-step progressive optimization method are:

[0027]Step 1. Basic optimization, extracting loop invariants to reduce calculation intensity, eliminating loop branches to facilitate vectorization; specifically: reducing calculation intensity through loop expansion and invariant extraction basic optimization methods, changing initial values of loop variables and exit conditions to eliminate branches judge.

[0028] Step 2. Parallel optimization, using the OpenMP parallel model, by adding pragmas before the core loop to achieve thread-level parallelism, using built-in vector instructions to rewrite the core loop to achieve instruction-level parallelism; specifically: after the loop is divided into blocks...

specific Embodiment 2

[0035] Specific embodiment 2: combine Figure 1-Figure 2 , see figure 1 , figure 2 , the finite-difference numerical algorithm optimization method in the heterogeneous many-core system of the present invention, in the hybrid heterogeneous high-performance computer system based on the combination of many-core accelerator (MIC) and multi-core general-purpose processor (CPU), by transforming the initial value of the loop variable And the exit condition eliminates the branch judgment, because when the processor processes the conditional branch, the branch prediction logic unit will use a statistical method to predict the calculation result before the calculation result is available. Once the branch prediction error occurs, the instruction pipeline will return to the The branch position generates pipeline bubbles, resulting in waste of clock cycles. In addition, after the branch prediction fails, the compiler cannot continue to perform subsequent optimizations such as loop unrol...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More