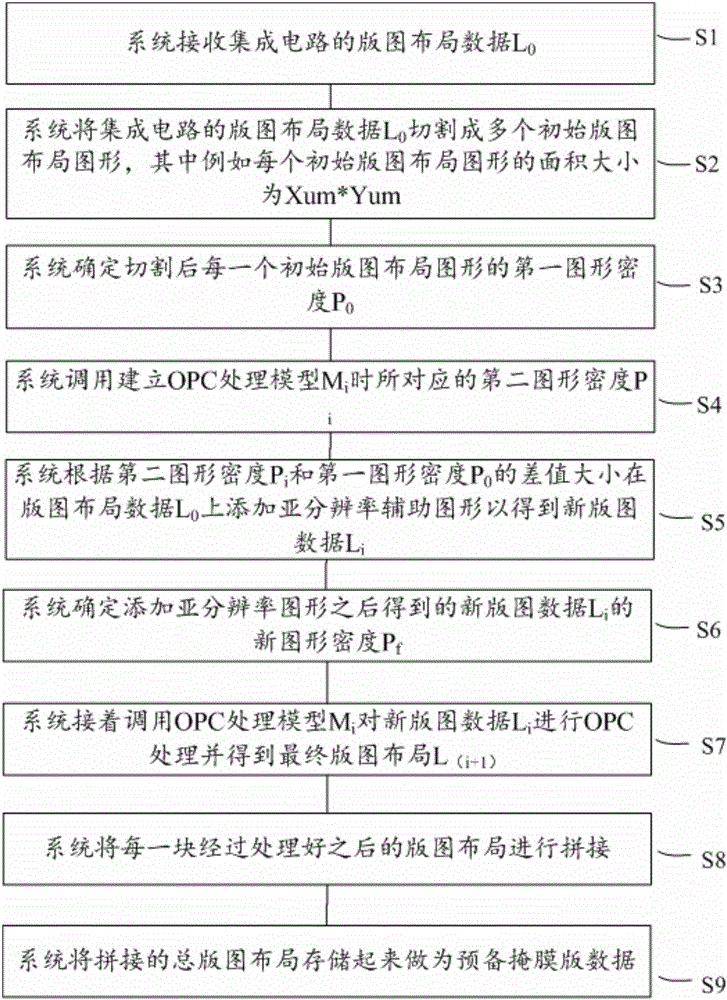

Method for layout OPC (optical proximity correction)

A technology for layout and layout data, applied in the field of layout OPC processing, can solve problems such as affecting device performance, weakening OPC processing effect, yield loss, etc., to achieve the effect of improving fitting degree, increasing layout processing time, and improving processing capacity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] In order to make the content of the present invention clearer and easier to understand, the content of the present invention will be described in detail below in conjunction with specific embodiments and accompanying drawings.

[0040] For all stages of integrated circuits from design to manufacturing, the idea of using EDA software is generally used to realize the product. Once the design plan is determined, subsequent tape-out is required to verify the various functions of the design. The verification process includes silicon wafer manufacturing and integration. Circuit processing, packaging, testing and assembly to produce the final product.

[0041] The general process of using EDA software to aid design in integrated circuit design generally includes the following steps:

[0042] System design: EDA software can be used to describe the functions that the designer wants to achieve.

[0043] Logic design and function verification: Designers can use EDA software to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com