Digital low-level control processor capable of flexibly configuring clock frequency

A technology for controlling processor and clock frequency, applied in automatic power control, electrical digital data processing, instruments, etc., can solve the problems of high price, single function curing, low energy dissipation, etc., to improve anti-interference ability and improve signal The effect of transmitting quality and ensuring welding quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] According to the attached Figure 1-7 , give a preferred embodiment of the present invention, and give a detailed description, so that the functions and characteristics of the present invention can be better understood.

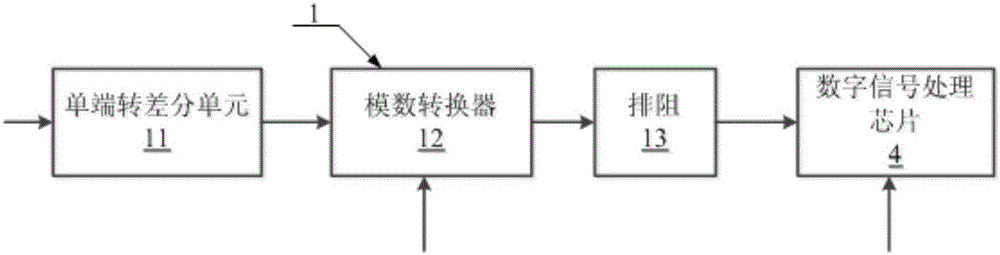

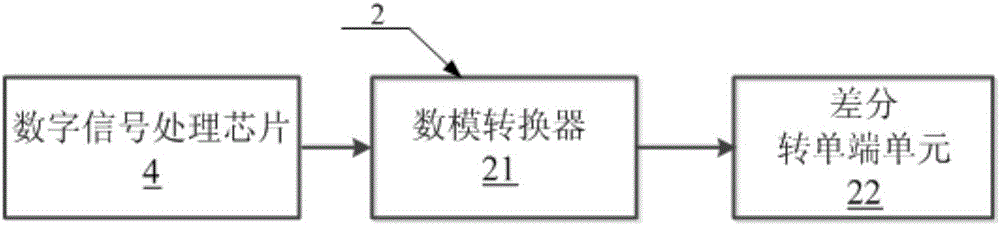

[0031] see figure 1 , a digital low-level control processor capable of flexibly configuring the clock frequency of the present invention, comprising four high-speed analog-to-digital conversion channels 1, two high-speed digital-to-analog conversion channels 2, eight digital output ports 3, and a digital signal processing chip 4 , a clock distribution system 5 and a CPCI communication interface 6, wherein the digital signal processing chip 4 is used to process the first digital signal from the high-speed analog-to-digital conversion channel 1 according to a preset low-level feedback algorithm to form a second digital signal and drive signal, and output the second digital signal to the high-speed digital-to-analog conversion channel 2, and output the d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More