Self-aligned split gate flash memory device and manufacturing method thereof

A self-aligned split-gate and flash memory device technology, applied in the field of self-aligned split-gate flash memory devices and self-aligned split-gate flash memory devices, can solve problems such as affecting the quality of the oxide layer and affecting the DR performance of the device.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

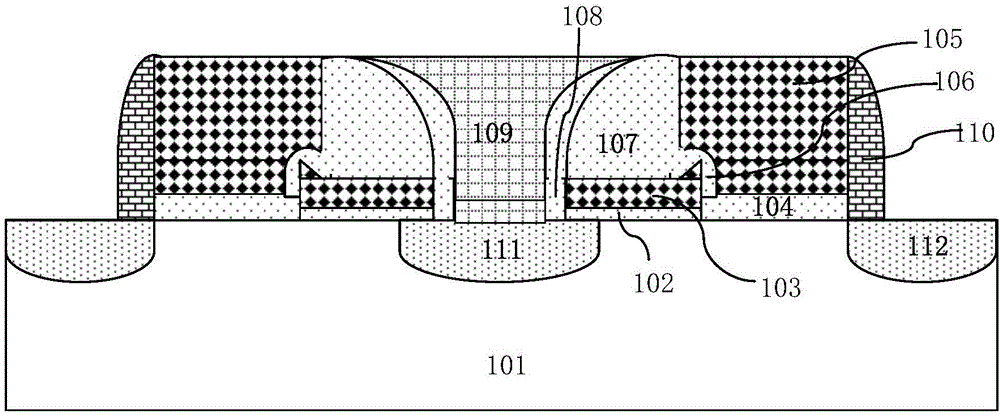

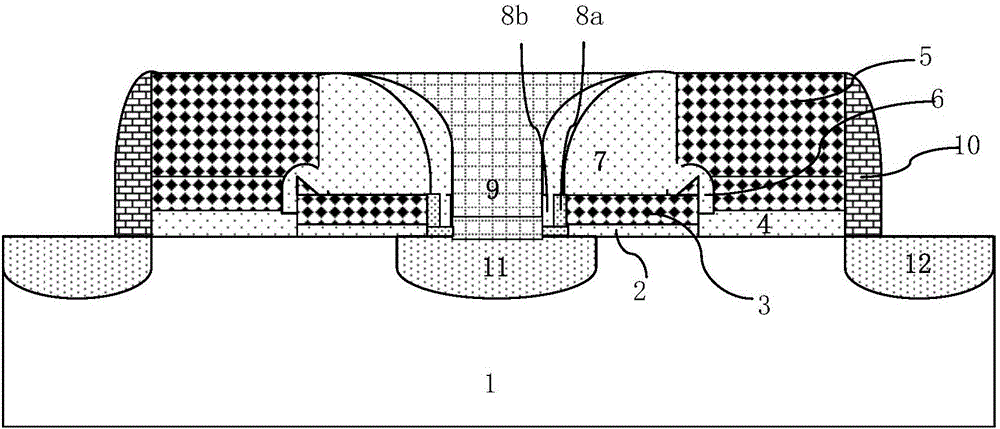

[0064] Such as figure 2 Shown is a schematic cross-sectional view of a cell structure of a self-aligned split-gate flash memory device according to an embodiment of the present invention. The cell structure of a self-aligned split-gate flash memory device according to an embodiment of the present invention includes: formed on a P-type doped semiconductor substrate such as silicon Polysilicon word line 5 , polysilicon floating gate 3 and source polysilicon 9 on substrate 1 .

[0065] The second side of the polysilicon floating gate 3 has an inclined structure with gradually increasing thickness, the thickness of the polysilicon word line 5 is greater than the thickness of the polysilicon floating gate 3, and the first side of the polysilicon word line 5 is tunneled. The oxide layer 6 covers the second side of the polysilicon floating gate 3 from the side and extends to the top of the second side of the polysilicon floating gate 3 .

[0066] The first floating gate spacer 7 co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More