Semiconductor memory and manufacturing method thereof

A manufacturing method and memory technology, which are applied in the fields of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problem of low stacking efficiency of semiconductor memory devices, difficulty in mass production, and multi-layer stacking technology. and other problems, to achieve the effect of large-capacity integration, high integration, and reducing stacking difficulty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

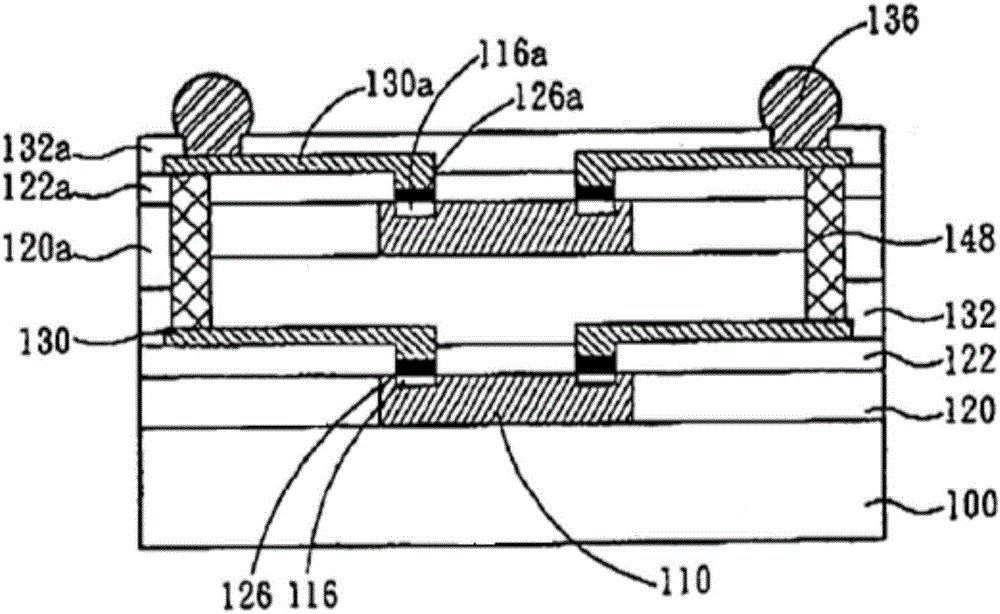

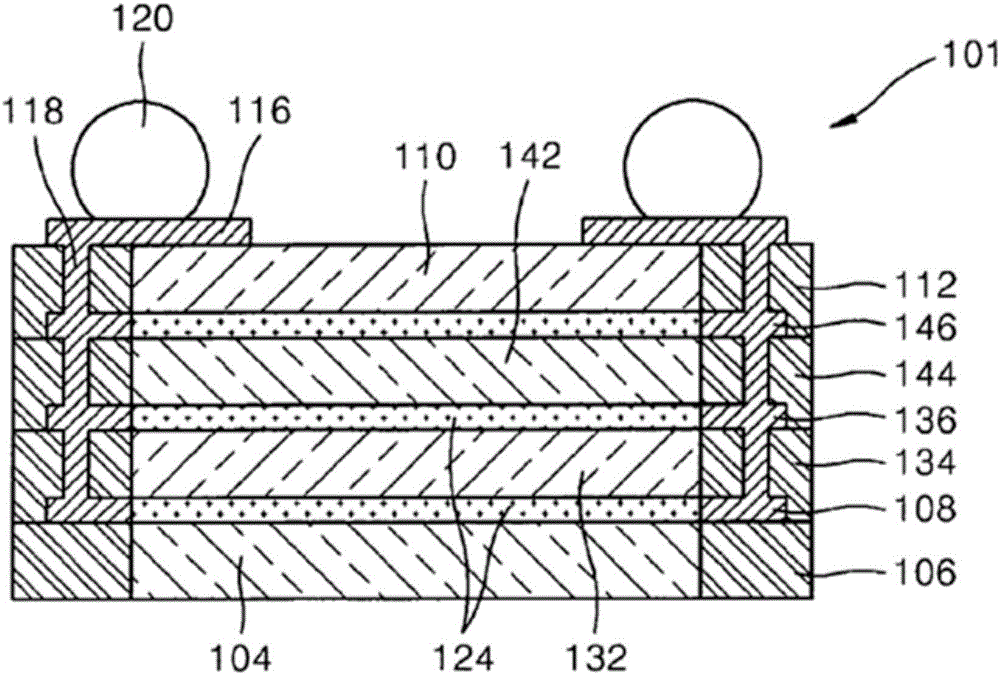

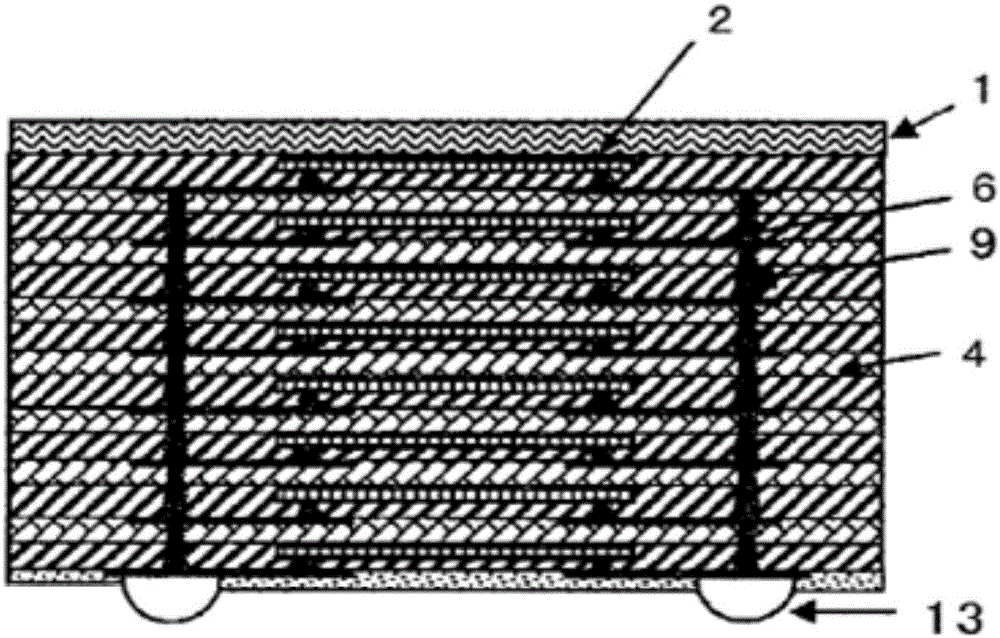

[0048] Figure 4 A schematic structural diagram of a semiconductor memory provided by an embodiment of the present invention. The semiconductor memory provided by the embodiment of the present invention can be used as a cache memory, a main memory, or a stack memory, and the like.

[0049] The semiconductor memory provided in this embodiment includes: two storage chip groups stacked sequentially from bottom to top, the redistribution layers of the two adjacent storage chip groups are electrically connected through the interlayer conductive pillars, and the memory chip located at the bottom The redistribution layer of the chipset is electrically connected to the external connection bump;

[0050] The memory chip group includes two memory chips stacked in sequence, and a composite insulating layer located under the two memory chips, the at least two memory chips are encapsulated in an integrated structure, the rewiring layer is arranged in the composite insulating layer, and th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More