Semiconductor device and manufacturing method thereof

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve problems such as limited performance improvement, small process window, and limited product yield, so as to improve performance and reduce The effect of loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

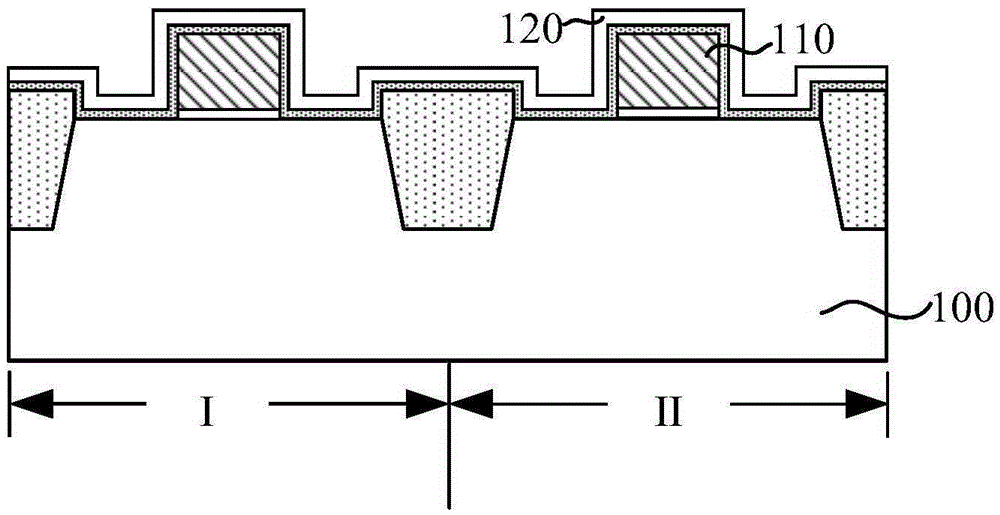

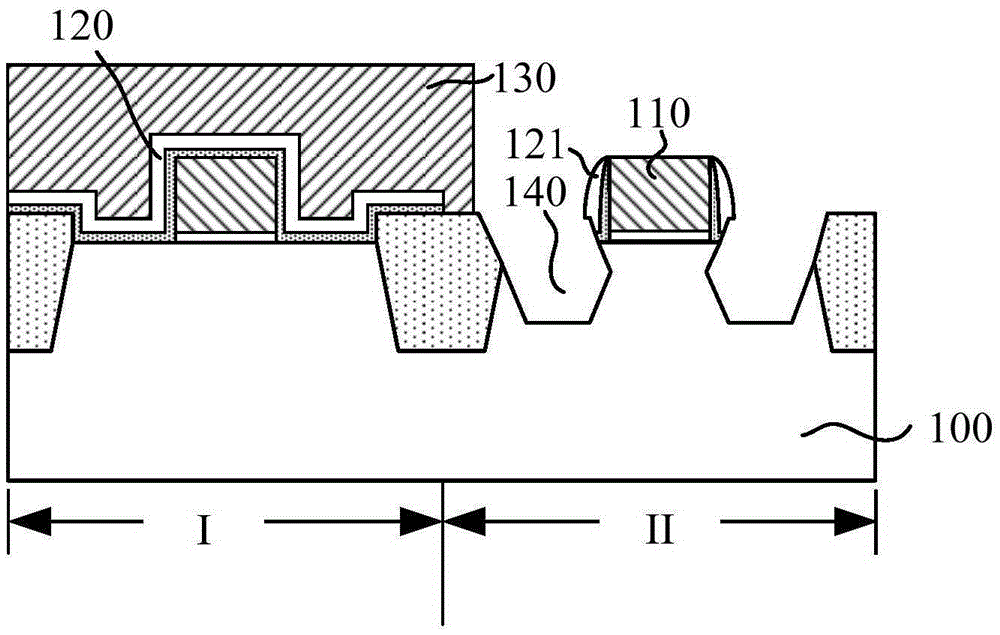

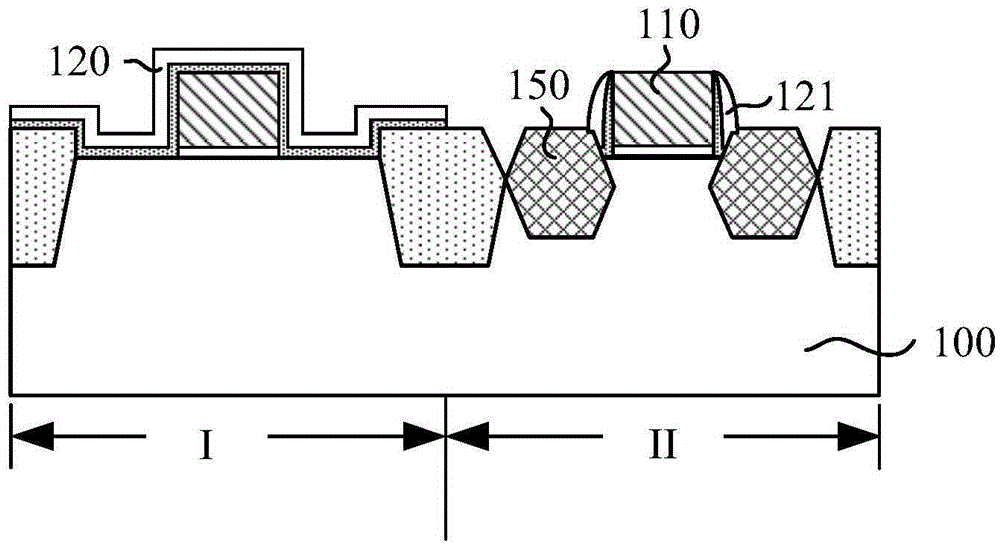

[0030] refer to Figure 1 to Figure 4 , in the prior art semiconductor manufacturing process, the formation process of the semiconductor device includes the following steps:

[0031] A semiconductor substrate 100 (such as figure 1 shown), a gate structure 110 (such as figure 1 shown), a layer of dielectric layer 120 is conformally covered on the semiconductor substrate 100 and the gate structure 110 (such as figure 1 shown); on the semiconductor substrate 100, a patterned first mask layer 130 (such as figure 2 As shown), the patterned mask layer 130 covers the NMOS region I, using the patterned mask layer 130 as a mask, through an etching process on both sides of the PMOS region II gate structure 110 A trench 140 is formed in the semiconductor substrate 100 (such as figure 2 As shown), a side wall 121 is formed on the side wall surface of the gate structure 110 of the PMOS region II, and the shape of the trench 140 is a Sigma shape; a stress layer 150 is filled in the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More