Automatic verifying platform of programmable logic block based on System Verilog

An algorithm and platform technology, applied in the field of programmable logic algorithm block automatic verification platform, to avoid changes, improve verification efficiency, and ensure independence.

- Summary

- Abstract

- Description

- Claims

- Application Information

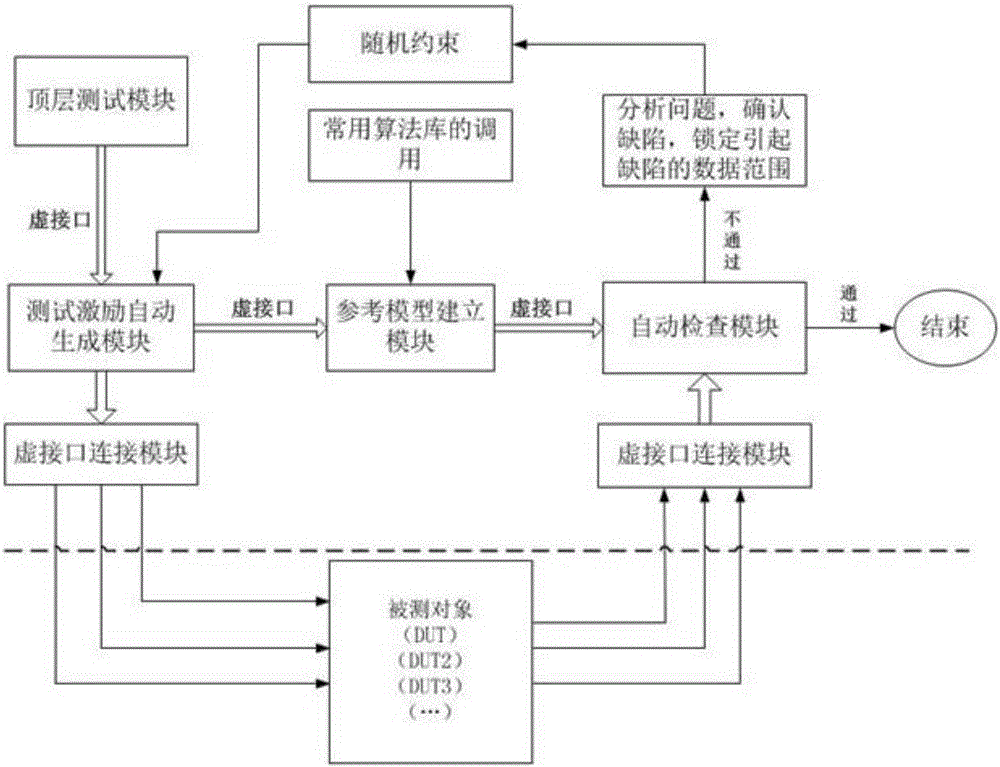

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

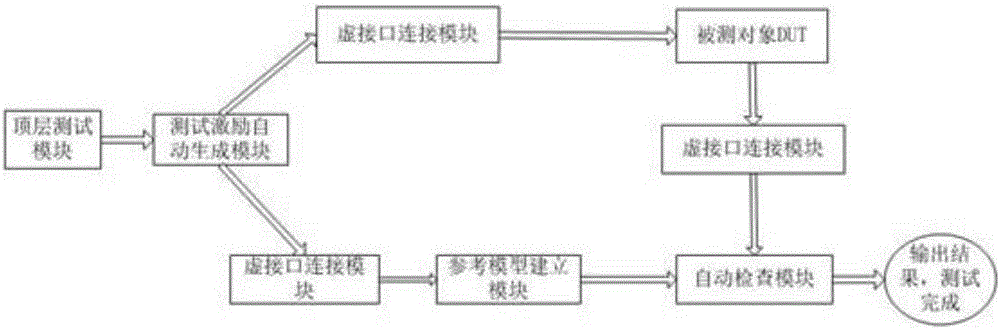

[0059] Embodiment 1: Verification of POW (power function) algorithm block

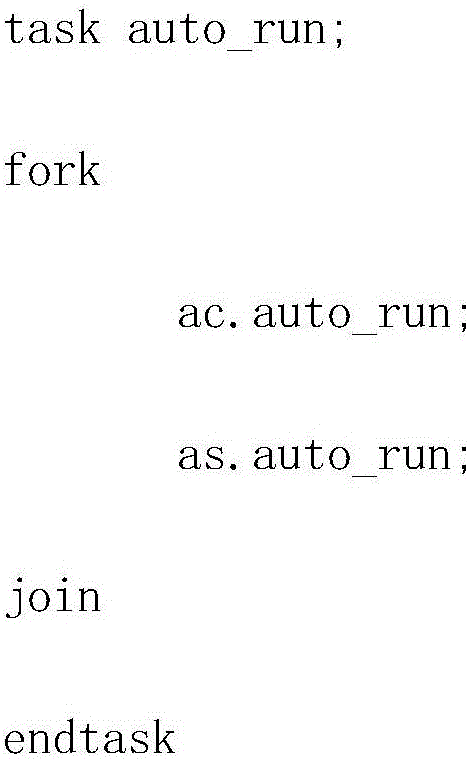

[0060] The POW algorithm block has two inputs, base and power, and one output. The three input types are in long real format. First, define the interface as real_sig_if. In the virtual interface connection module, declare the input, output, and input signals of the virtual interface type to be connected to the test stimulus automatic generation module and the automatic inspection module respectively. The output signal is connected to the automatic test stimulus module. The inspection modules are connected, and the top-level test module declares the input and output interface signals, which are respectively connected to the corresponding signals of the measured object and the virtual interface connection module. Call the test stimulus automatic generation module, which calls the random generation function randomize to generate the input data type that meets the requirements. In the reference model build...

Embodiment 2

[0061] Embodiment 2: verification of simulated manual algorithm block

[0062] The analog manual algorithm block includes 6 bool_signal type inputs, 10 real type parameter inputs and 5 bool_signal type outputs. The 6 input signals are controlled by the signal ena. When ena changes, the 6 input signals change together. According to this characteristic, create an interface declaration of bool_aman_if, including a bool type enable signal, and 6 input signals. The input signal of bool_aman_if, the actual parameter input of type real_sig_if, and the output signal of bool_sig_if are declared in the top-level test module. Call the virtual interface connection module in the top-level module to realize the connection between the interface of the object under test and the virtual interface connection module, call the test stimulus automatic generation module and the automatic inspection module, and connect the two modules through the virtual interface connection module. Call the random...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com