Ultrahigh-speed low-jitter multi-phase clock circuit

A multi-phase clock, low jitter technology, applied in electrical components, electrical pulse generation, automatic power control, etc., can solve problems such as increasing ADC noise floor, increasing ADC spurs, reducing signal-to-noise ratio, etc., to improve performance, Improve clock matching and phase channel count, reduce the effect of sample time mismatch

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0051] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

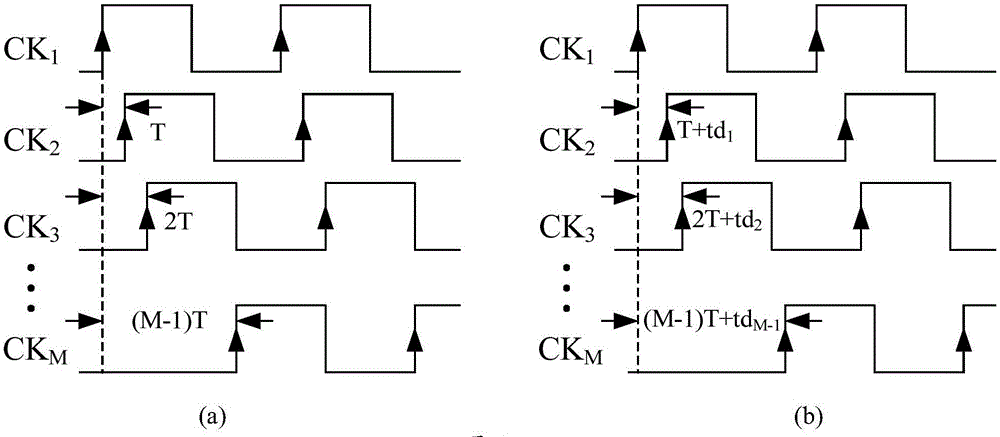

[0052] For an ultra-high-speed low-jitter multi-phase clock system, not only the clock frequency is very high, but also multiple phases are divided into one clock frequency. The time difference between two adjacent phases is already very small. The main difficulty of matching and calibration technology lies in the need The large number of calibrations (related to the number of multi-phase clocks), the calibration accuracy needs to be quite high, and the calibration process needs to be completed in the shortest possible time, all of which pose challenges to the implementation of matching calibration.

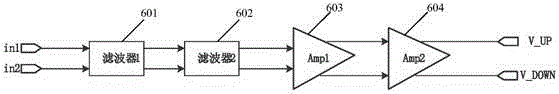

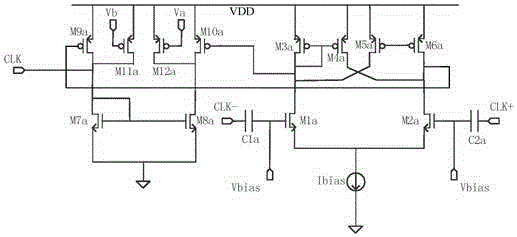

[0053] Such as figure 2 As shown, the present invention provides an ultra-high-speed low-jitter multi-phase clock circuit, which consists of an input clock recovery and duty cycle adjustment module 201, a phase detector module 202, a charge pum...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More