Semiconductor device and preparation method thereof, and electronic apparatus

A technology of electronic devices and semiconductors, applied in semiconductor devices, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as aggravated impacts

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

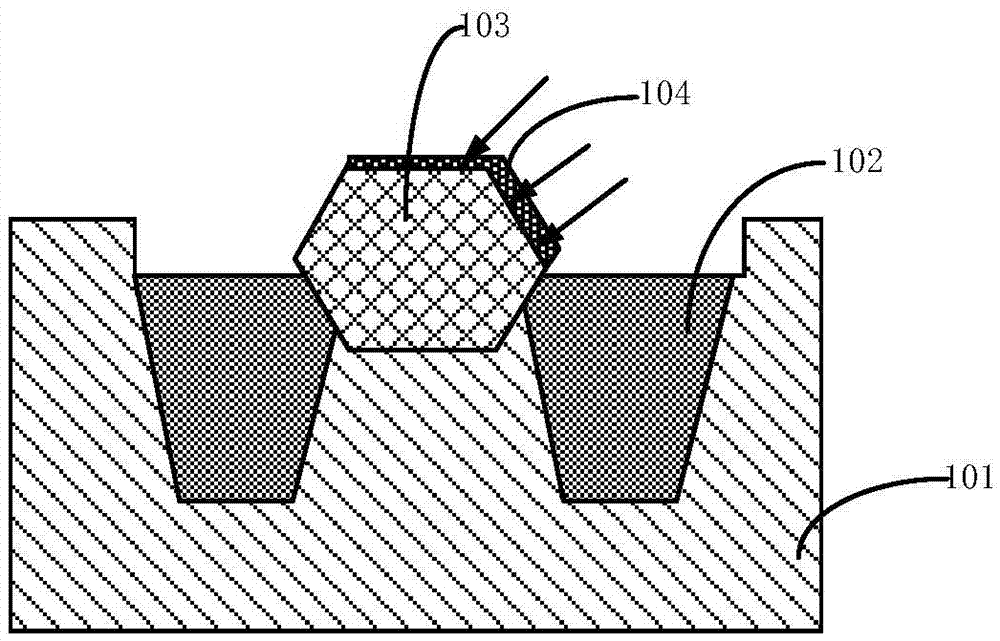

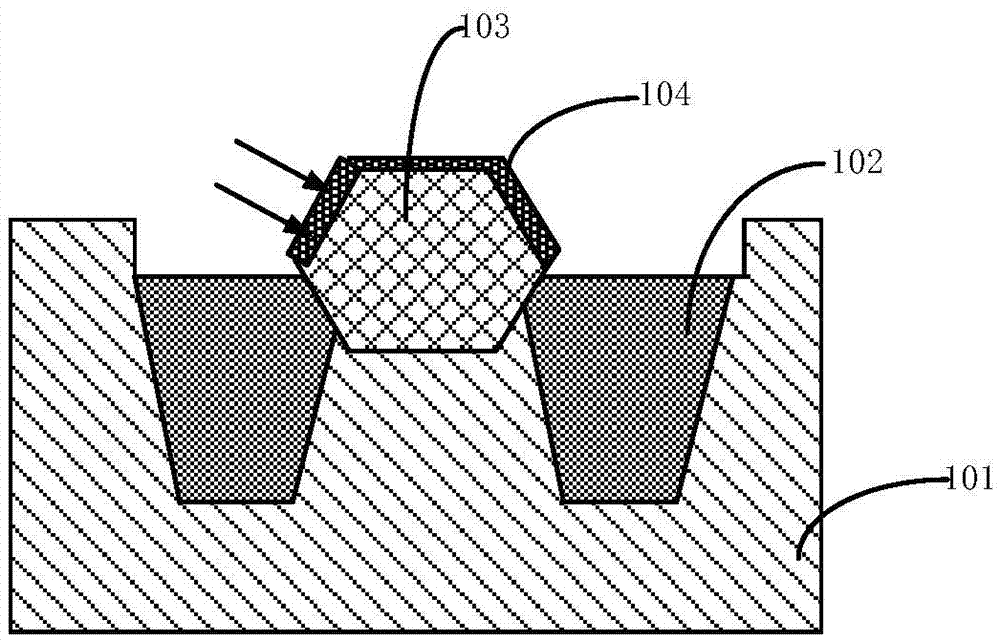

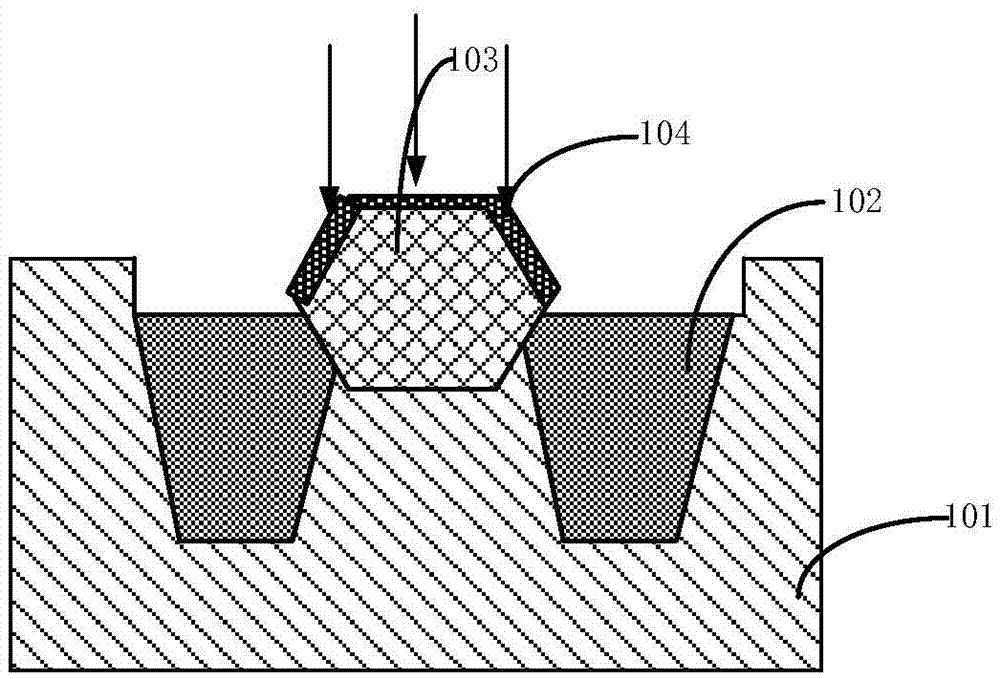

[0032] In order to solve the problems existing in the prior art in the present invention, a kind of preparation method of semiconductor device is provided, below in conjunction with attached Figures 1a-1d A specific embodiment of the present invention will be further described.

[0033] Step 101 is executed to provide a semiconductor substrate 101 on which a gate structure and Σ-shaped raised source and drain located on both sides of the gate structure are formed.

[0034] Specifically, refer to Figure 1a , a semiconductor substrate 101 is provided, and the semiconductor substrate 101 may be at least one of the materials mentioned below: silicon, silicon-on-insulator (SOI), silicon-on-insulator (SSOI), and the like.

[0035] In addition, an active region may be defined on the semiconductor substrate 101 . Other active devices may also be included on the active area, which are not marked in the shown figures for convenience.

[0036] Then a gate structure is formed on the s...

Embodiment 2

[0074] The present invention also provides a semiconductor device, which is prepared by the method described in the first embodiment. In the semiconductor device prepared by the method, an amorphous layer is formed on the inclined sidewall of the upper part of the Σ-shaped raised source and drain, which can reduce the Σ-shaped in the subsequent steps of LDD ion implantation and / or source-drain implantation. Raise the ion implantation depth at the edge of the source and drain, reduce the narrow channel effect, thereby lowering the threshold voltage and improving the performance and yield of semiconductor devices.

Embodiment 3

[0076] The present invention also provides an electronic device, including the semiconductor device described in the second embodiment. Wherein, the semiconductor device is the semiconductor device described in the second embodiment, or the semiconductor device obtained according to the preparation method described in the first embodiment.

[0077] The electronic device of this embodiment can be any electronic product or equipment such as mobile phone, tablet computer, notebook computer, netbook, game console, TV set, VCD, DVD, navigator, camera, video recorder, voice recorder, MP3, MP4, PSP, etc. , can also be any intermediate product including the semiconductor device. The electronic device according to the embodiment of the present invention has better performance due to the use of the above-mentioned semiconductor device.

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More