Built-in self-test structure of on-chip embedded Flash

A built-in self-test and embedded technology, applied in static memory, instruments, etc., can solve the problems of large hardware overhead, complex test control, large hardware overhead, etc., and achieve the effect of reducing difficulty, simple test control, and avoiding dependence

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

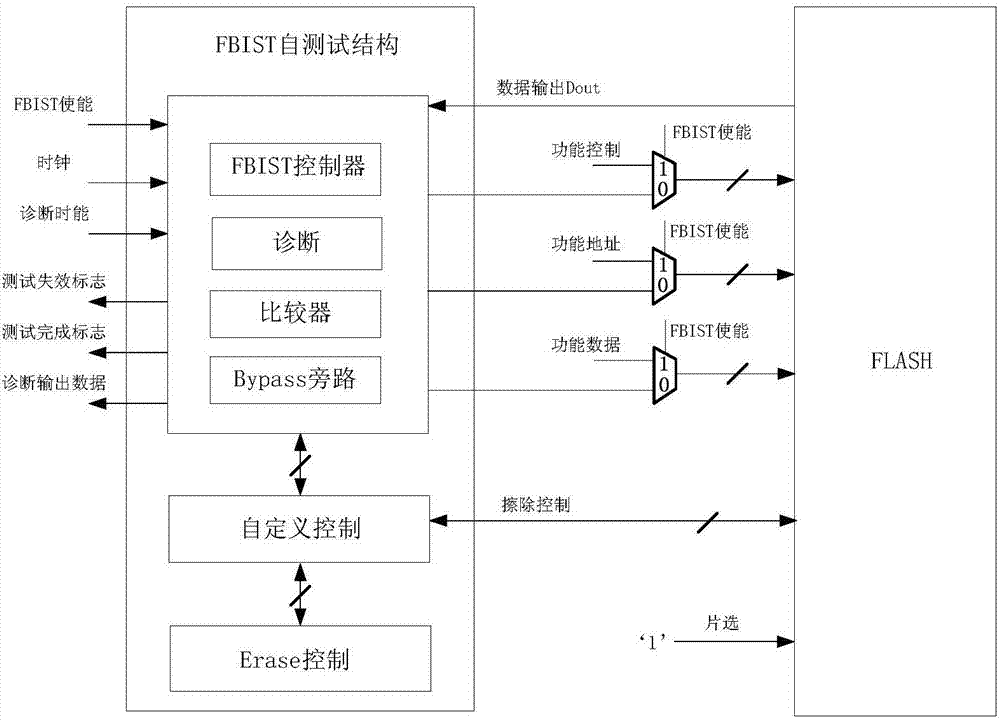

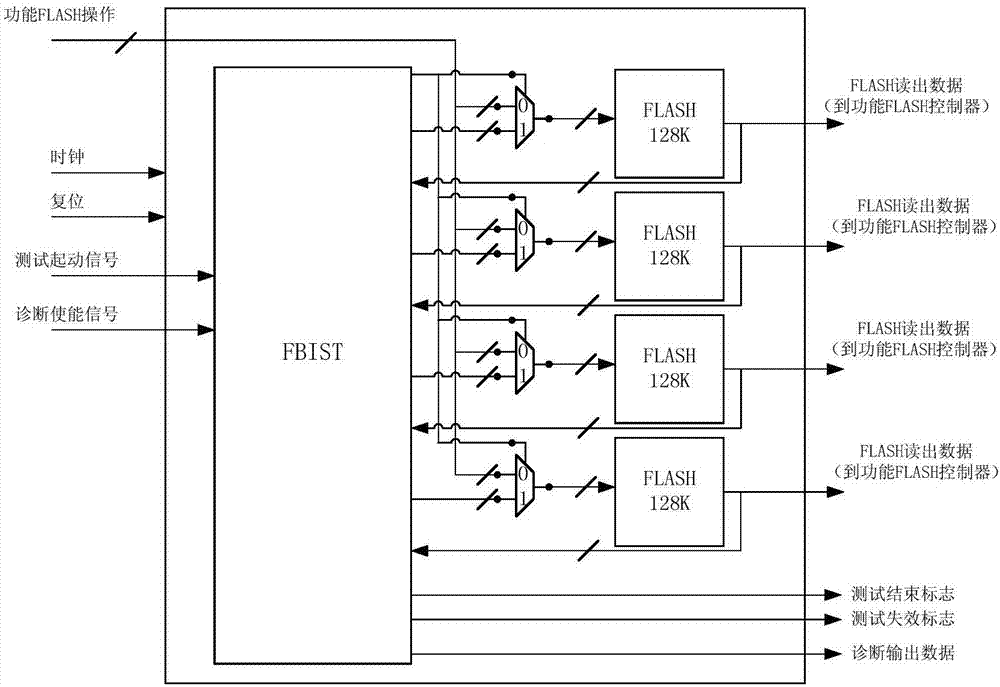

[0033] On a super-large-scale SOC chip with 0.18um process, four pieces of 128K capacity FLASH IP are integrated. This IP supports macro erase and page erase, and the function test access takes a long time and the control is relatively complicated. For the efficient testing of embedded FLASH IP in the circuit, during testability design, the on-chip embedded FLASH built-in self-test structure of the present invention is adopted, and the interface logic is as follows: image 3 shown.

[0034]In the design, considering the scale and test time of FLASH, parallel test technology is adopted. With the support of the built-in self-test structure of the present invention, four 128K FLASHs are tested in parallel, and one FBIST controller performs test control uniformly. When the FBIST circuit is enabled, the controller generates test data, addresses and control signals according to the algorithm sequence under the control of the state machine operation and the custom module, and realize...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More