Flash memory unit structure forming method

A technology of flash memory cells and shallow trenches, applied in electrical components, electrical solid devices, circuits, etc., can solve the problems of charge loss, large influence at grain boundaries, and the sharp corners of floating gates cannot be rounded, etc., to achieve high Reliability, the effect of not damaging the floating gate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

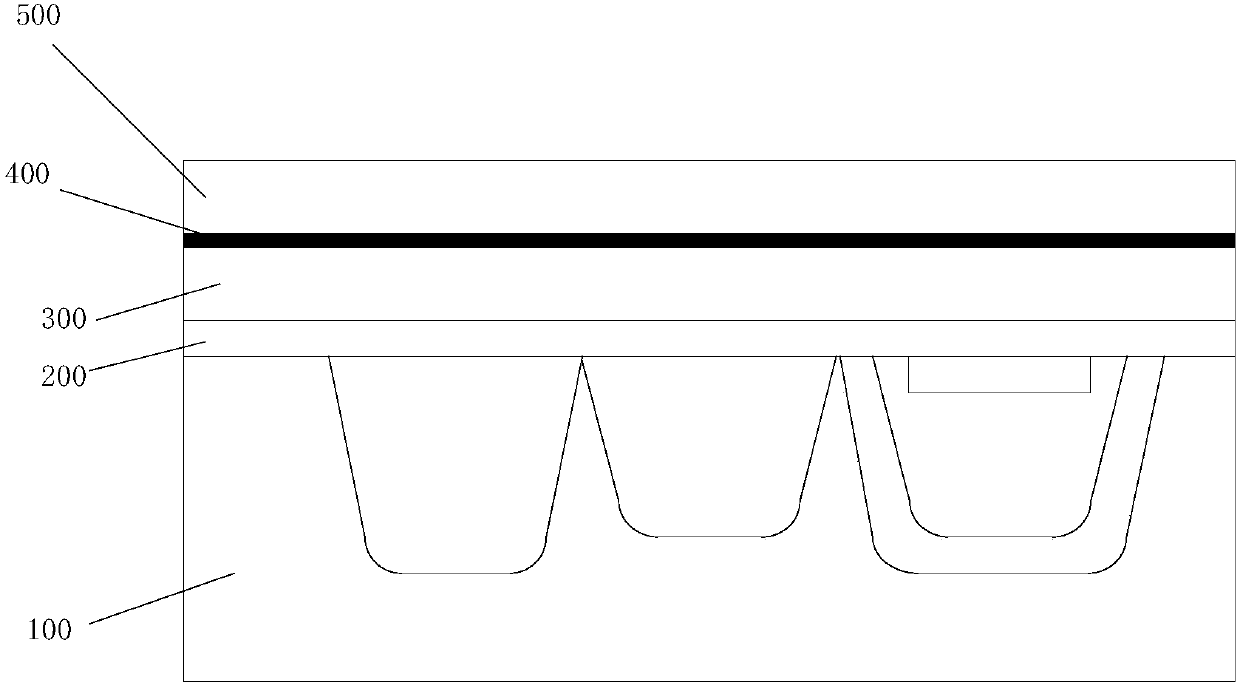

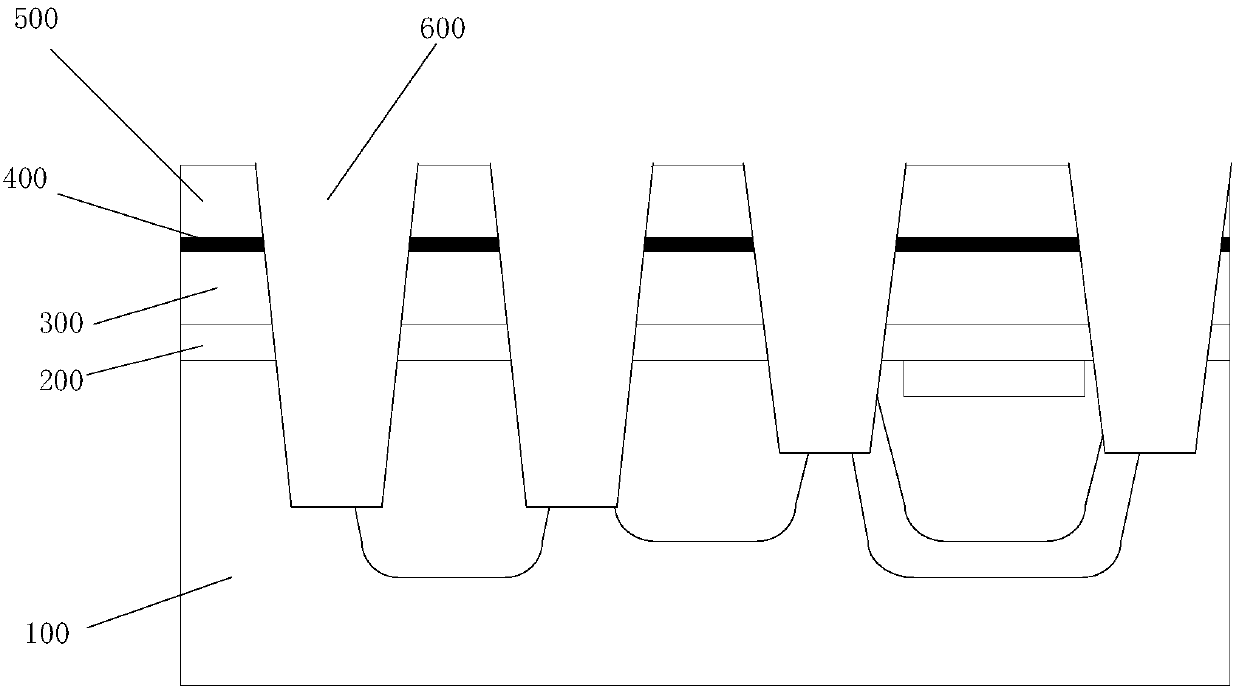

[0027] The specific embodiments of the present invention are given below in conjunction with the accompanying drawings, but the present invention is not limited to the following embodiments. Advantages and features of the present invention will be apparent from the following description and claims. It should be noted that all the drawings are in very simplified form and use imprecise ratios, which are only used for the purpose of conveniently and clearly assisting in describing the embodiments of the present invention.

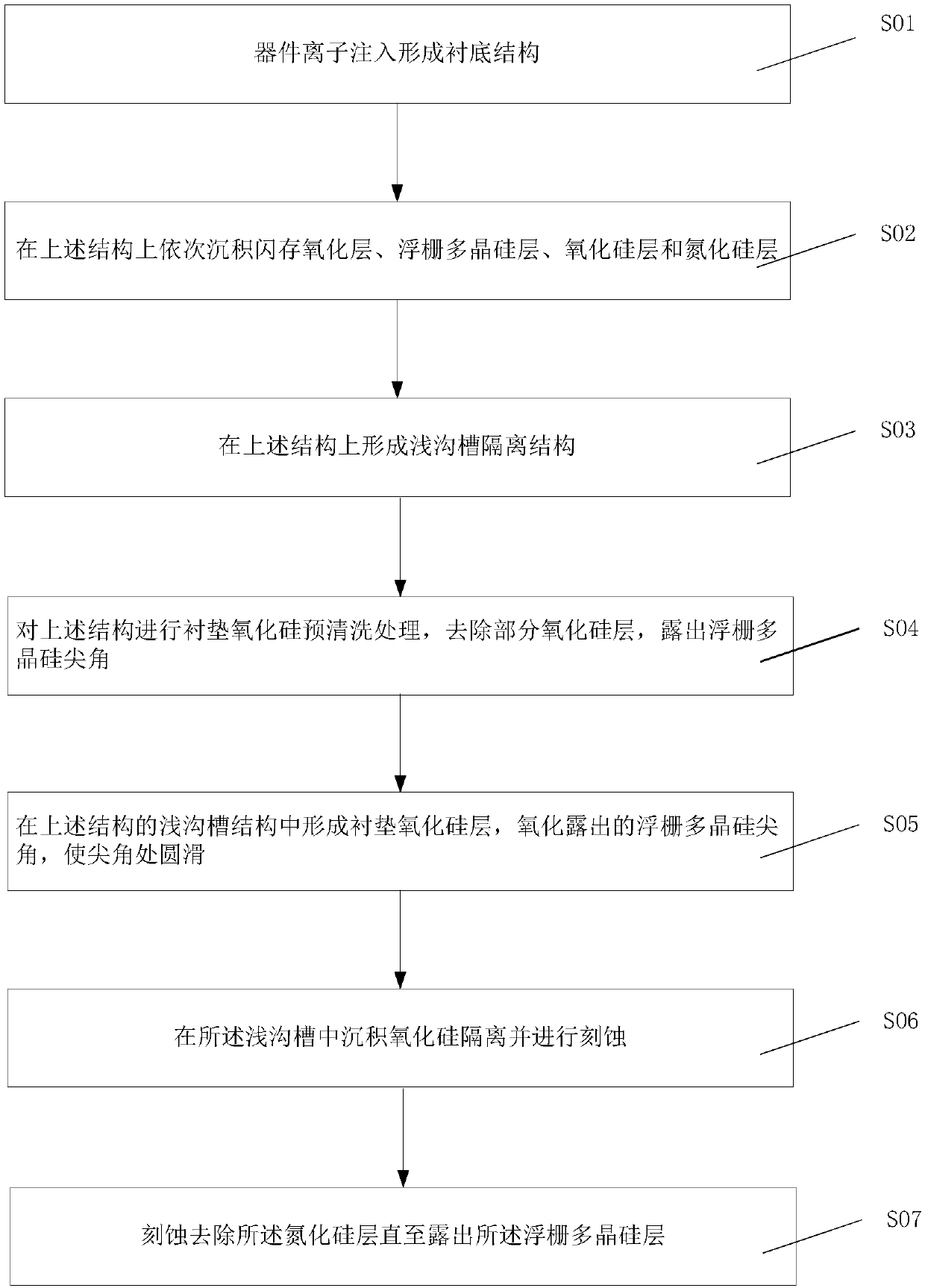

[0028] Please refer to figure 1 , figure 1 Shown is a flow chart of a method for forming a flash memory cell structure in a preferred embodiment of the present invention. The present invention proposes a method for forming a flash memory unit structure, comprising the following steps:

[0029] Step S01: device ion implantation to form a substrate structure;

[0030] Step S02: sequentially depositing a flash memory oxide layer, a floating gate polysilicon l...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap