Multi-threshold-value unit replacing method based on hierarchical processing and cluster constraint

A layered, multi-threshold technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as difficulty in adapting to the design environment, tight design cycle, and impossibility to achieve strong adaptability and portability capabilities, speed up design progress, and reduce design complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

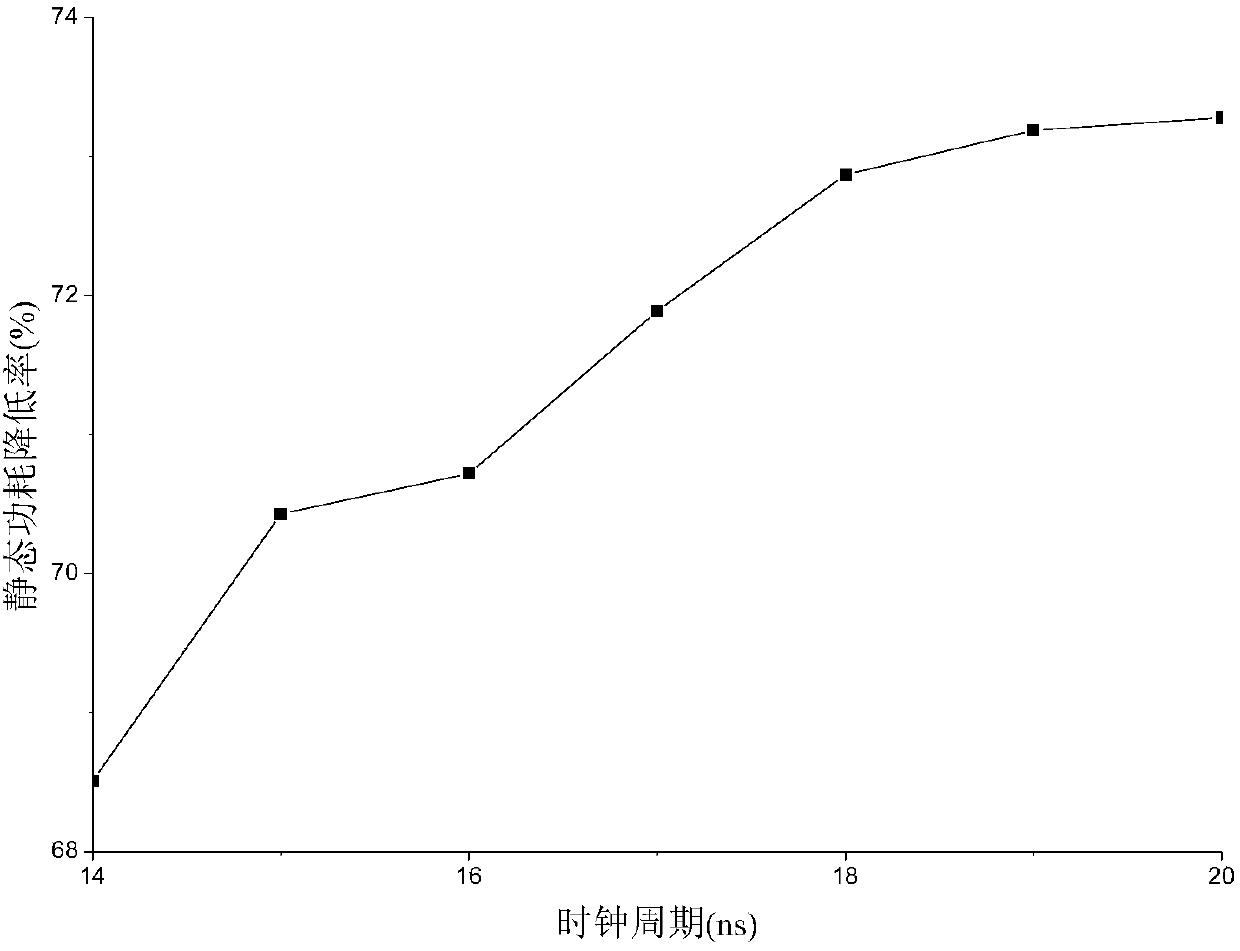

[0047] Apply the multi-threshold unit replacement method of the present invention for testing.

[0048] The multi-threshold unit replacement method of the present invention takes the open source oc8051 core as an embodiment (https: / / opencores.org / projects).

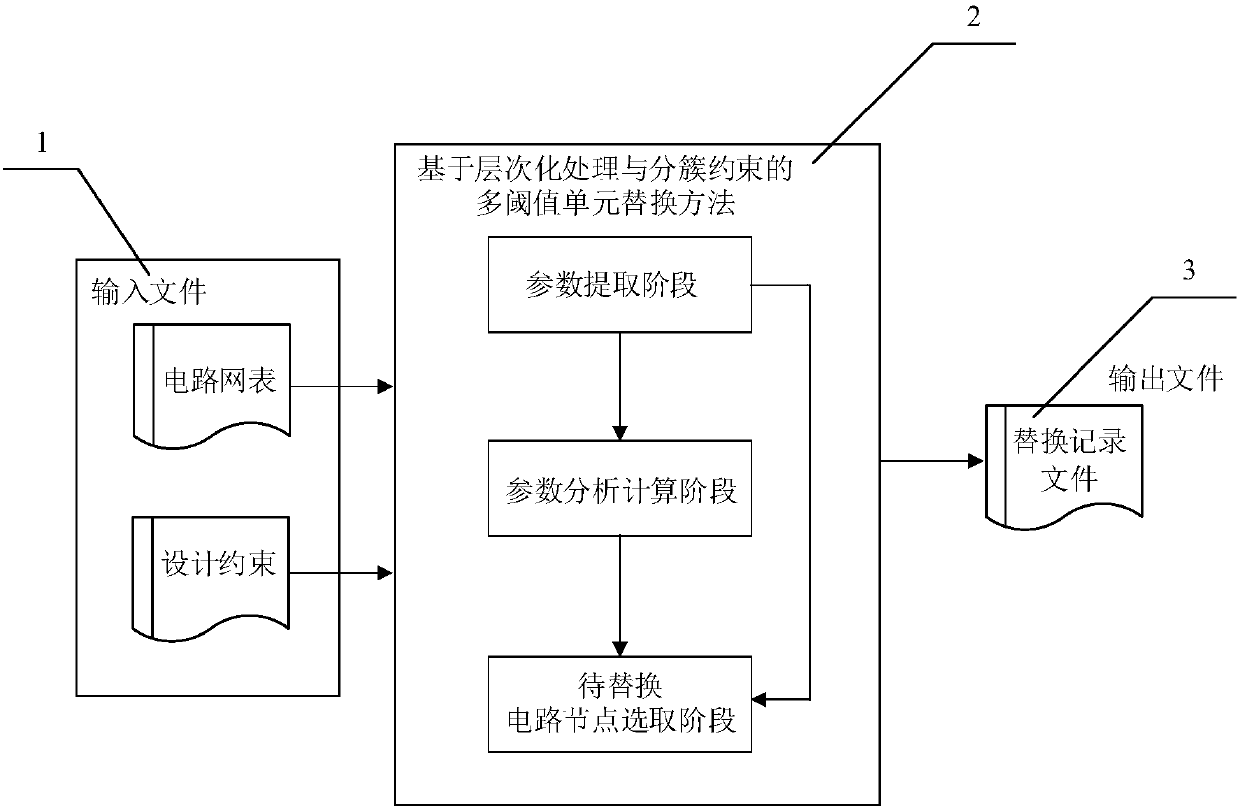

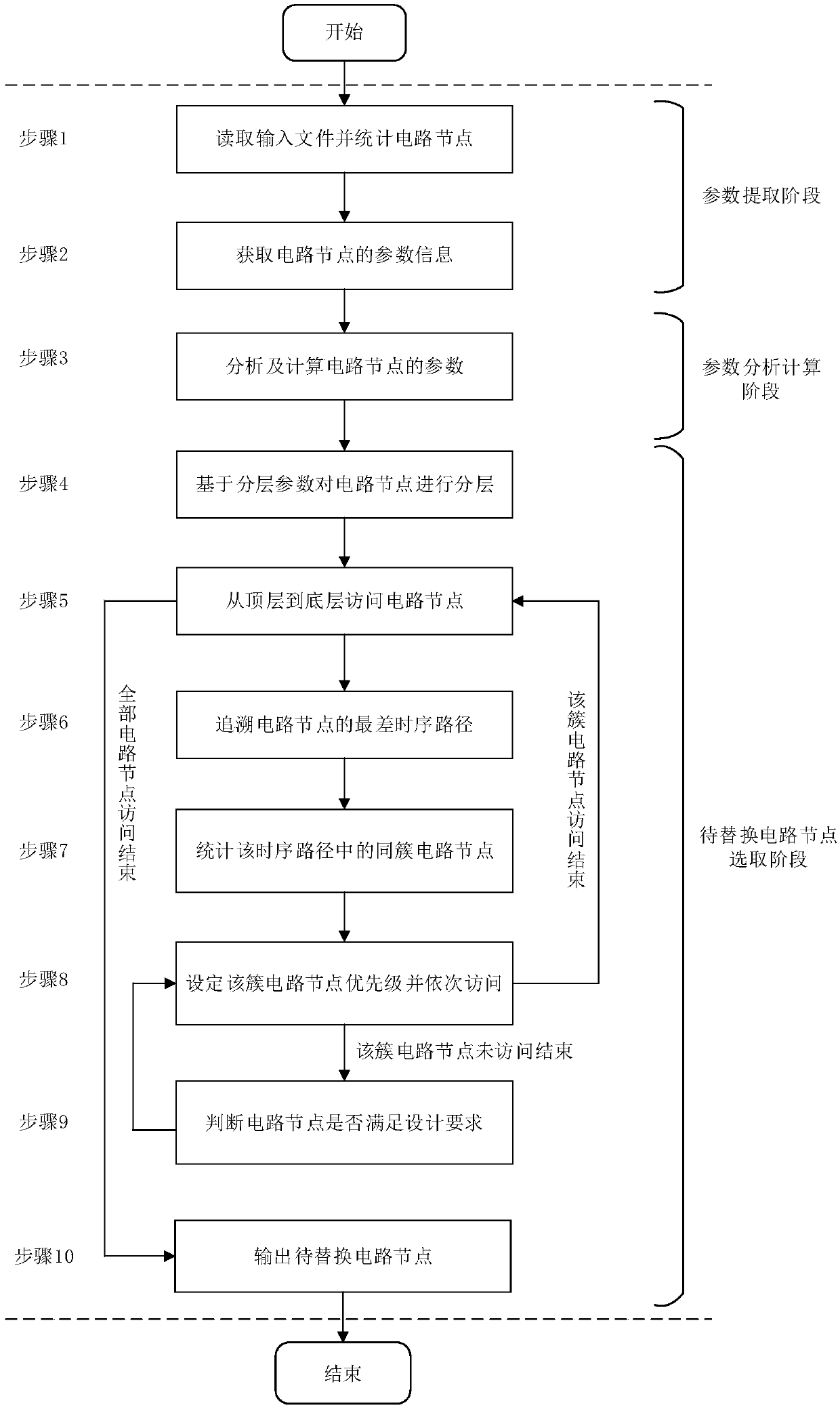

[0049] First, use circuit synthesis software to synthesize the test circuit, add design constraints, convert the RTL-level code into a circuit netlist, and generate a design constraint file. Then, input the generated circuit netlist and design constraint files into static timing analysis software for static timing analysis. Finally, the optimization method described in the present invention is used in the static timing analysis software. The method is realized by Tcl script language, and after the method is executed, a file containing circuit nodes to be replaced is output for use in a subsequent ASIC design process.

[0050] image 3 , Figure 4 It is the result obtained after performing the above operations on the o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More