Three-dimensional memory formation method

A memory, three-dimensional technology, applied in semiconductor devices, electric solid-state devices, electrical components, etc., can solve the problems of increasing the production cycle and production cost of three-dimensional memory, complicated operations, increasing structural shape changes and structural size changes, and shortening production. effect of cycle time, simplified operation steps, reduced risk of structural damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] Exemplary embodiments of the present disclosure will be described in more detail below with reference to the accompanying drawings. Although exemplary embodiments of the present disclosure are shown in the drawings, it should be understood that the present disclosure may be embodied in various forms and should not be limited by the embodiments set forth herein. Rather, these embodiments are provided for more thorough understanding of the present disclosure and to fully convey the scope of the present disclosure to those skilled in the art.

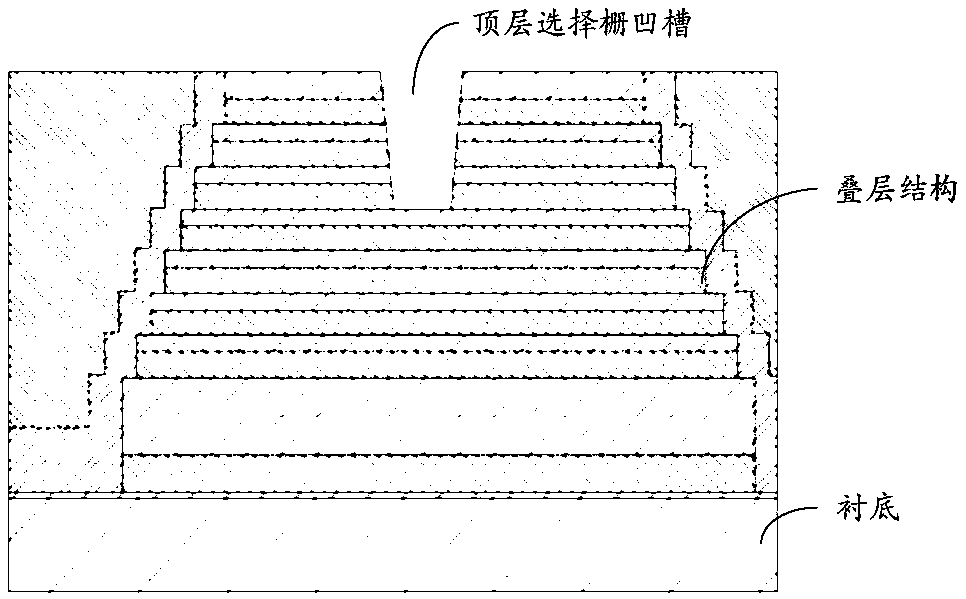

[0029] According to an embodiment of the present invention, a method for forming a three-dimensional memory is proposed, such as Figure 9 shown, including:

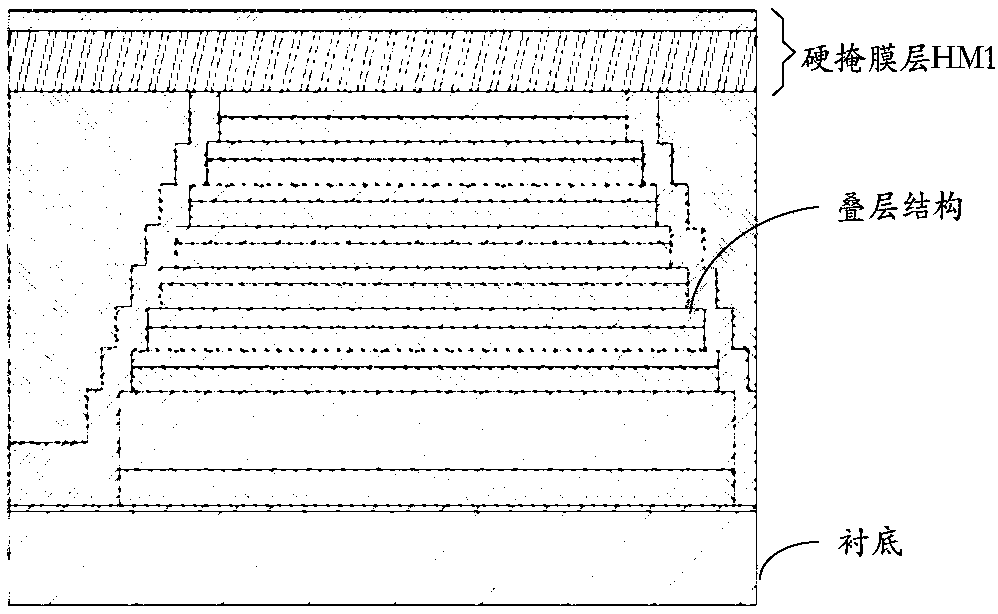

[0030] Provide a substrate, and form a stacked structure and a cutting line (Scrubber Line) on the substrate;

[0031] forming a first hard mask layer (Hard Mask) on the laminated structure and the dicing line;

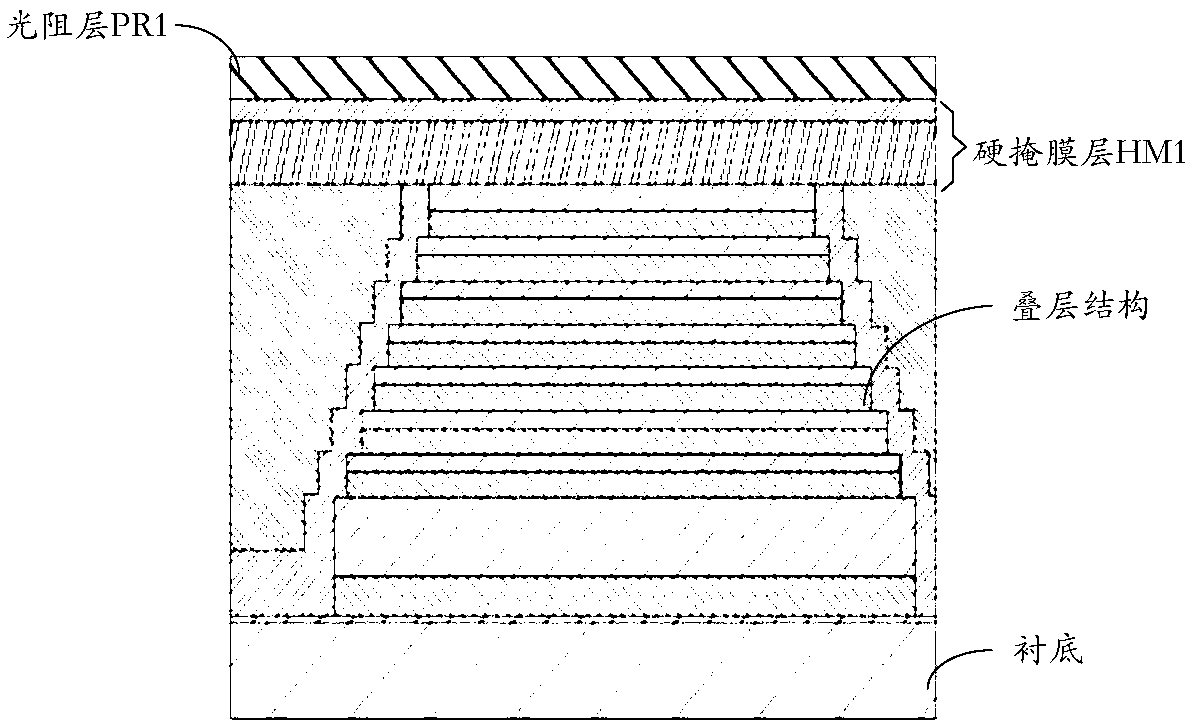

[0032] forming a photoresist layer (Photo Resist) on the firs...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More