Vertical double diffused field effect transistor and its manufacturing method

A field effect transistor, vertical double diffusion technology, applied in semiconductor/solid state device manufacturing, semiconductor devices, electrical components, etc., can solve problems affecting device performance, etc., to improve device performance, reduce on-resistance, and reduce resistance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The following will clearly and completely describe the technical solutions in the embodiments of the present invention. Obviously, the described embodiments are only some of the embodiments of the present invention, rather than all the embodiments. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

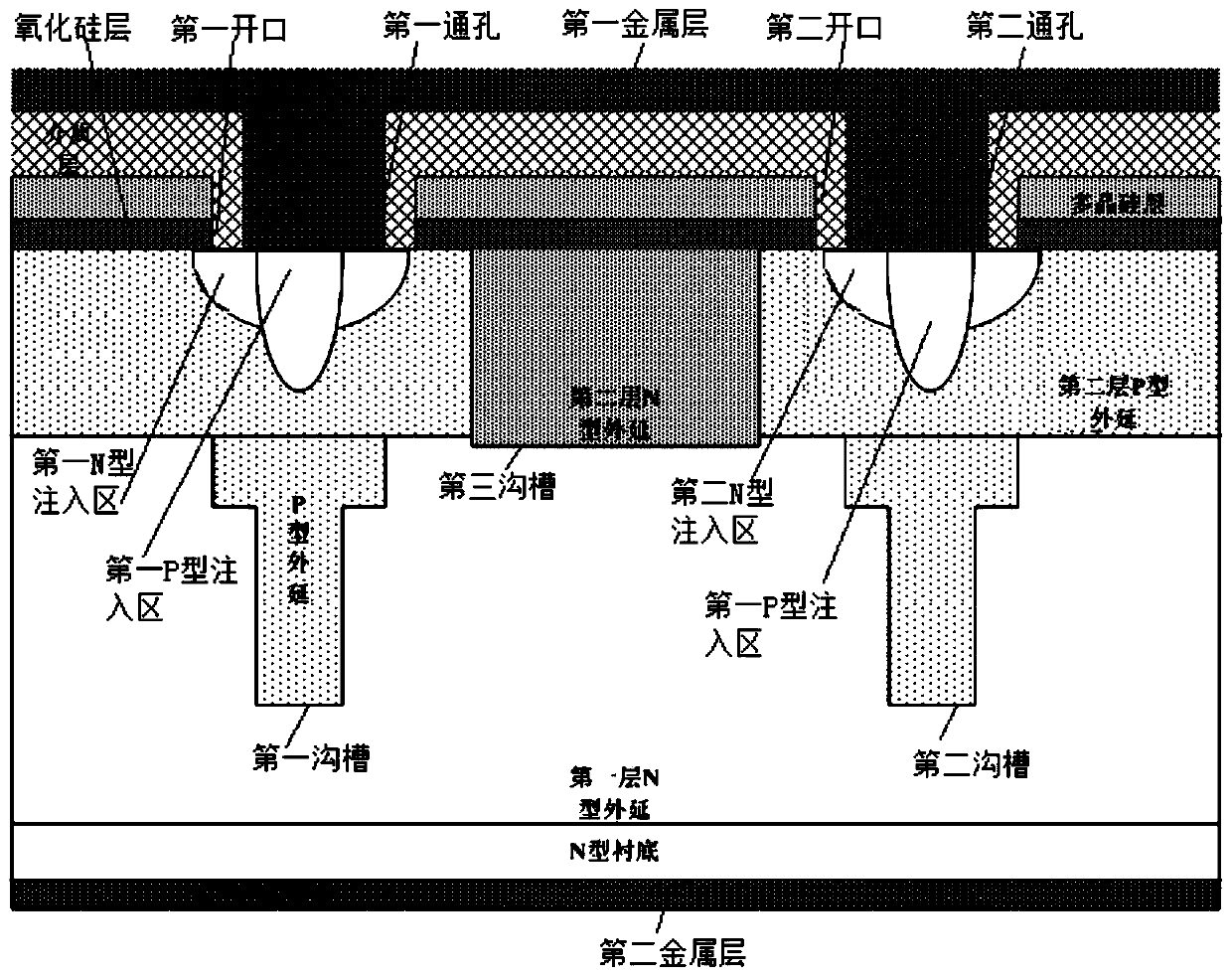

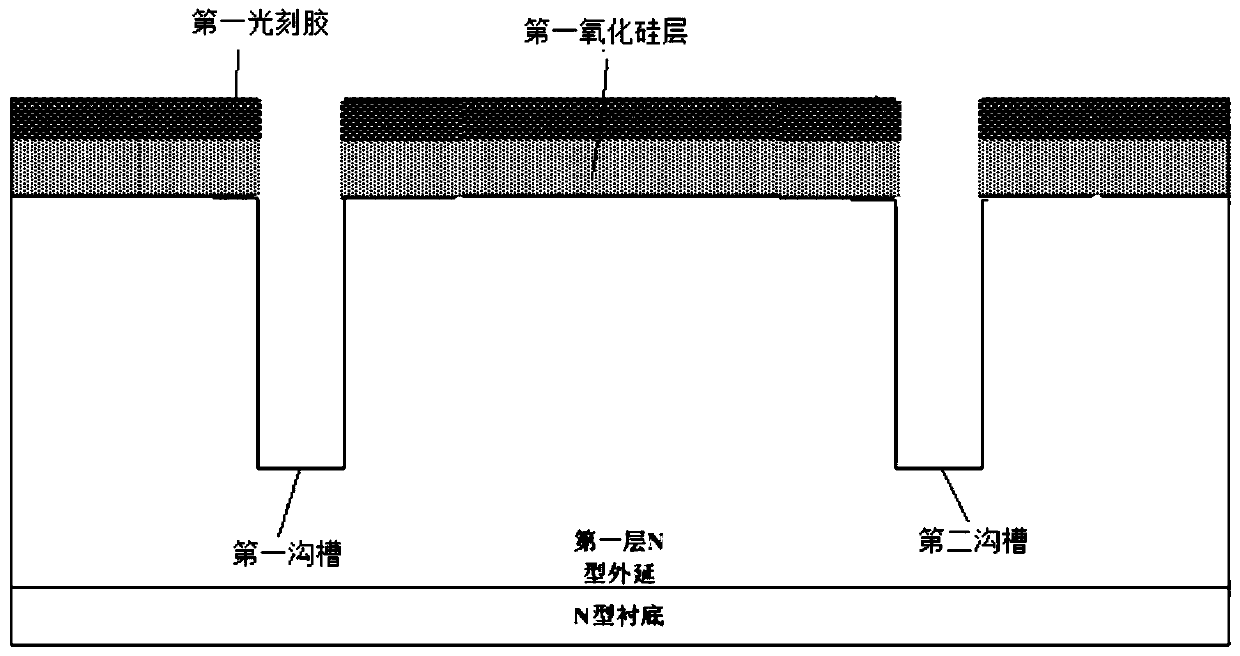

[0030] see figure 1 , figure 1 It is a schematic diagram of the cross-sectional structure of the vertical double-diffused field effect transistor provided by the present invention. The vertical double-diffused field effect transistor includes an N-type substrate, a first layer of N-type epitaxy formed on the N-type substrate, a first groove and a first layer of N-type epitaxial layer formed on the surface of the first layer of N-type epitaxial layer. Two trenches, the P-type epitaxy formed in the first trench and t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More