Core processing circuit design method for navigation system

A technology of circuit design and core processing, which is applied in the direction of navigation through speed/acceleration measurement, can solve the problems of failure to integrate bus transmission, low data transmission efficiency, single hardware function, etc., to achieve health monitoring, improve safety and Reliability and Power Consumption Reduction Effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] A navigation system core processing circuit design method, comprising the following steps:

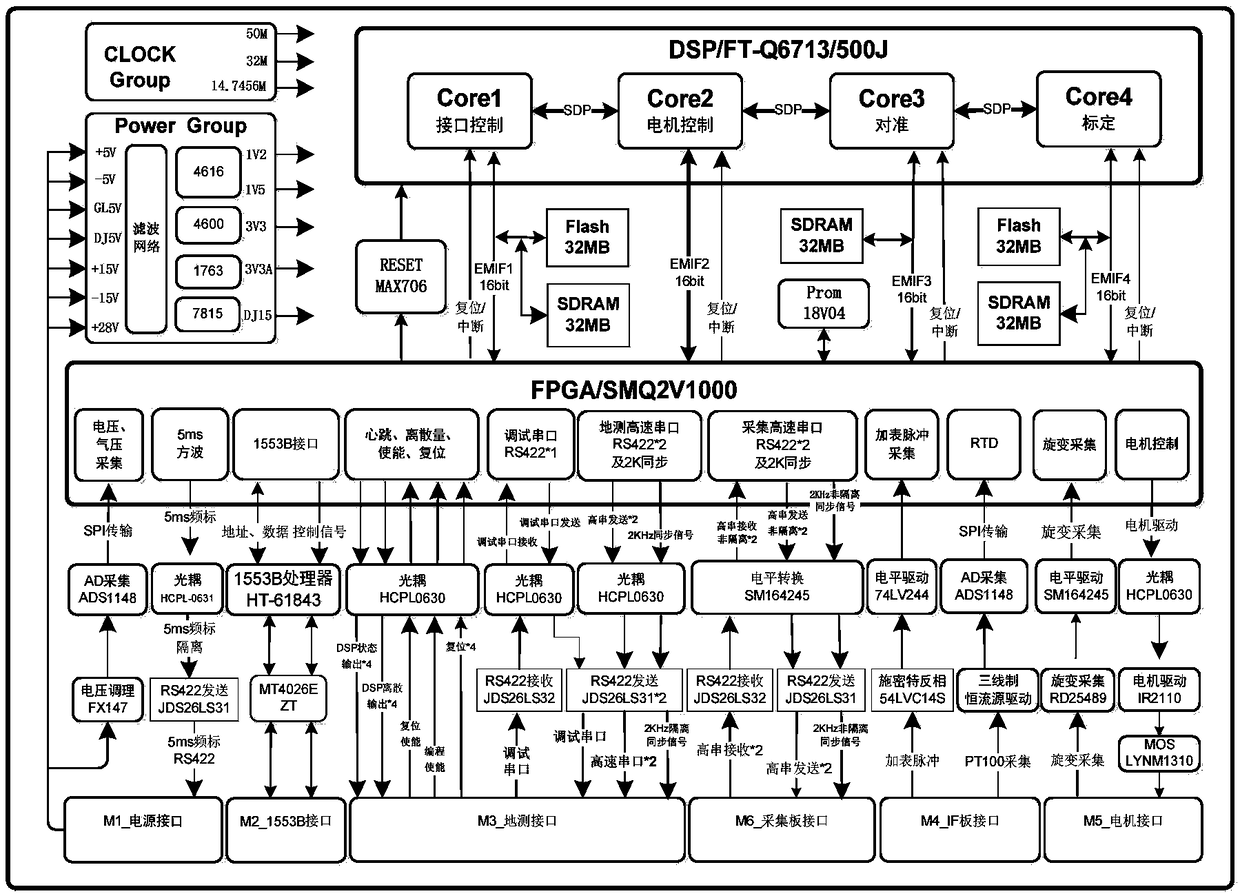

[0046] The specific implementation details are as follows: figure 1 shown

[0047] (1) The core circuit design method based on the multi-core FT-Q6713J / 500 processor chip.

[0048]The core processing circuit of the traditional navigation system is generally composed of two parts, one part is a single-core DSP to realize inertial calculation, gyro and acceleration acquisition, and the other part is a separate processor to realize the acquisition and transmission of RS422, RS429, 1553B and other interfaces and buses. Parts are coupled through dual-port or asynchronous serial bus. This heterogeneous architecture not only causes a wide variety of navigation system processors and complex development, but also the low data transmission efficiency between processors is not conducive to deep coupling between different sensors. Using the multi-core FT6713-500 processor chip, the bootst...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More