Multi-chip stack packaging structure

A packaging structure and chip stacking technology, applied in the direction of semiconductor/solid-state device parts, semiconductor devices, electrical components, etc., can solve the problems of reducing the integration degree of the package body, reducing the packaging density, and reducing the packaging efficiency, so as to save the curing time. , the effect of improving packaging density and improving packaging efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

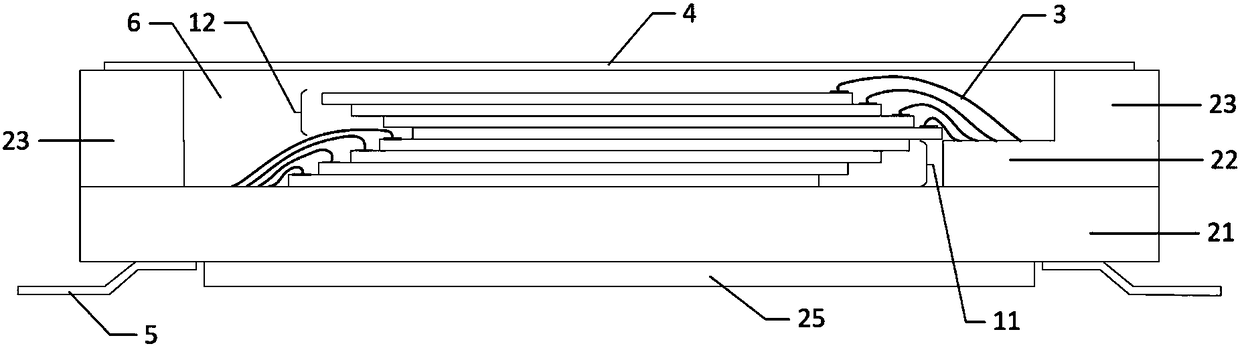

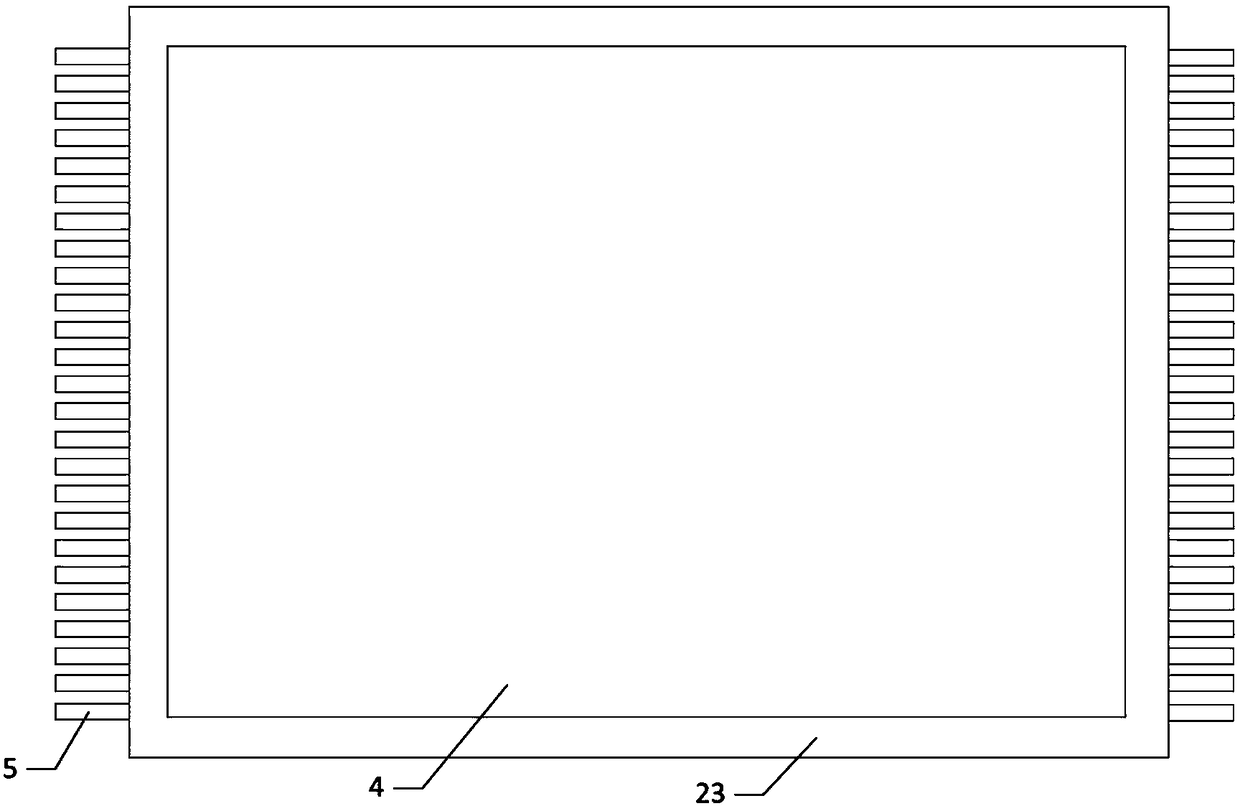

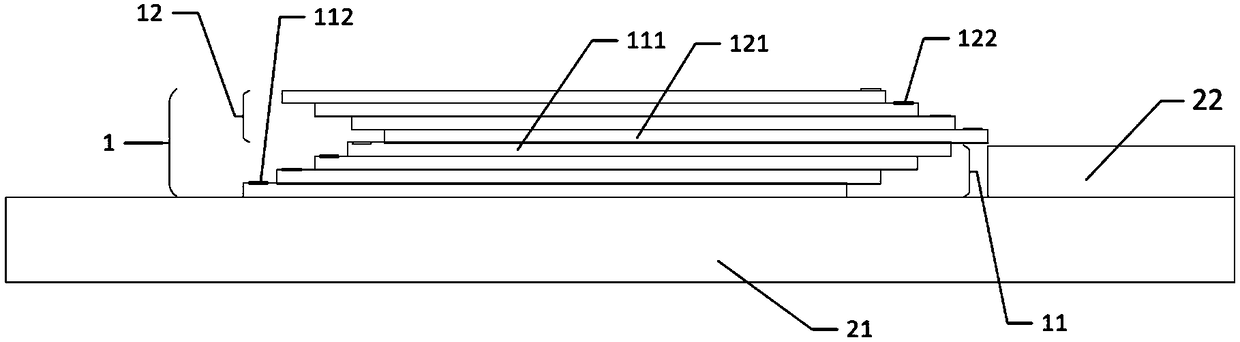

[0031] Preferred embodiments of the present invention are described below with reference to the accompanying drawings. Those skilled in the art should understand that these embodiments are only used to explain the technical principles of the present invention, and are not intended to limit the protection scope of the present invention. For example, although the following embodiments are explained in conjunction with memory chips, this is not limiting. The technical solution of the present invention is also applicable to logic chips or their combination with memory chips. The change of this application object Without departing from the principle and scope of the present invention.

[0032] In addition, in order to better illustrate the present invention, numerous specific details are given in the specific embodiments below. It will be understood by those skilled in the art that the present invention may be practiced without certain of the specific details. In some examples, s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More