GaN (Gallium Nitride) HEMT (High Electron Mobility Transistor) device and preparation method thereof

A device and N-type technology, applied in the field of GaNHEMT devices and their preparation, can solve the problems of limiting the high-frequency characteristics of GaNHEMT devices, increasing the complexity of the device manufacturing process, and large parasitic resistance of source and drain, so as to reduce parasitic capacitance and shrink gate Effects of long size and excellent RF characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

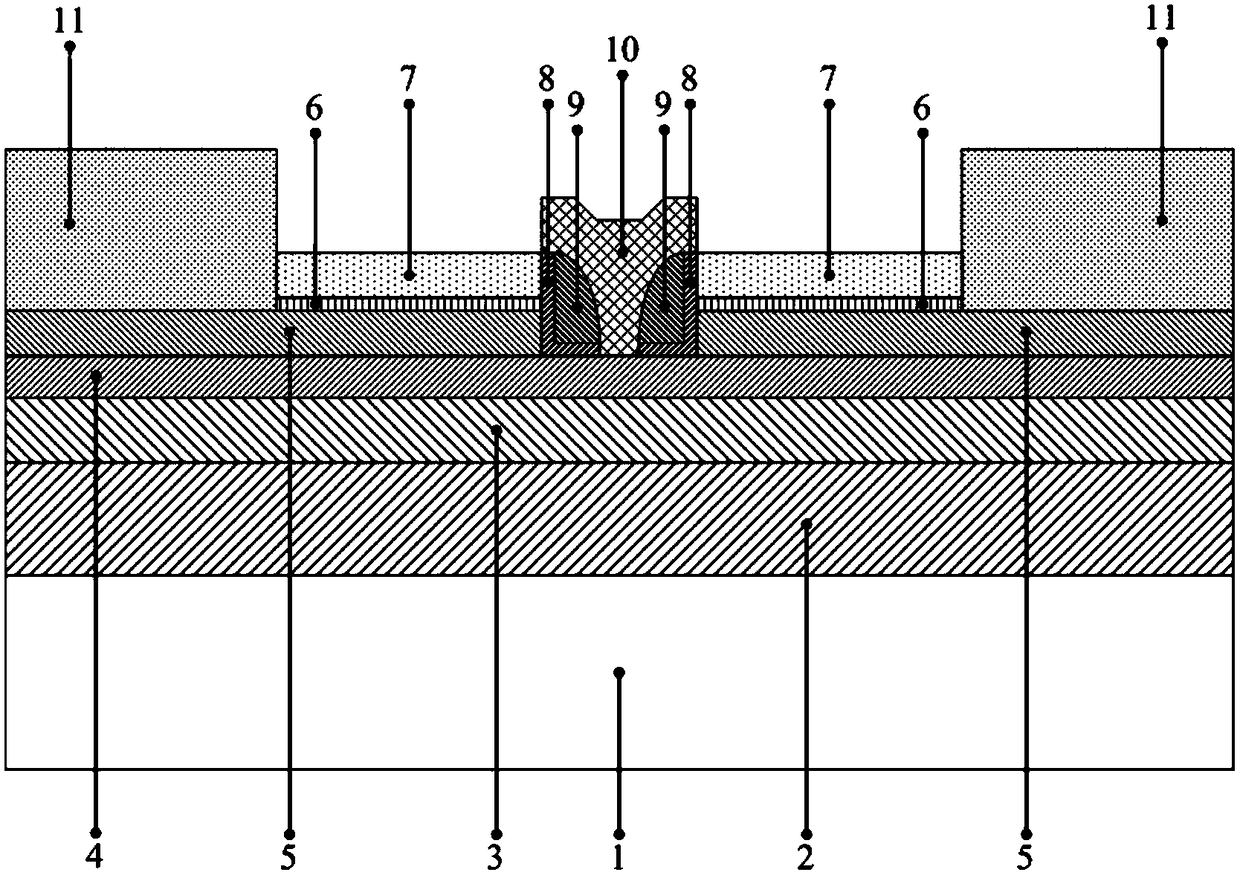

[0040] This embodiment provides a GaN HEMT device. refer to figure 1 As shown, the GaN HEMT device includes a substrate 1, a buffer layer 2, a GaN channel layer 3, a barrier layer 4, an N-type cap layer 5, a first passivation layer 6, a first dielectric layer 7, a second passivation layer layer 8, second dielectric layer 9, gate metal layer 10 and source-drain metal layer 11.

[0041]Wherein, the buffer layer 2 is stacked on the substrate 1; the GaN channel layer 3 is stacked on the buffer layer 2; the barrier layer 4 is stacked on the GaN channel layer 3; the N-type cap layer 5 is stacked on the barrier layer 4; the source-drain metal layer 11 is stacked on the outer edge of the N-type cap layer 5, and the first A passivation layer 6 is also stacked on the N-type cap layer 5, the first dielectric layer 7 is stacked on the first passivation layer 6, the first passivation layer 6 and the The first dielectric layer 7 is located between the source and drain metal layers on bot...

Embodiment 2

[0055] This embodiment provides a method for preparing a GaN HEMT device, including the following steps:

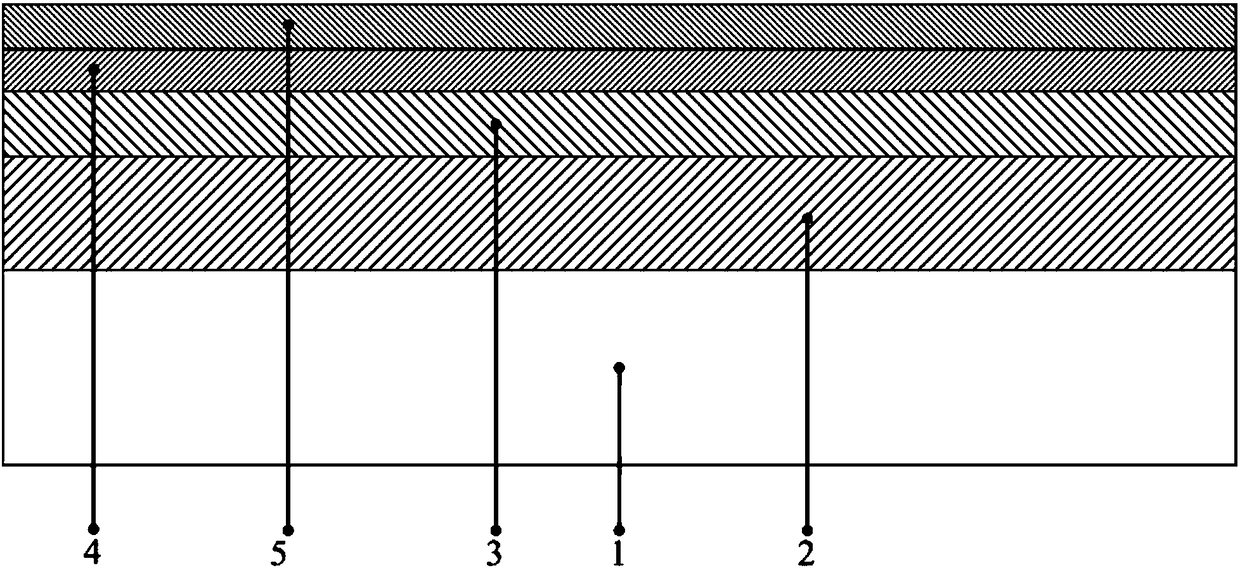

[0056] S1. Epitaxially form buffer layer 2, channel layer 3, barrier layer 4 and N-type cap layer 5 sequentially on substrate 1, such as figure 2 shown;

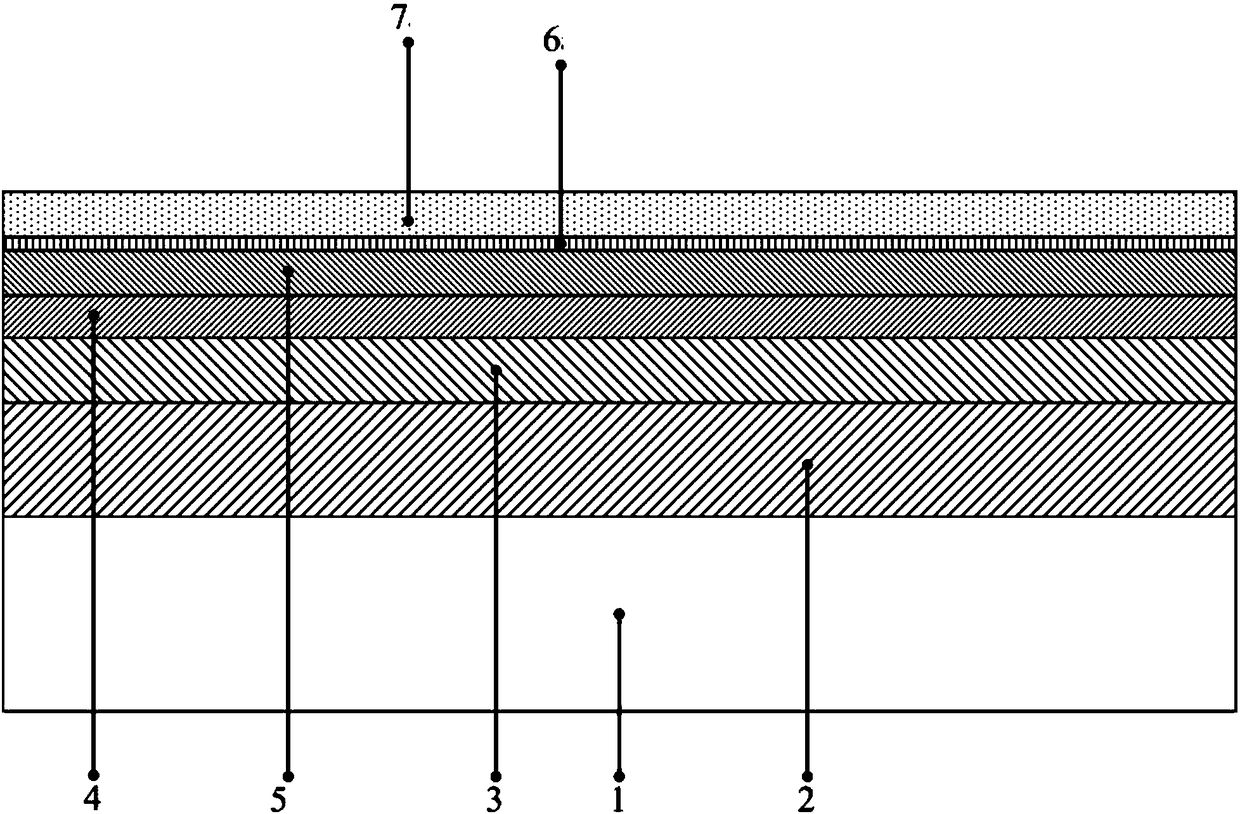

[0057] S2. Deposit the first passivation layer 6 and the first dielectric layer 7 sequentially on the N-type cap layer 5, and selectively remove part of the first passivation layer, part of the first dielectric layer and part of the N-type by dry etching cap layer, thereby forming a gate metal region 12 penetrating through the middle of the first dielectric layer 7, the first passivation layer 6 and the N-type cap layer 5, such as image 3 and 4 shown;

[0058] S3, sequentially depositing the second passivation layer 8 and the second dielectric layer 9, dry etching the second passivation layer 8 and the second dielectric layer 9 to make the upper surface of the barrier layer 4 located in the gate metal region 12 Th...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More