Lateral transistor and manufacturing method thereof

A technology of lateral transistors and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., and can solve the problems of low device emitter emissivity and poor current amplification capability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

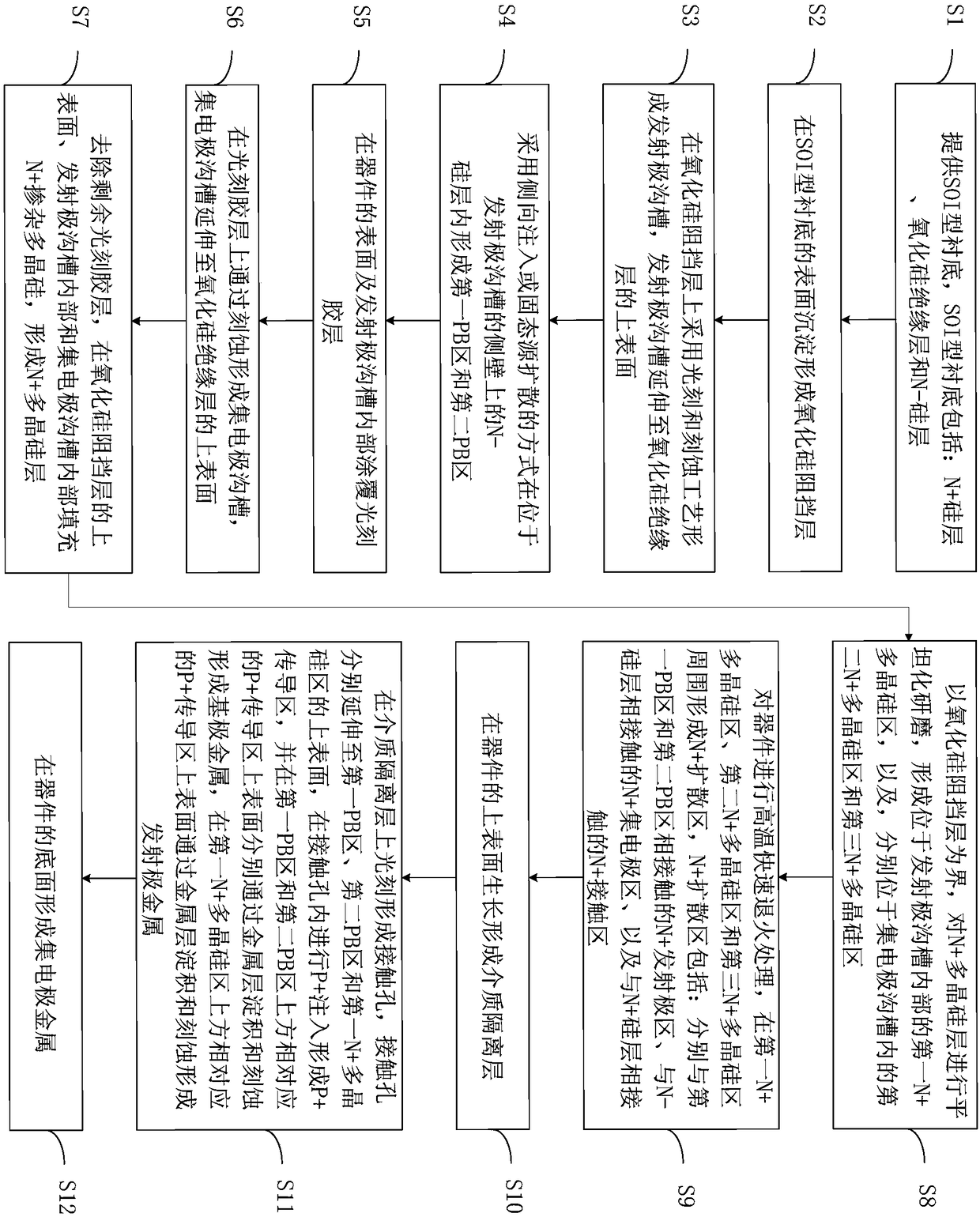

[0051] see figure 1 , a flowchart of a method for fabricating a lateral transistor provided by an embodiment of the present invention. A method for fabricating a lateral transistor provided in an embodiment of the present invention includes the following steps:

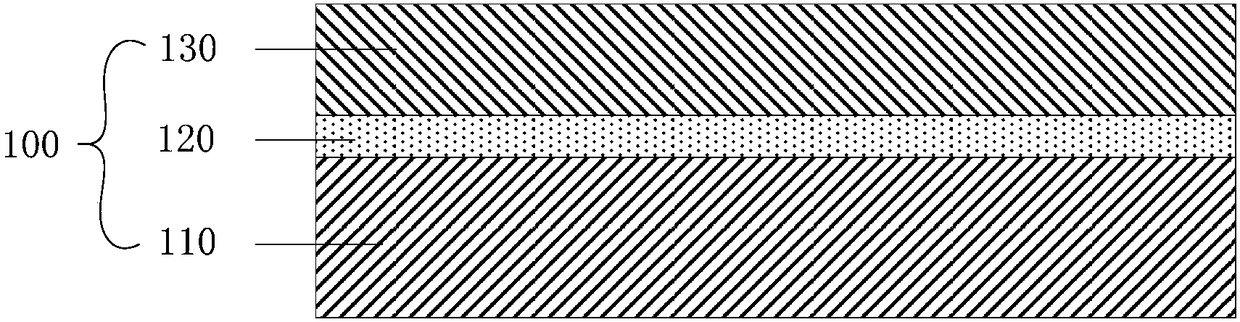

[0052] Step 1: Provide an SOI type substrate 100 , which sequentially includes an N+ silicon layer 110 , a silicon oxide insulating layer 120 and an N − silicon layer 130 from bottom to top. see figure 2 , a product schematic diagram of Step 1 in the method for fabricating a lateral transistor provided in an embodiment of the present invention.

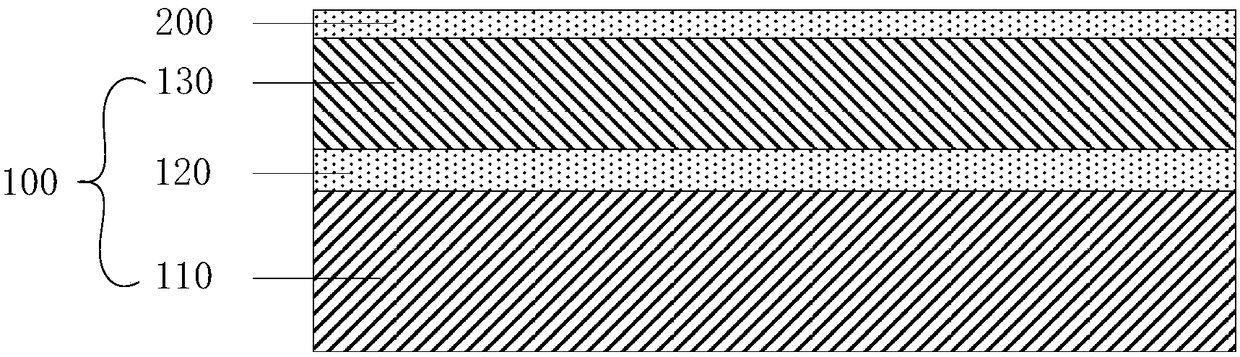

[0053] Step 2: forming a silicon oxide barrier layer 200 by depositing on the surface of the SOI substrate. see image 3 , a product schematic diagram of Step 2 in the method for fabricating a lateral transistor provided in an embodiment of the present invention.

[0054] Step 3: Form an emitter trench on the silicon oxide blocking layer 200 by photolithography and etch...

Embodiment 2

[0067] A lateral transistor provided by an embodiment of the present invention is prepared according to the above method for manufacturing a lateral transistor, including: an SOI substrate, a silicon oxide barrier layer, a first PB region, a second PB region, and a first N+ polysilicon region, the second N+ polysilicon region, the third N+ polysilicon region, N+ diffusion region, dielectric isolation layer, P+ conduction region, emitter metal, base metal and collector metal. Wherein, the SOI type substrate includes: N+ silicon layer, silicon oxide insulating layer and N- silicon layer, and the N+ diffusion area includes: N+ emitter area, N+ collector area and N+ contact area. see Figure 13 , in the manufacturing method of the lateral transistor provided in the above embodiment, the product in the product schematic diagram in step 12 is the structural schematic diagram of the lateral transistor provided in the embodiment of the present invention.

[0068] The silicon oxide ba...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Width | aaaaa | aaaaa |

| Width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com