FPGA chip, intermediate frequency demodulation card and satellite data transmission ground detection test intermediate frequency receiver

A receiver and chip technology, which is applied in the field of satellite data transmission subsystem ground test, can solve the problems of single-function ground test equipment, etc., to improve portability, enhance design flexibility and upgradeability, and optimize demodulation performance Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0052] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

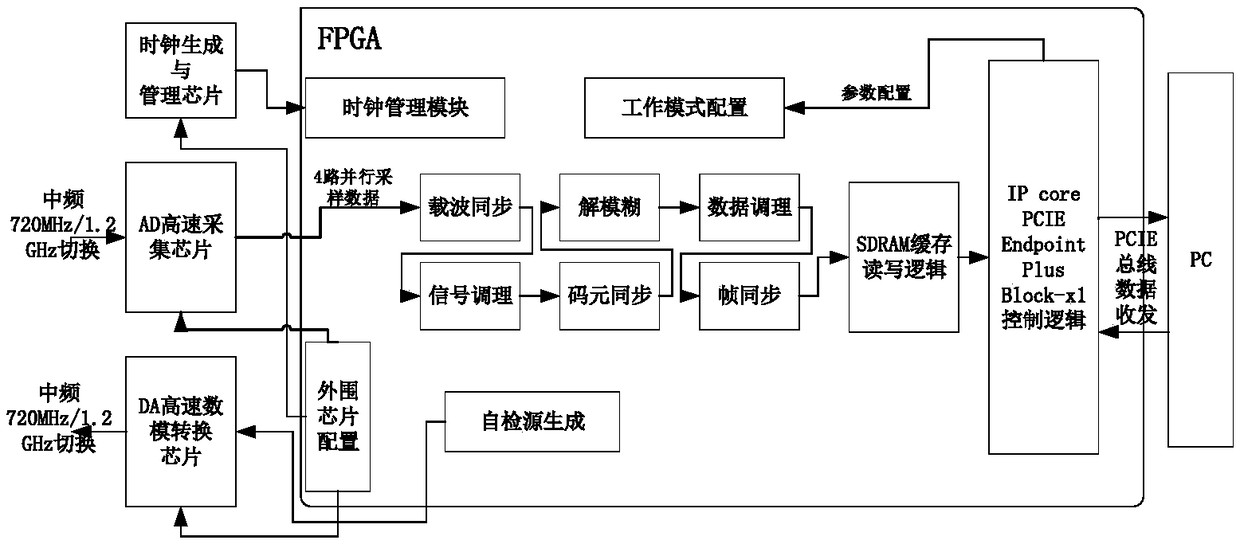

[0053] Since FPGA has the characteristics of high processing speed, strong flexibility, and rich resources, this design is based on the current mainstream modular design idea, the design architecture of software radio, and the design of intermediate frequency data processing algorithm with FPGA as the core reflects the stability of software radio system High, flexible, convenient for secondary development, inheritability and scalability, etc., are very suitable for implementing equipment and systems with multiple functional modes, high performance requirements, and strong reliability.

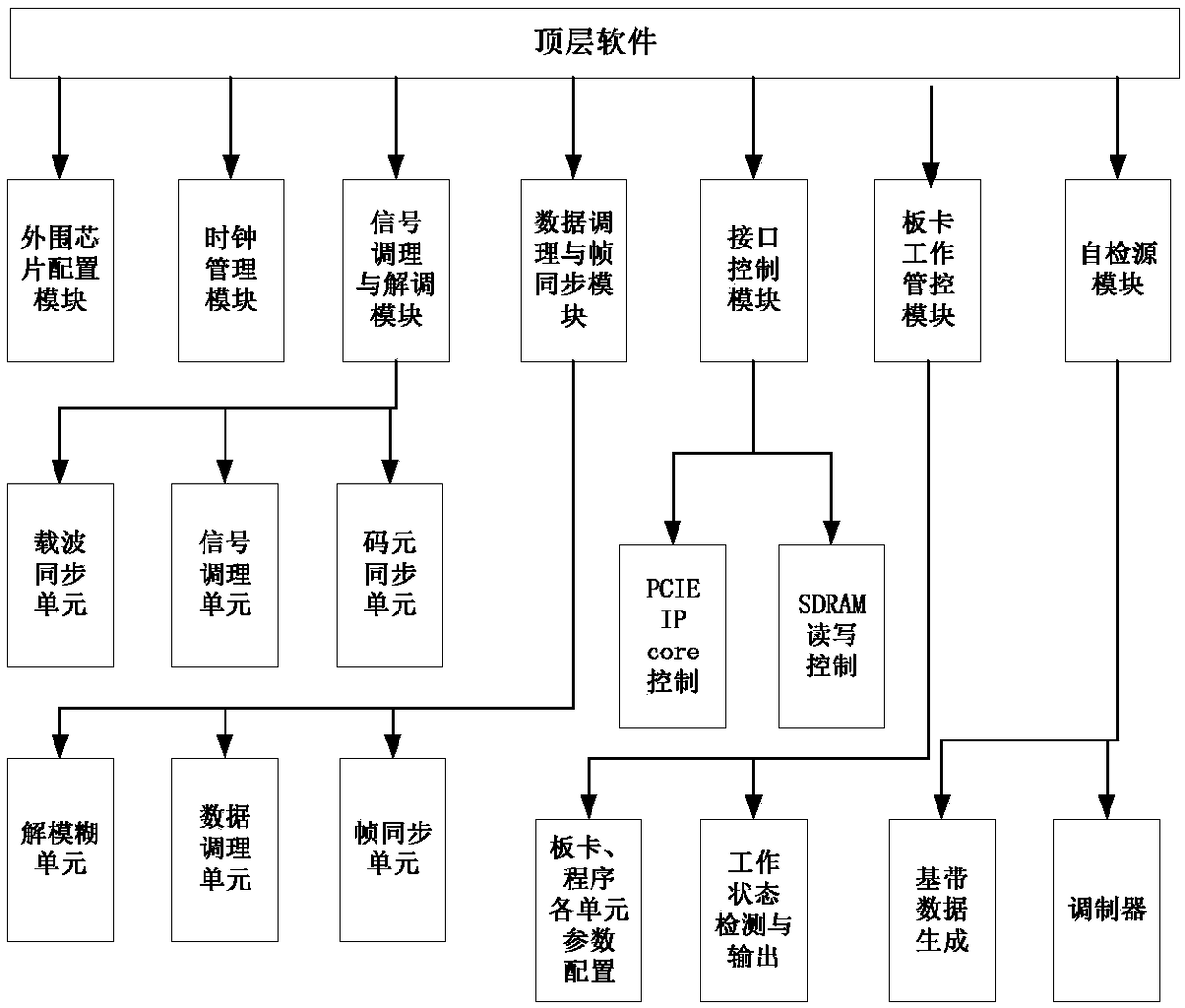

[0054] Such as figure 1 As shown, the working principle of the FPGA top-level software and each logic module is briefly described as follows:

[0055] Top-level software: define the input and output interfaces, and connect the secondary logic modules through ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More