Self-adaptive routing single-cycle on-chip network router

A network-on-chip, self-adaptive technology, applied in the direction of data exchange network, digital transmission system, electrical components, etc., can solve problems such as network deadlock and implementation complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

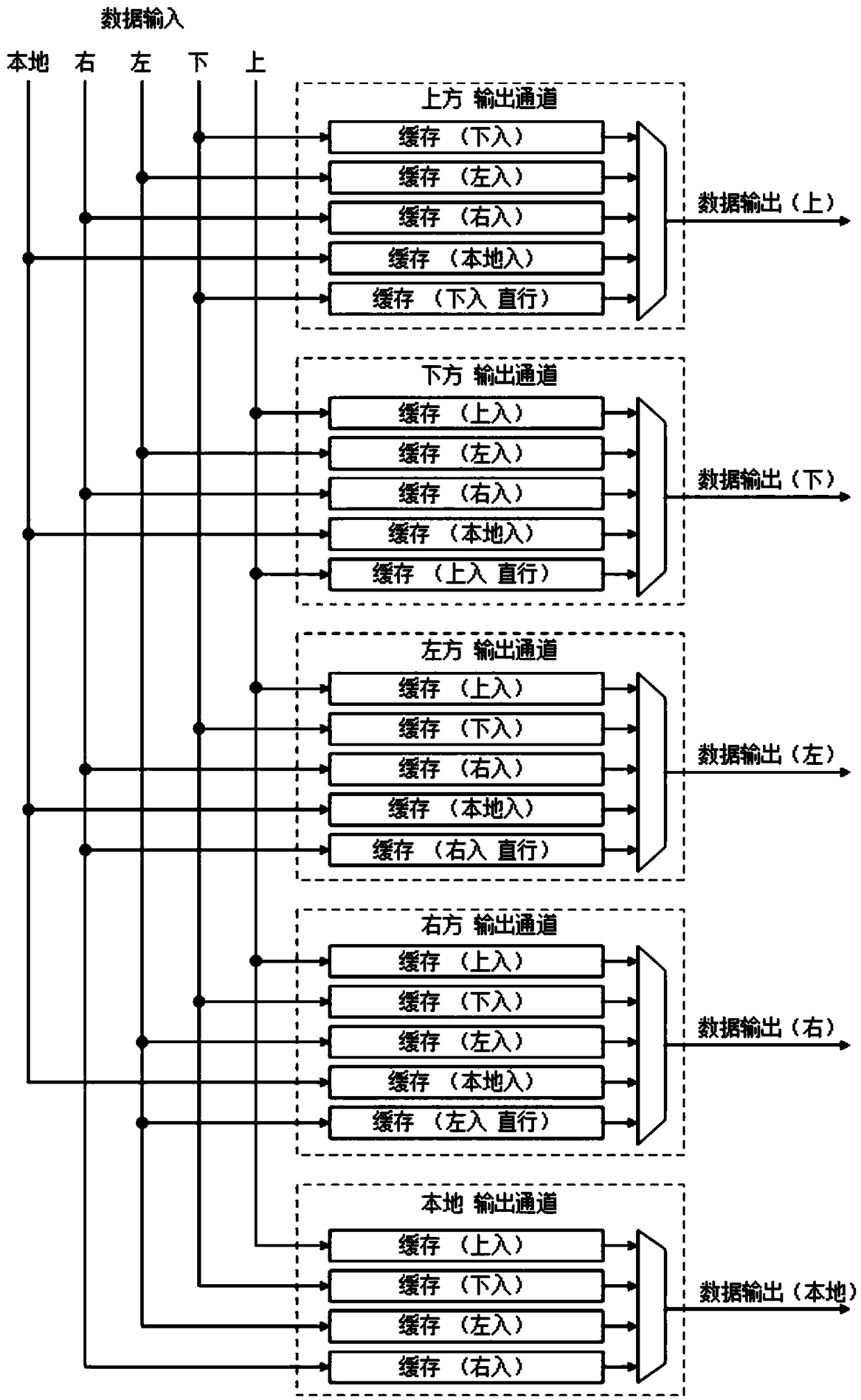

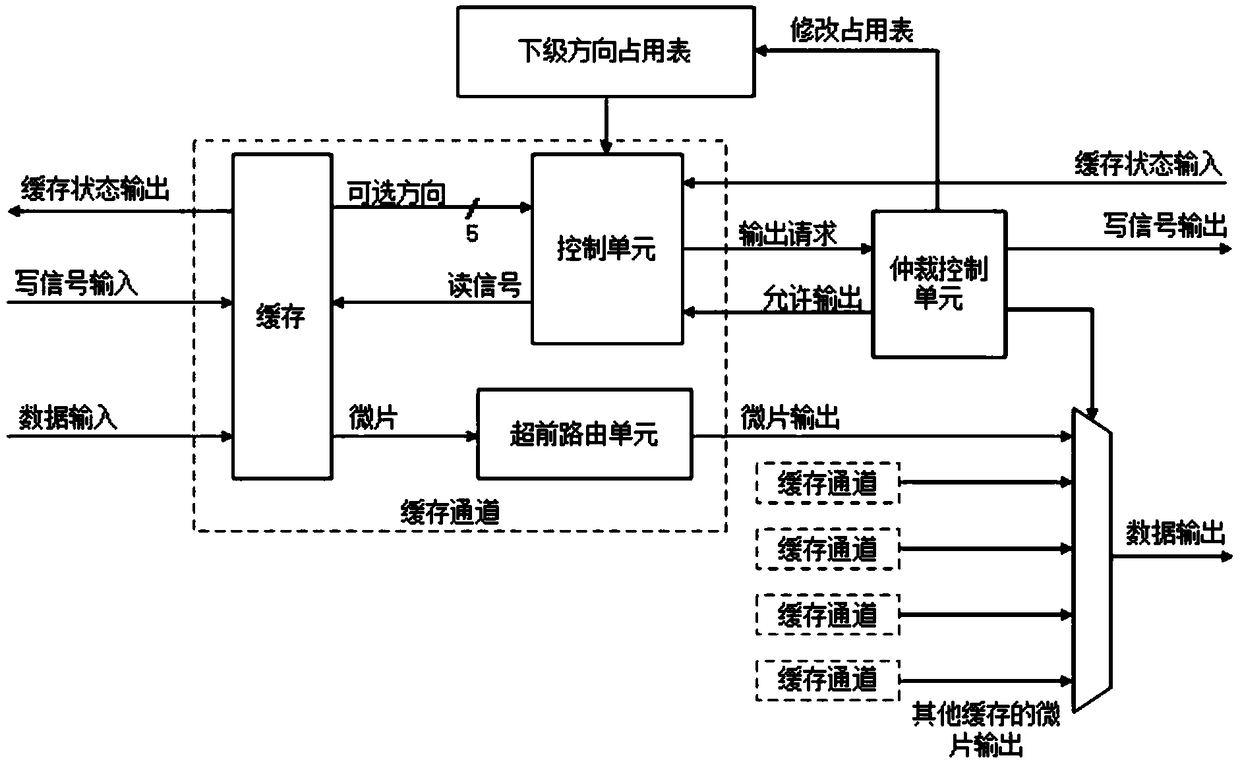

[0014] figure 2 is a specific implementation of an output channel. Each cache unit has its own exclusive routing unit and control unit, which together are called a cache channel, and a dotted box in the figure is a cache channel. Since each cache channel uses the same structure, figure 2 Only one of the five cache channels is expanded in . In addition to buffer channels, an output channel also includes an arbitration control unit, a lower-level direction occupancy table, and a multiplexer, and these three modules are shared by all buffer channels.

[0015] The occupancy state of caches in each direction of the lower-level router is stored in the lower-level direction occupation table. After the circuit is reset, all directions are idle. When a buffer channel is outputting a data packet, it will occupy a direction, and the occupied direction will be recorded in the lower-level direction occupation table, and other buffer channels cannot request from this direction. Direct...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More