Display chip for virtual reality

A display chip and virtual reality technology, applied in the field of virtual reality, can solve the problems of poor comprehensive effect of display chips, poor near-eye display effect, inconvenient portability, etc., to enhance immersive experience, realize large-scale mass production, and improve standby time the effect of time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

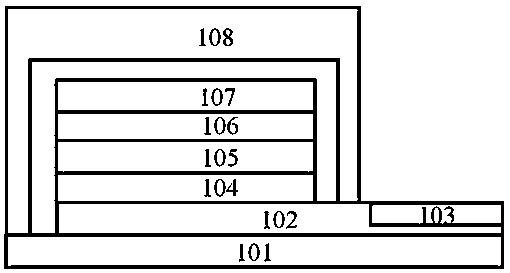

[0025] refer to figure 1 , a display chip for virtual reality, comprising: a single crystal silicon substrate 101 and a driving circuit layer 102, a bonding pad layer 103 located on the surface of the driving circuit layer 102, a cathode pixel layer 104, a color light emitting Layer 105, a transparent common anode layer 106, a single-layer thin film encapsulation layer 107, and a glass cover 108; the size of the single crystal silicon substrate 101 is 0.6 inches; the driving circuit layer 102 is made by CMOS integrated circuit technology, and its transistor The feature size is 90 nm, supporting dual voltage or multi-voltage regions, the analog circuit voltage range is -5V to +5V, and the digital circuit voltage is +1V to +5V; the driving circuit layer 102 includes a transistor layer, a transistor to metal wiring The connection hole layer of the layer, one or more metal wiring layers, one or more via layers between the metal wiring layers, a via hole under the cathode pixel lay...

Embodiment 2

[0027] refer to figure 1, a display chip for virtual reality, comprising: a single crystal silicon substrate 101 and a driving circuit layer 102, a bonding pad layer 103 located on the surface of the driving circuit layer 102, a cathode pixel layer 104, a color light emitting Layer 105, a transparent common anode layer 106, a single-layer thin film encapsulation layer 107, and a glass cover 108; the size of the monocrystalline silicon substrate 101 is less than 1 inch; the driving circuit layer 102 is made by CMOS integrated circuit technology, and its The characteristic size of the transistor is 0.13 microns, and it supports dual voltage or multi-voltage regions. The voltage range of the analog circuit is -5V to +5V, and the voltage of the digital circuit is +1V to +5V; the driving circuit layer 102 includes a transistor layer, a transistor-to-metal connection The connection hole layer of the wiring layer, one or more metal wiring layers, the via layer between one or more met...

Embodiment 3

[0029] refer to figure 1 , a display chip for virtual reality, comprising: a single crystal silicon substrate 101 and a driving circuit layer 102, a bonding pad layer 103 located on the surface of the driving circuit layer 102, a cathode pixel layer 104, a color light emitting Layer 105, a transparent common anode layer 106, a single-layer thin film encapsulation layer 107, and a glass cover 108; the size of the monocrystalline silicon substrate 101 is less than 1 inch; the driving circuit layer 102 is made by CMOS integrated circuit technology, and its The characteristic size of the transistor is 0.35 microns, supporting dual voltage or multi-voltage regions, the voltage range of the analog circuit is -5V to +5V, and the voltage of the digital circuit is +1V to +5V; the driving circuit layer 102 includes a transistor layer, a transistor to metal connection The connection hole layer of the wiring layer, one or more metal wiring layers, the via layer between one or more metal w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More