Three-layer heterojunction organic field-effect transistor memory and fabrication method thereof

A heterojunction and organic field technology, which is applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve problems such as poor data stability, low current switch ratio, difficult multi-level storage, etc., to achieve easy operation, Effect of reducing dependence on operating voltage and improving memory speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0045] A method for preparing a three-layer heterojunction organic field effect transistor memory, comprising the following steps:

[0046] (1) Configure polymer solution, dissolve in low boiling point solvent, concentration 3~5 mg / mL;

[0047] (2) Select a suitable substrate, and sequentially form a gate electrode and a gate insulating layer on the substrate, as the substrate, the thickness of the gate insulating layer is 50~300 nm, then clean the substrate and dry it, and set it aside;

[0048] (3) Treat the dried substrate in step (2) with ultraviolet ozone for 3-5 minutes;

[0049] (4) Spin-coat the solution prepared in step (1) on the substrate prepared in step (3), with a thickness of 25-70 nm, and dry and anneal the spin-coated sample;

[0050] (5) An organic heterojunction semiconductor layer and source-drain electrodes are sequentially vapor-deposited on the sample prepared in step (4).

[0051] In step (1), the polymer in the polymer solution is polyvinylpyrrolidon...

Embodiment 1

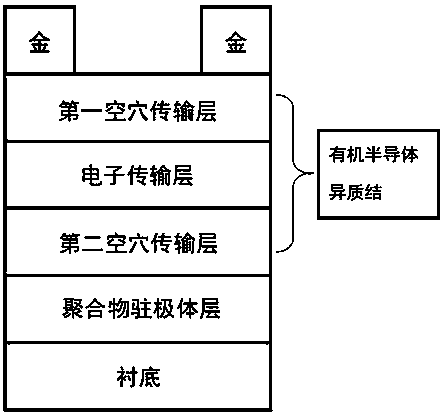

[0055] like Figure 1-8 As shown, a three-layer heterojunction organic field effect transistor memory, including:

[0056] Substrate;

[0057] a gate electrode formed over the substrate;

[0058] a gate insulating layer and a polymer electret layer covering the gate electrode, and a gate insulating layer between the gate electrode and the polymer electret layer;

[0059] a second hole transport layer formed over the polymer electret layer;

[0060] a charge transport layer formed on the second hole transport layer;

[0061] a first hole transport layer formed on the charge transport layer;

[0062] Porous source and drain electrodes formed on both sides of the channel region on the surface of the first hole transport layer.

[0063] The substrate is highly doped silicon.

[0064] In the technical solution of this embodiment 1, the materials selected for the substrate and the gate electrode are highly doped silicon, the thickness of the gate insulating layer is 50-300 nm,...

Embodiment 2

[0078] A three-layer heterojunction organic field effect transistor memory, comprising:

[0079] Substrate;

[0080] a gate electrode formed over the substrate;

[0081] a gate insulating layer and a polymer electret layer covering the gate electrode, and a gate insulating layer between the gate electrode and the polymer electret layer;

[0082] a second hole transport layer formed over the polymer electret layer;

[0083] a charge transport layer formed on the second hole transport layer;

[0084] a first hole transport layer formed on the charge transport layer;

[0085] The source and drain electrodes are formed on both sides of the channel region on the surface of the first hole transport layer.

[0086] The substrate is any one of highly doped silicon wafer, glass wafer or plastic PET.

[0087] In the technical scheme of this embodiment 2, highly doped silicon is used as the substrate and the gate electrode; a layer of 50nm silicon dioxide is used as the gate insulat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More