Circuit and method for testing on-chip memory

An on-chip memory and test circuit technology, applied in static memory, instruments, etc., can solve problems such as inconvenience of on-chip memory testing, and achieve the effect of simplifying the mass production test process, avoiding accidents, and scientifically structured.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

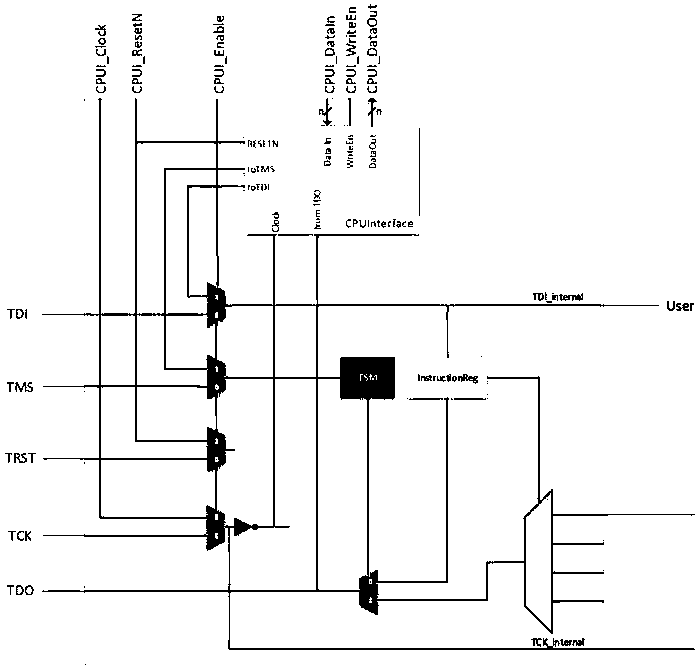

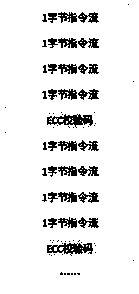

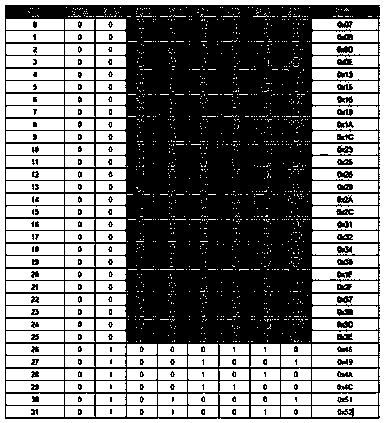

[0050] This embodiment provides an on-chip memory test circuit, such as figure 1 As shown, the on-chip memory test circuit includes an embedded self-test circuit 10, a TAP controller 20, a test instruction conversion circuit 30 and an off-chip Flash40, wherein: the embedded self-test circuit 10 is configured by an EDA tool to the RTL code. The on-chip memory 50 is inserted and formed to generate test vectors; the TAP controller 20 is correspondingly generated when the embedded self-test circuit 10 is formed, and during mass production, the external test device 60 communicates with the TAP controller 20 through the JTAG interface communication, and configure the embedded self-test circuit 10, select to open single or multiple embedded self-test circuits 10 to test the on-chip memory 50; the EDA tool sets the hardware bus width, and uses the first A script converts the test vector into a first test instruction, encapsulates the first test instruction, encodes it and converts it ...

Embodiment 2

[0066] The present embodiment also provides an on-chip memory testing method, the on-chip memory 50 testing method includes: the embedded self-test circuit 10 is formed by inserting the on-chip memory 50 in the RTL code by the EDA tool, and generates test vectors; TAP controller 20 Correspondingly generated when the embedded self-test circuit 10 is formed, during mass production, an external test device communicates with the TAP controller 20 through the JTAG interface, and configures the embedded self-test circuit 10, and selects to open a single or a plurality of embedded self-test circuits 10 to test the on-chip memory 50; the EDA tool sets the hardware bus width, utilizes the first script to convert the test vector into the first test instruction, and converts the second test vector to the first test instruction. A test command is encapsulated, encoded and converted into a binary command stream in bytes, the binary command stream produces a corresponding ECC check code, and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More