A kind of lateral trench mosfet device and its preparation method

A technology of lateral grooves and devices, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., and can solve problems such as low working speed, poor reverse recovery characteristics, and high power loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

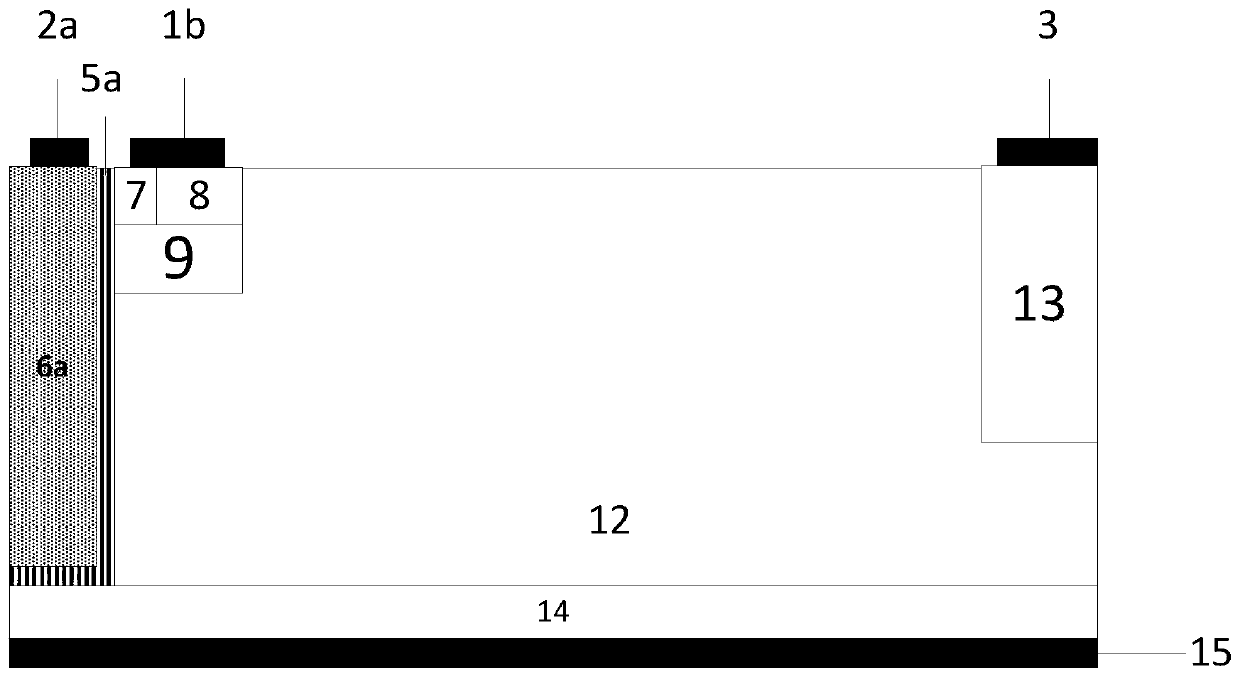

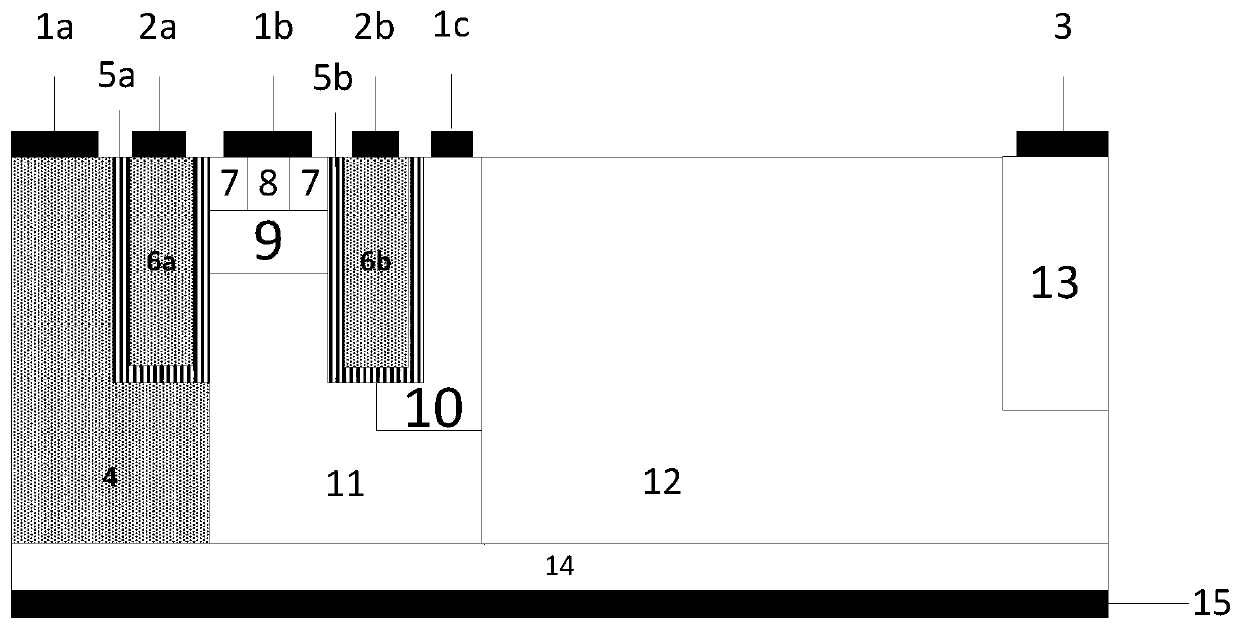

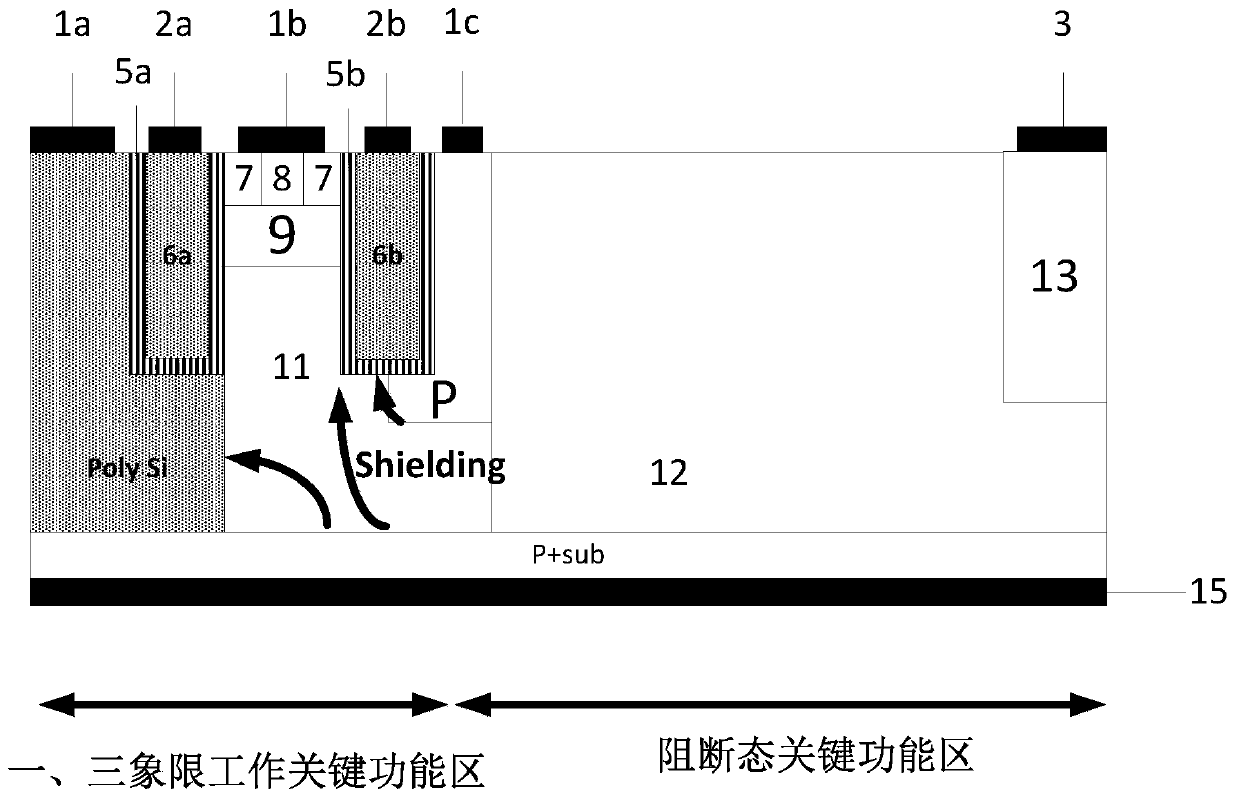

[0098] A lateral silicon carbide MOSFET provided in this embodiment has a device cell structure such as figure 2 As shown, it includes a silicon carbide P-type substrate 14 and a substrate electrode 15 arranged on the back of the silicon carbide P+ substrate 14; The N-type doped region 11 and the SiC N-type drift region 12, the doping concentration of the SiC N-type doped region 11 is higher than that of the SiC N-type drift region 12; The top layer is provided with a silicon carbide N+ drain region 13, and the upper surface of the silicon carbide N+ drain region 13 is provided with a drain metal 3; a polysilicon region is provided on the top layer on the side of the silicon carbide N-type doped region 11 away from the drain metal 3 4. The upper and lower surfaces of the polysilicon region 4 are flush with the silicon carbide N-type doped region 11, and the polysilicon region 4 and the silicon carbide N-type doped region 11 form a heterojunction with rectifying characteristic...

Embodiment 2

[0100] A lateral silicon carbide MOSFET provided in this embodiment has a device cell structure such as Figure 4 As shown, the difference from Embodiment 1 is that the substrate is an SOI substrate. The SOI substrate includes BULK region 18, SOI dielectric layer 17 and silicon carbide N+ substrate 16 from bottom to top, such as Figure 4 shown. This improvement not only isolates the substrate current, but also provides a low-resistance path for electrons, such as Figure 5 shown. Therefore, the improvement is beneficial to improve the on-state performance of the device;

Embodiment 3

[0102] A lateral silicon carbide MOSFET provided in this embodiment has a device cell structure such as Image 6 As shown, the difference from Embodiment 1 is that the polysilicon region 4 is now a Schottky contact metal 19, such as Image 6 shown. The polysilicon 4 or the Schottky contact metal 19 forms a rectifying contact with the silicon carbide N- epitaxy 9. As described in the principle of the invention, this contact has an obvious effect on optimizing the third quadrant of the device.

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More