A digital circuit design method of heterogeneous dual-magnetron memristor model based on DSP Builder is presented

A technology of circuit design and memristor, which is applied in the field of memristor circuit design and simulation, can solve problems such as limiting the application of analog chaotic circuits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0057] Embodiment 1: Circuit design of heterogeneous magnetron memristor 1 .

[0058] For the magnetron memristor 1 constructed in step 1, the schematic diagram of its equivalent analog circuit is as follows Figure 6 As shown, it consists of 3 operational amplifiers, 2 multipliers, 1 capacitor and 5 resistors. The first stage operational amplifier U a circuit is used to avoid loading effects. The second stage with resistor R b and capacitance C a connected op amp U b The circuit is an integrator that implements the relationship that

[0059]

[0060] Level 3 with R c , R d and R e connected op amp U c circuit is a current inversion circuit, when R d = R e The following relationship can be realized when

[0061]

[0062] where g 1 , g 2 for multiplier A 1 ,A 2 scale factor.

[0063] Simultaneous equations (11) and (12), the equivalent memorization expression can be obtained as

[0064]

[0065] The parameter values of each component in the circuit ...

Embodiment 2

[0067] Embodiment 2: Circuit design of heterogeneous magnetron memristor 2

[0068] For the magnetron memristor 2 constructed in step 2, the schematic diagram of its equivalent analog circuit is as follows Figure 7 As shown, it consists of 4 operational amplifiers, 2 multipliers, 1 capacitor and 7 resistors. The first stage operational amplifier U d circuit is used to avoid loading effects. The second stage with resistor R g and capacitance C b connected op amp U e The circuit is an integrator. An inverting proportional amplifier is connected between the second stage and the third stage to realize output polarity inversion. Level 3 with R j , R k and R l connected op amp U g The circuit is a current inversion circuit.

[0069] The parameter values of each component in the circuit are respectively set as:

[0070] R f =750kΩ, R g = 632kΩ, R h = R i = 10kΩ, R j =83.3kΩ, R k =R l = 2 kΩ.

[0071] The analog multiplier adopts the model AD633JN device, the op...

Embodiment 3

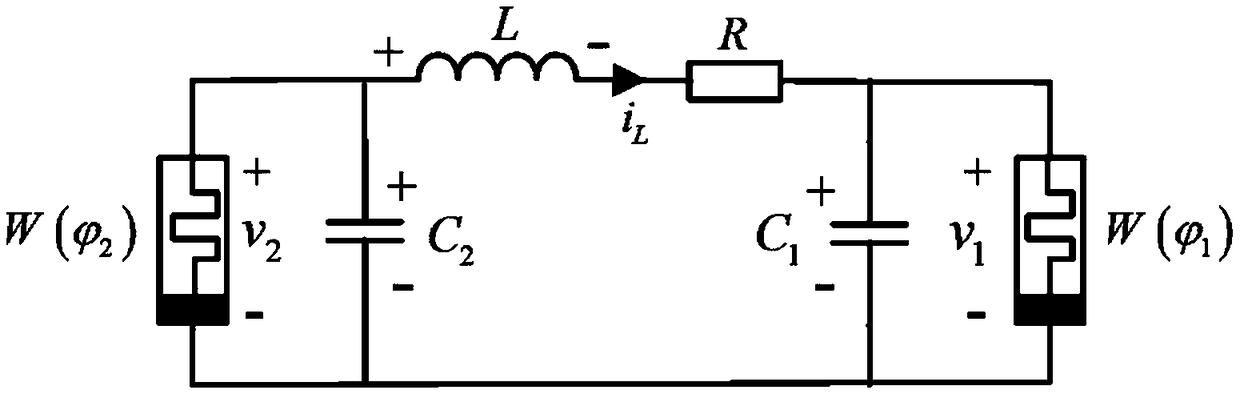

[0072] Example 3: Numerical analysis of heterogeneous magnetron memristor chaotic system.

[0073] Select circuit parameters for equation (8) so that α=9, β=9, γ=5, R=0.1, ie c 1 =0.11,c 2 =0.11, L=0.2 and a=-1.2, b=3, c=0.9, d=2.7, then equation (8) becomes

[0074]

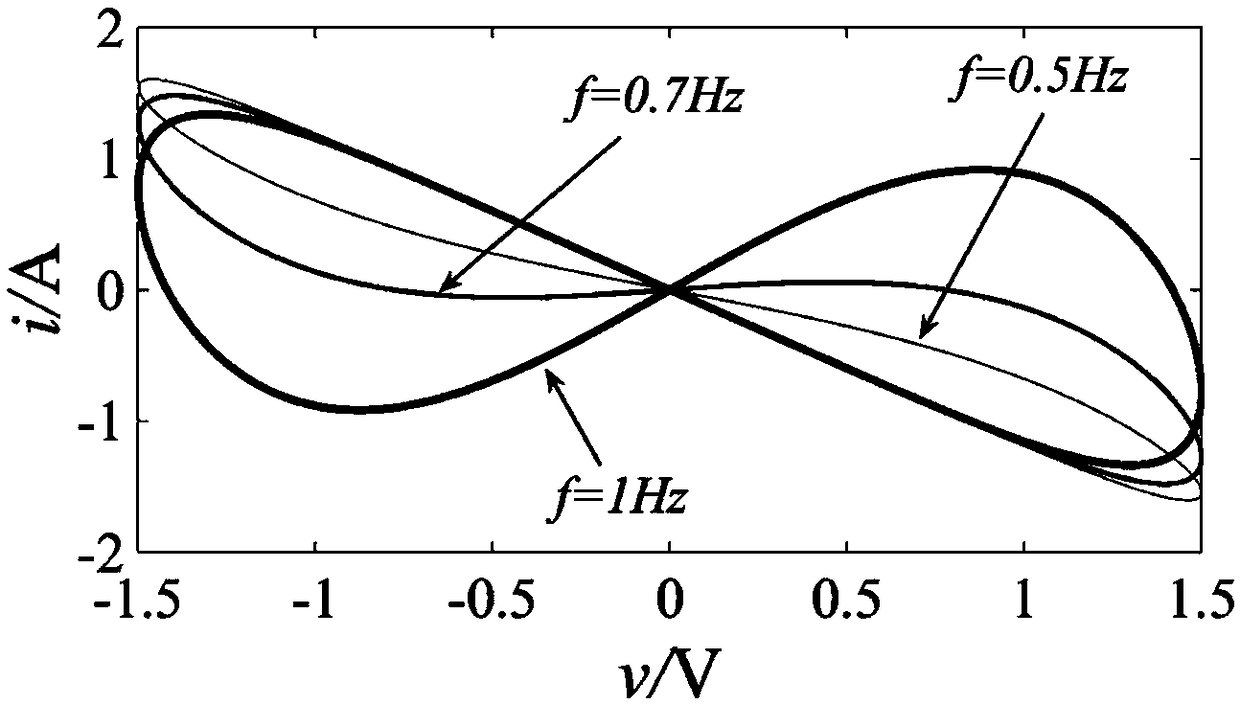

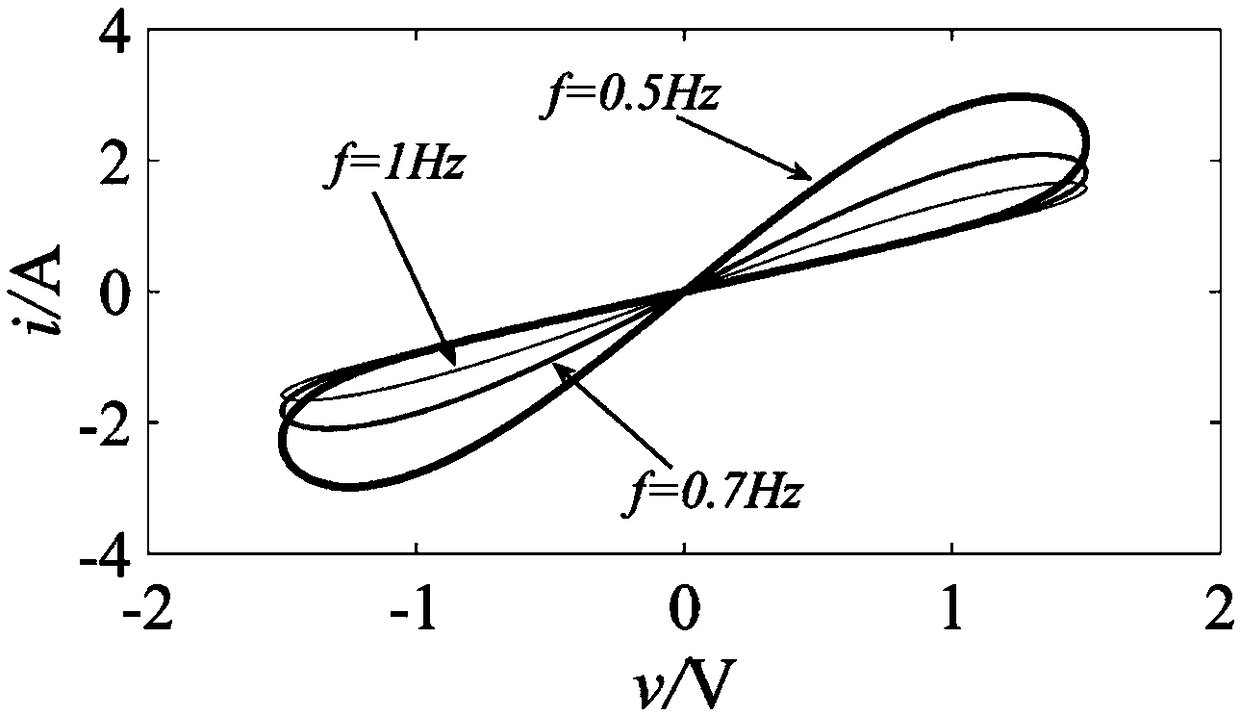

[0075] For the initial conditions of (0.001,0.01,0,0,0), the system (14) generates a double-scroll chaotic attractor, and its two-dimensional trajectory waveform on the phase plane is as follows Figure 4 shown.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More