Patents

Literature

62 results about "Memristor circuits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

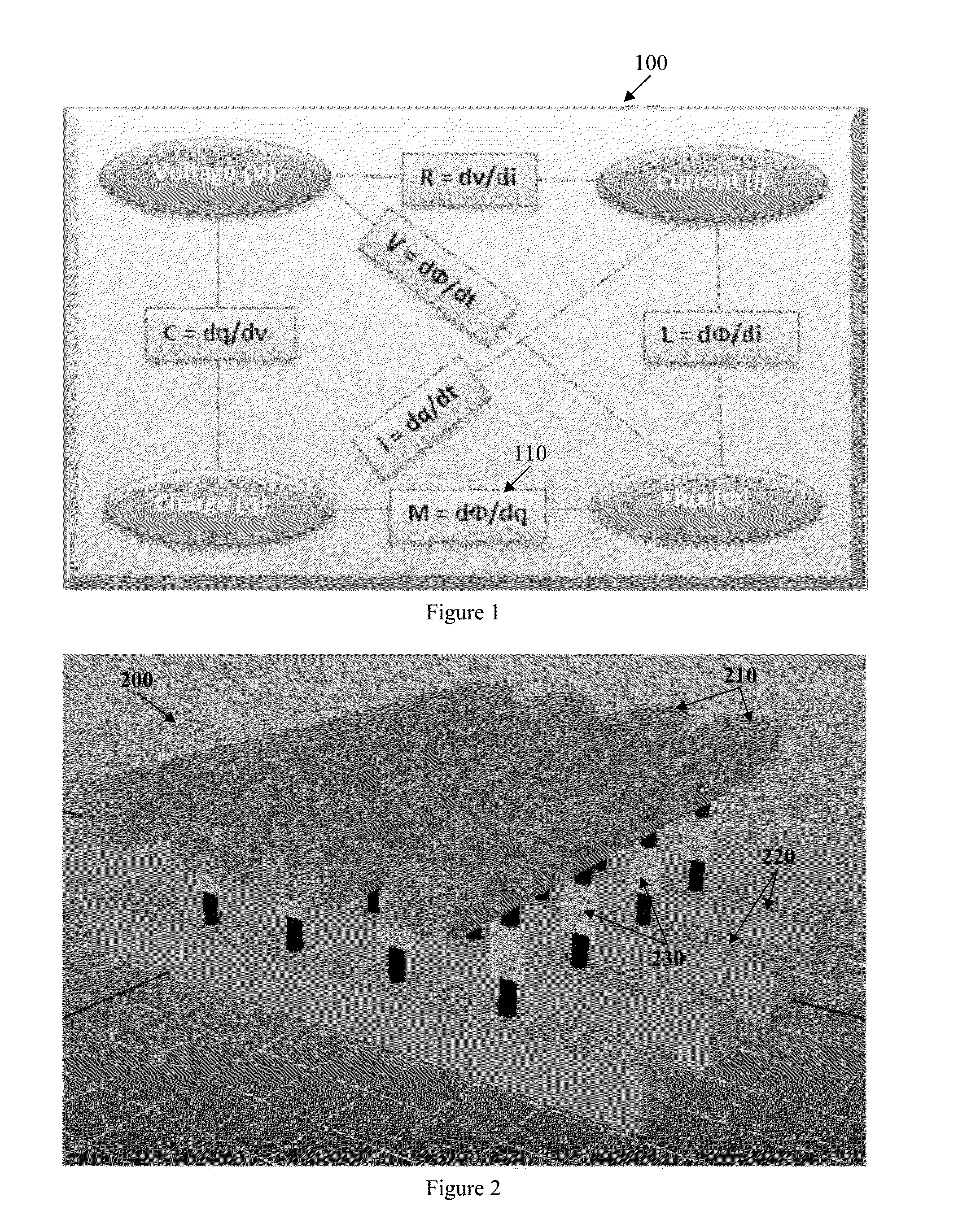

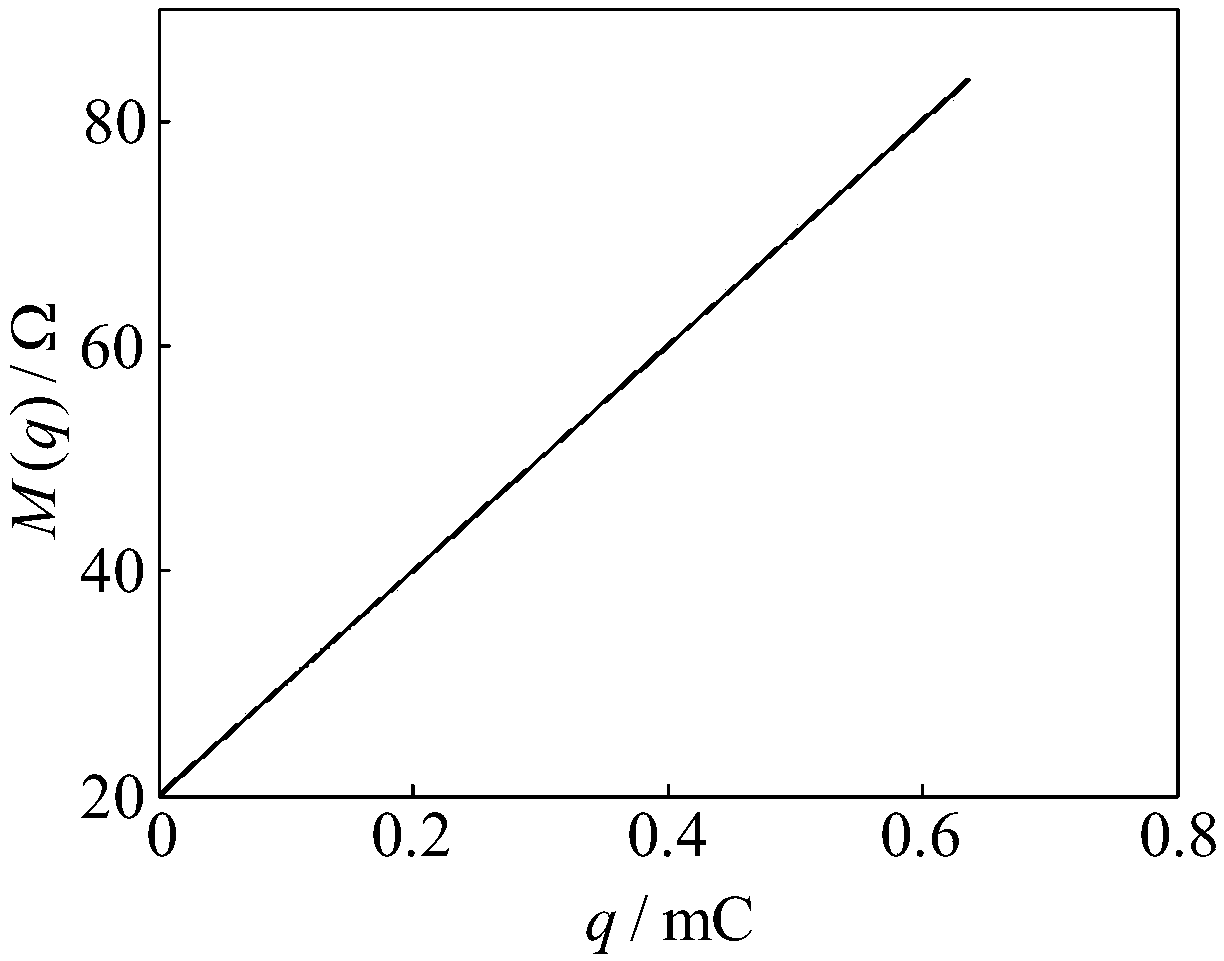

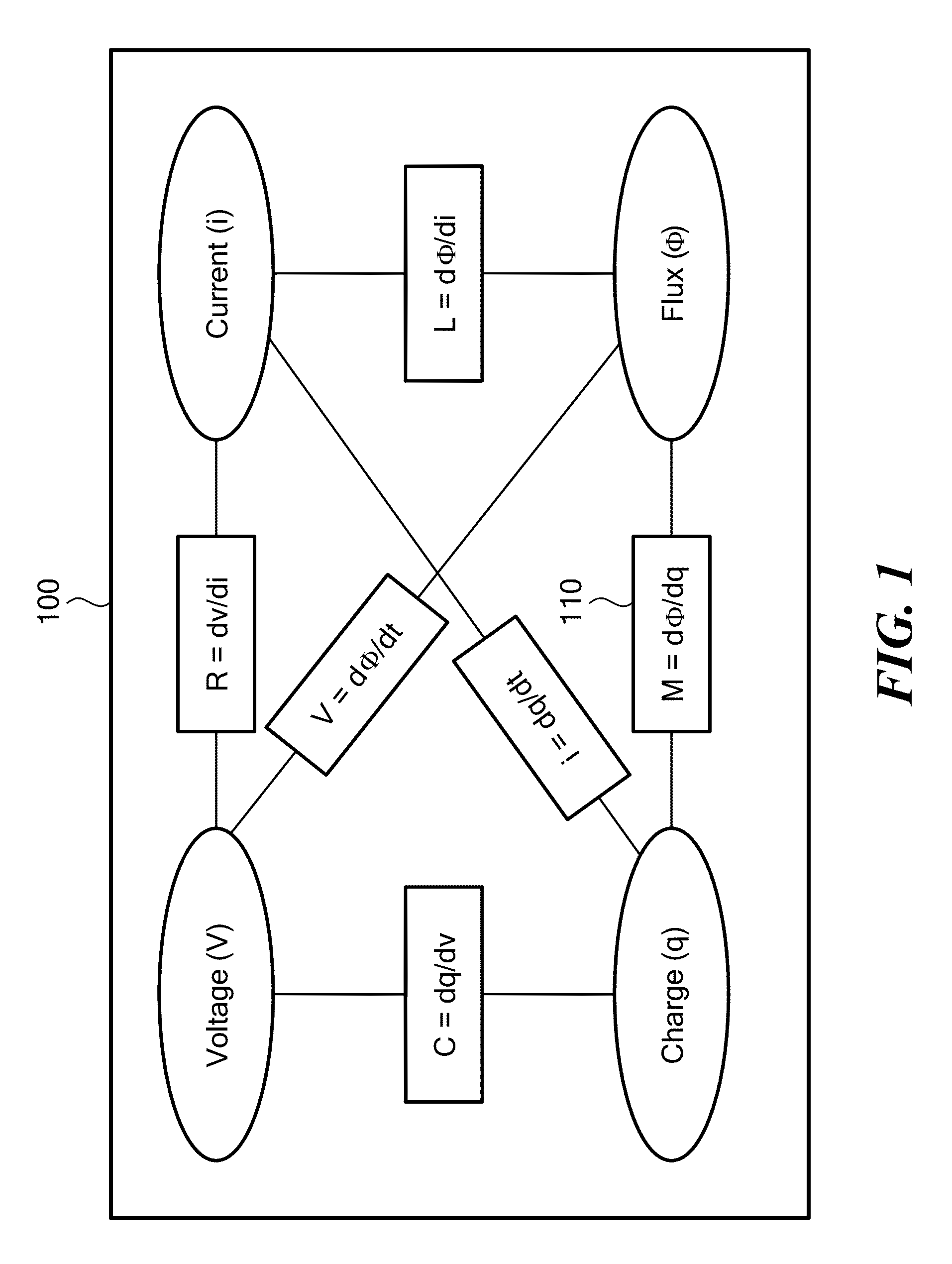

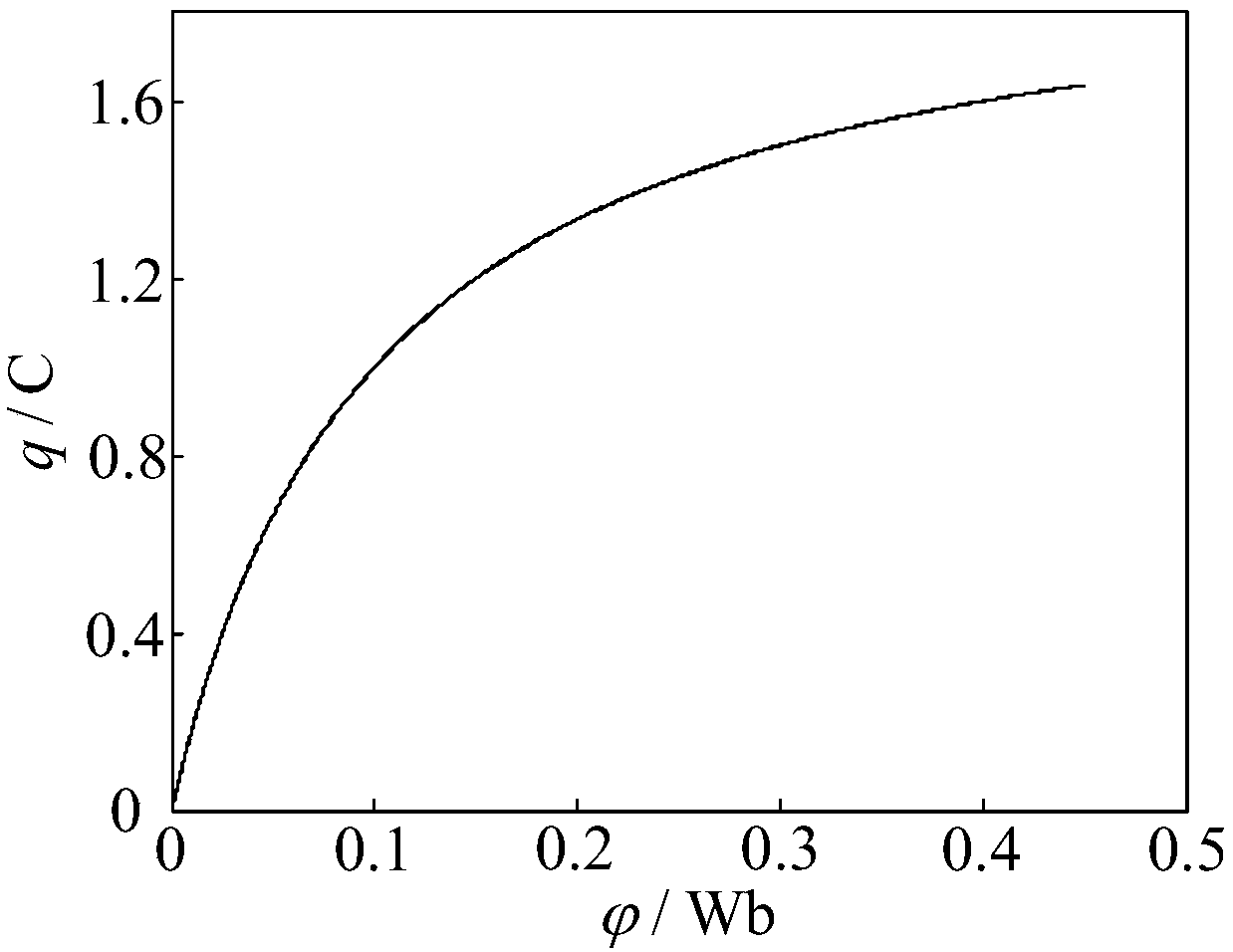

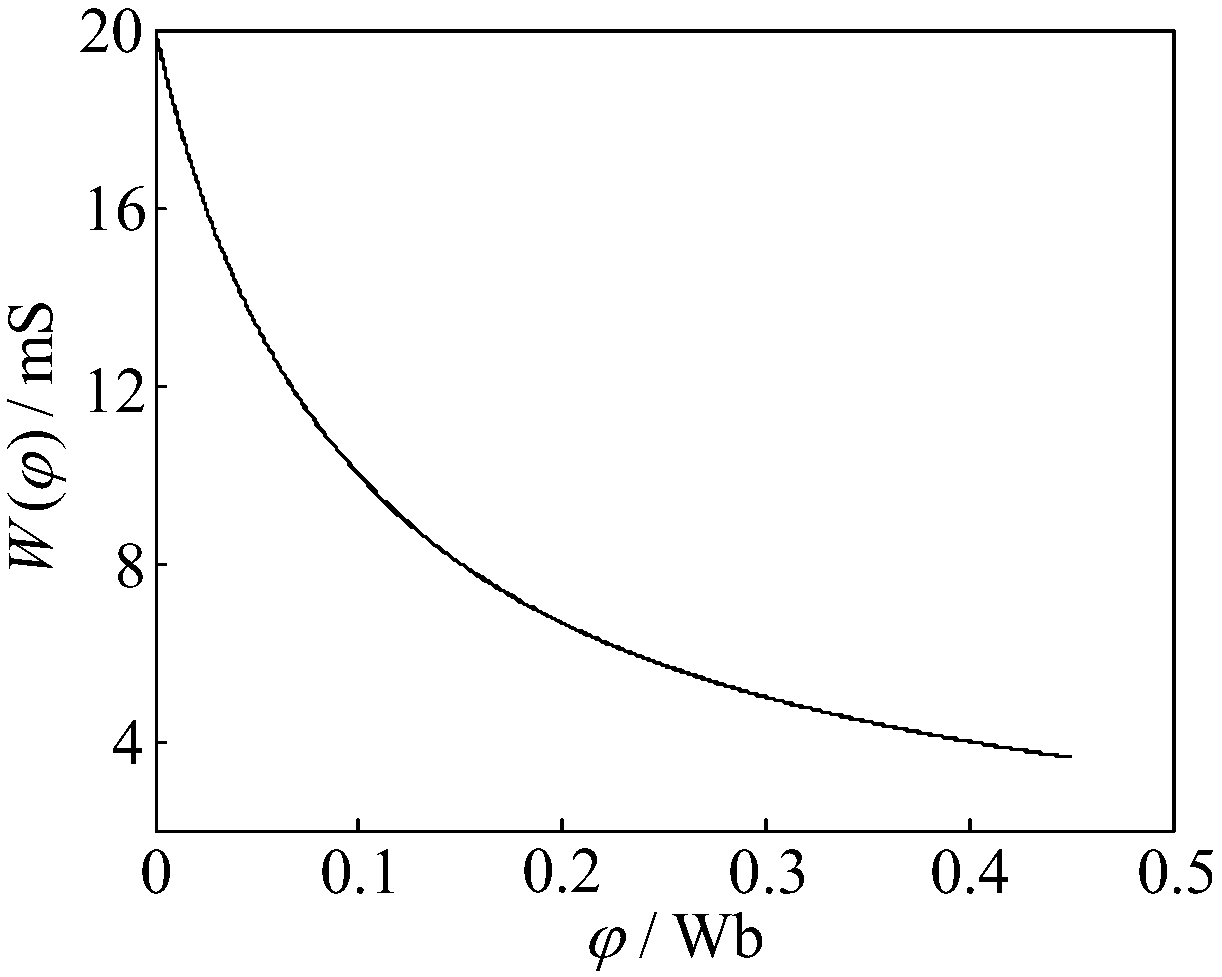

Memristor is the contraction of memory resistor which is a passive device that provides a functional relation between charge and flux. It is a two-terminal circuit element in which the flux between the two terminals is a function of the amount of electric charge that has passed through the device [1].

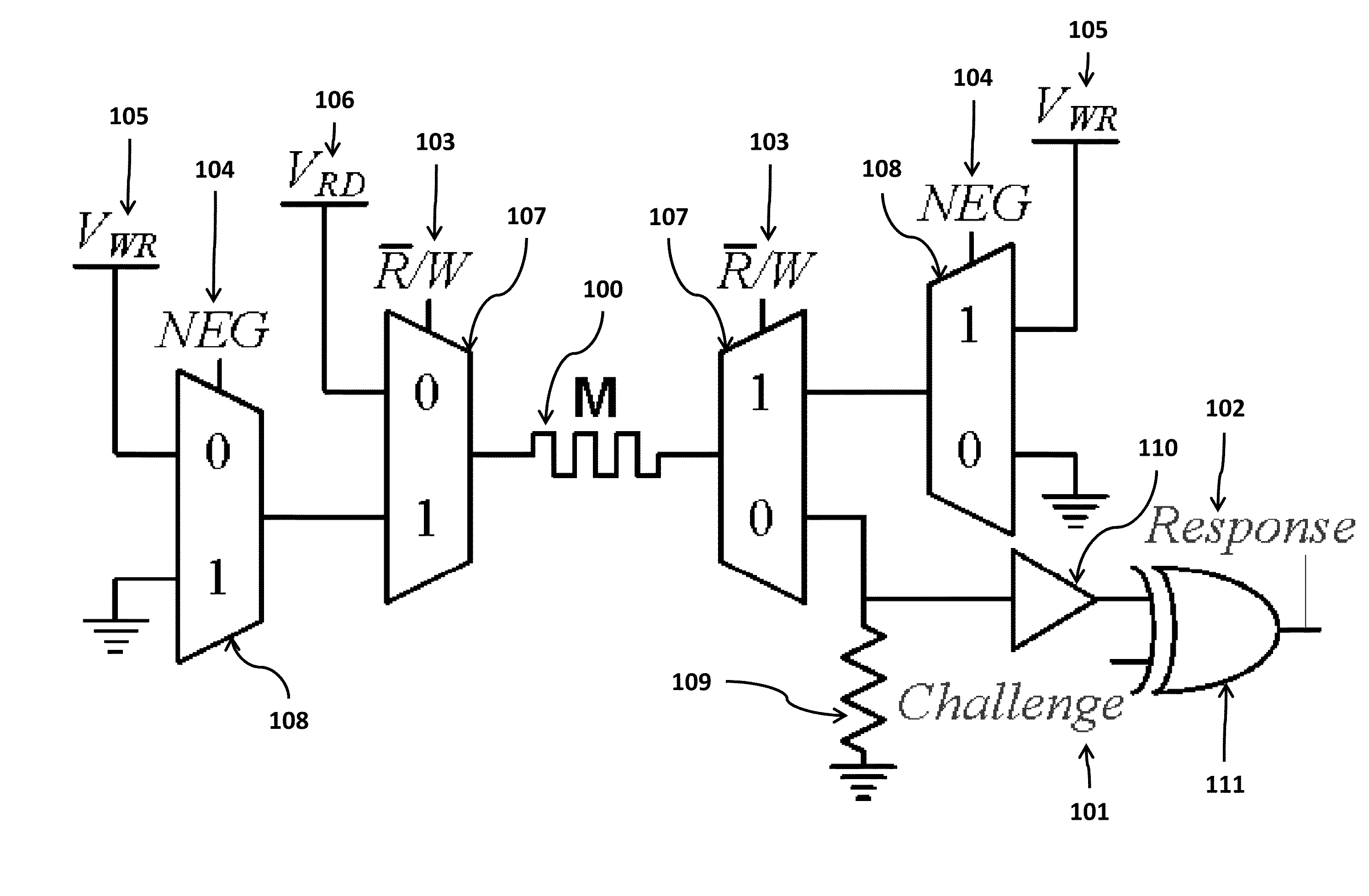

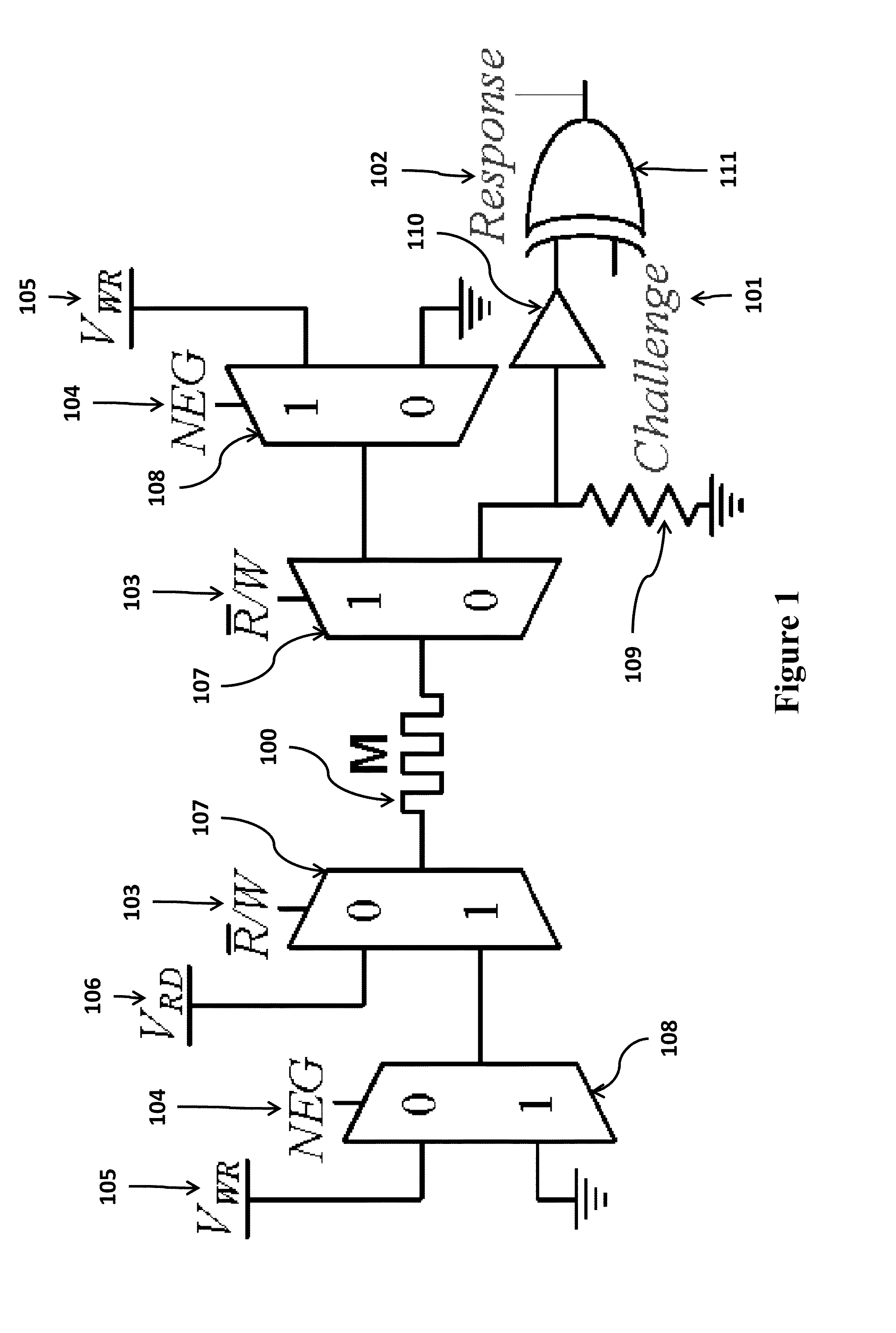

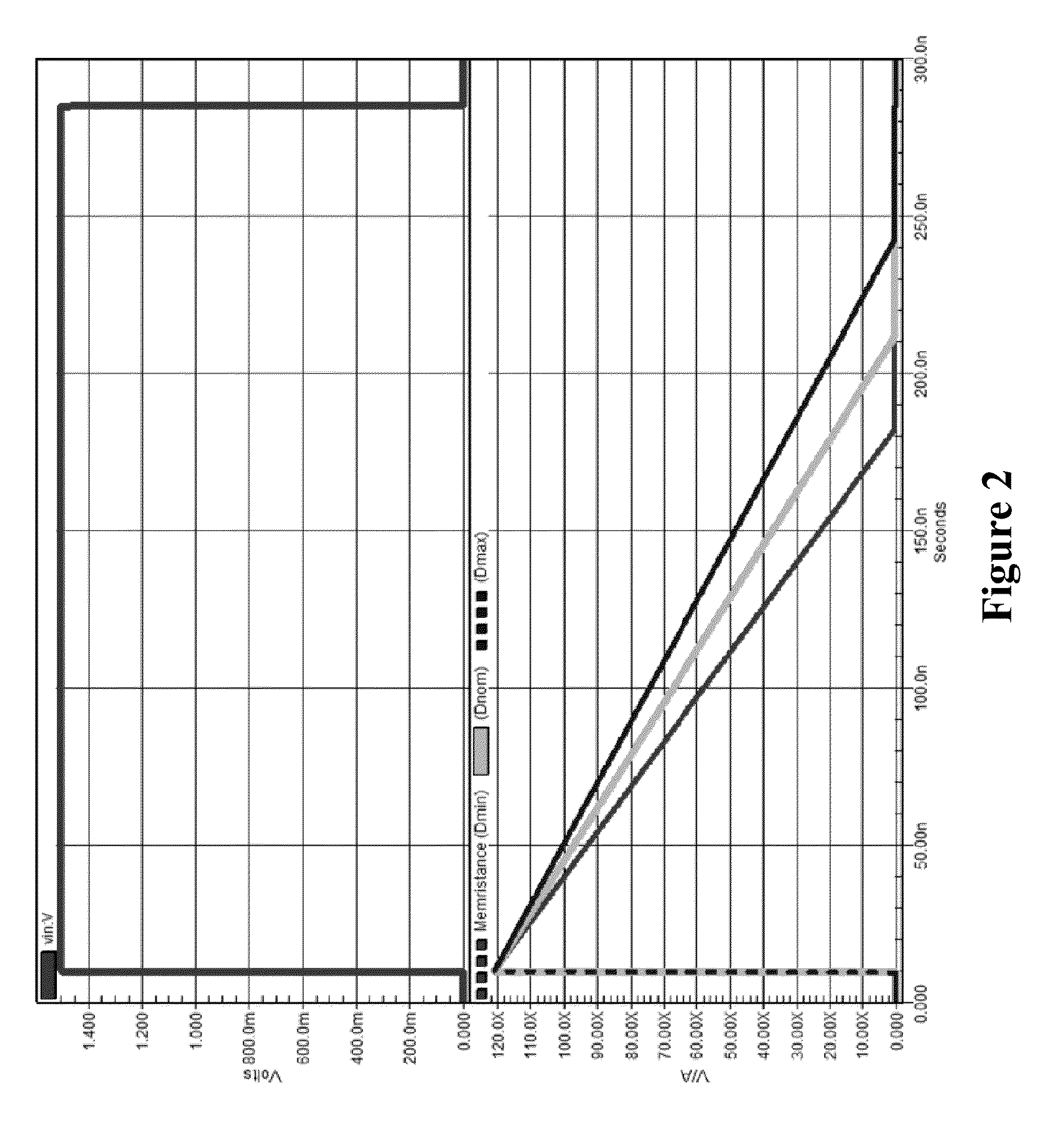

Write-Time Based Memristive Physical Unclonable Function

InactiveUS20140268994A1High resistance stateDigital storageInternal/peripheral component protectionHigh resistancePhysical unclonable function

A physical unclonable function (PUF) device consisting of a hybrid CMOS-memristor circuit that leverages variations in the required write-time of a memristor. Variations in the time required to write, or SET, a memristor from a high to low resistance state arise from variability in physical parameters such as the memristor thickness. When applying a SET voltage across the memristor for the nominal minimum SET time, variability leads to a situation where the memristor will actually SET to the low resistance state only 50% of the time. When the device does not SET it will remain in the high resistance state. Since the to resistance state of the memristor corresponds to reading either a logic 1 or logic 0 on the output of the circuit, the write-time based memristive PUF produces a digital signature directly corresponding to the fabrication process-induced physical variations of an integrated circuit.

Owner:BY THE SEC OF THE AIR FORCE UNITED STATES OF AMERICA AS REPRESENTED

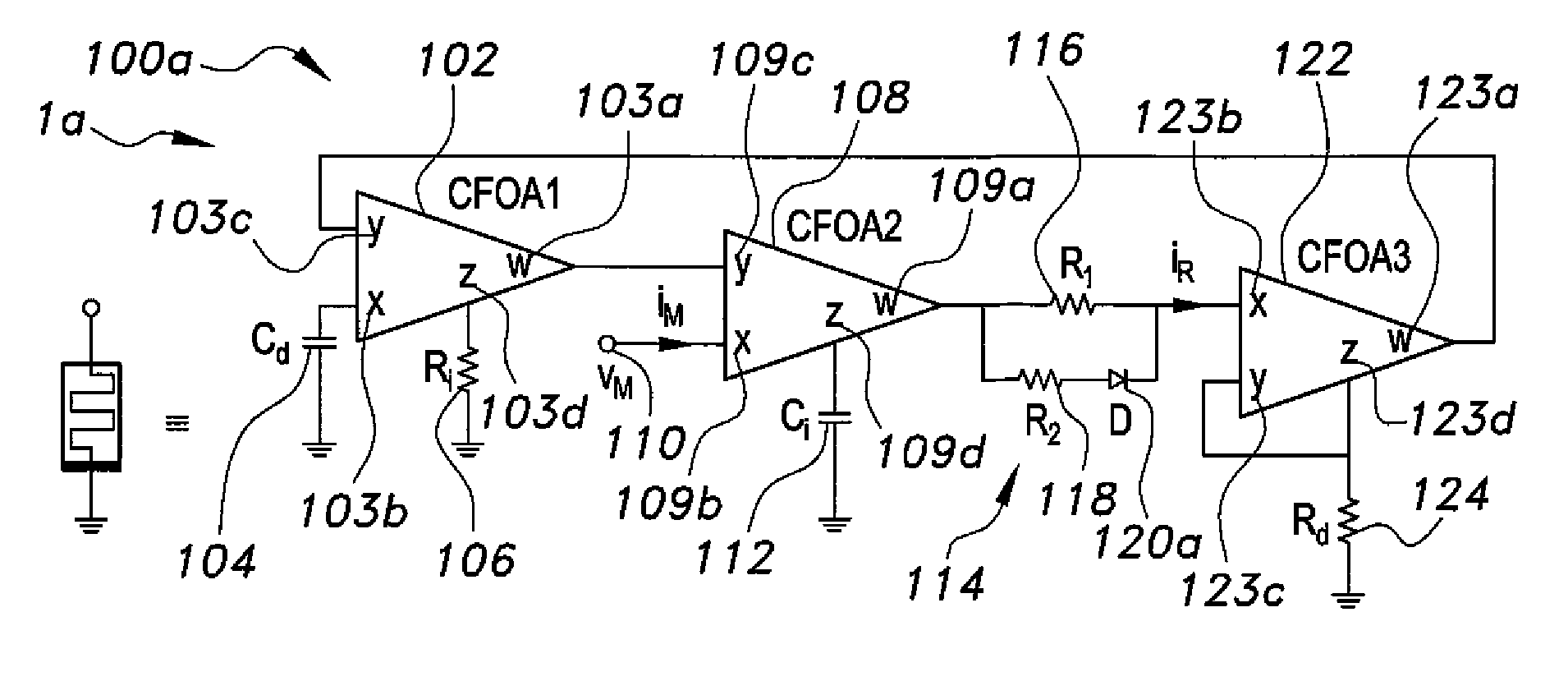

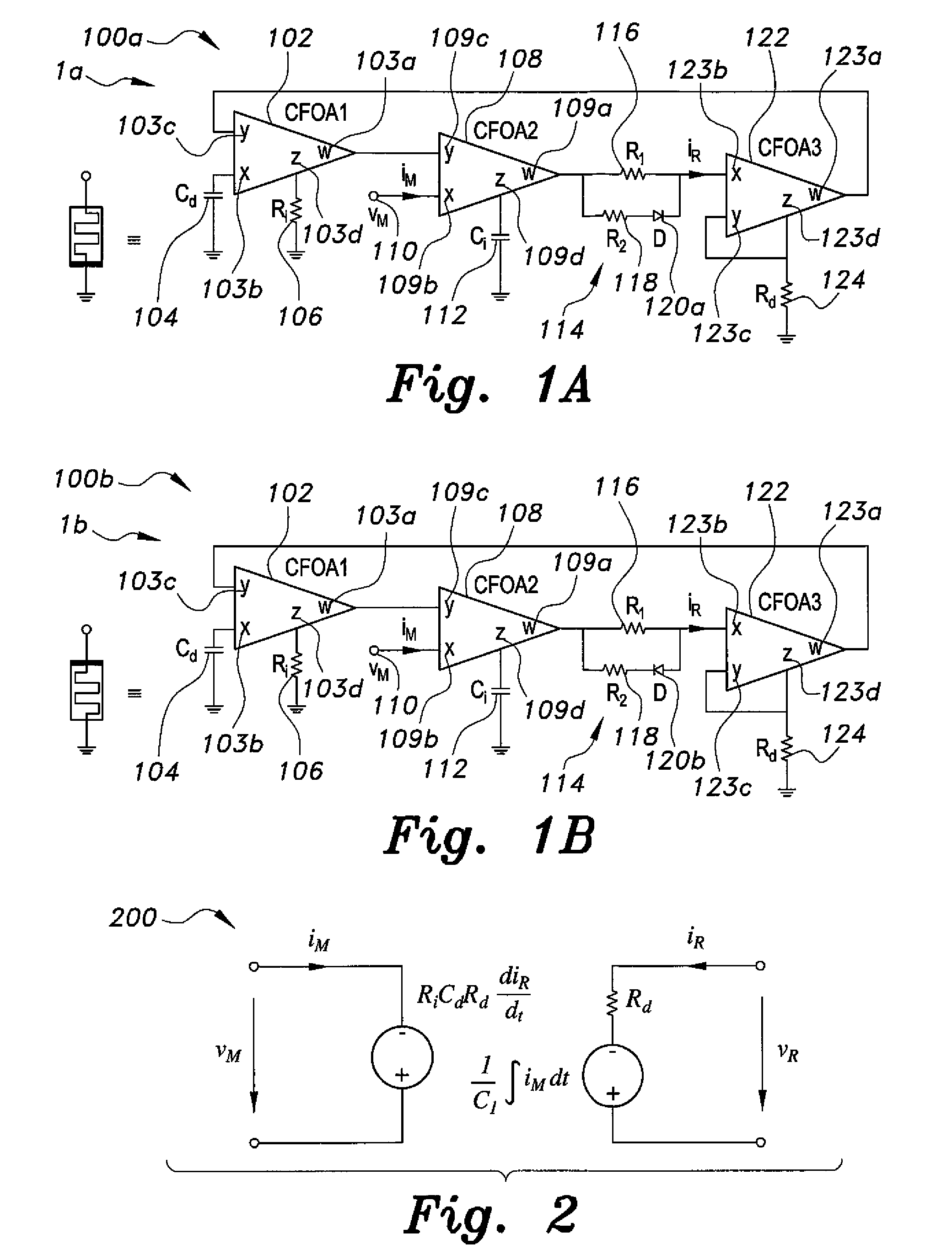

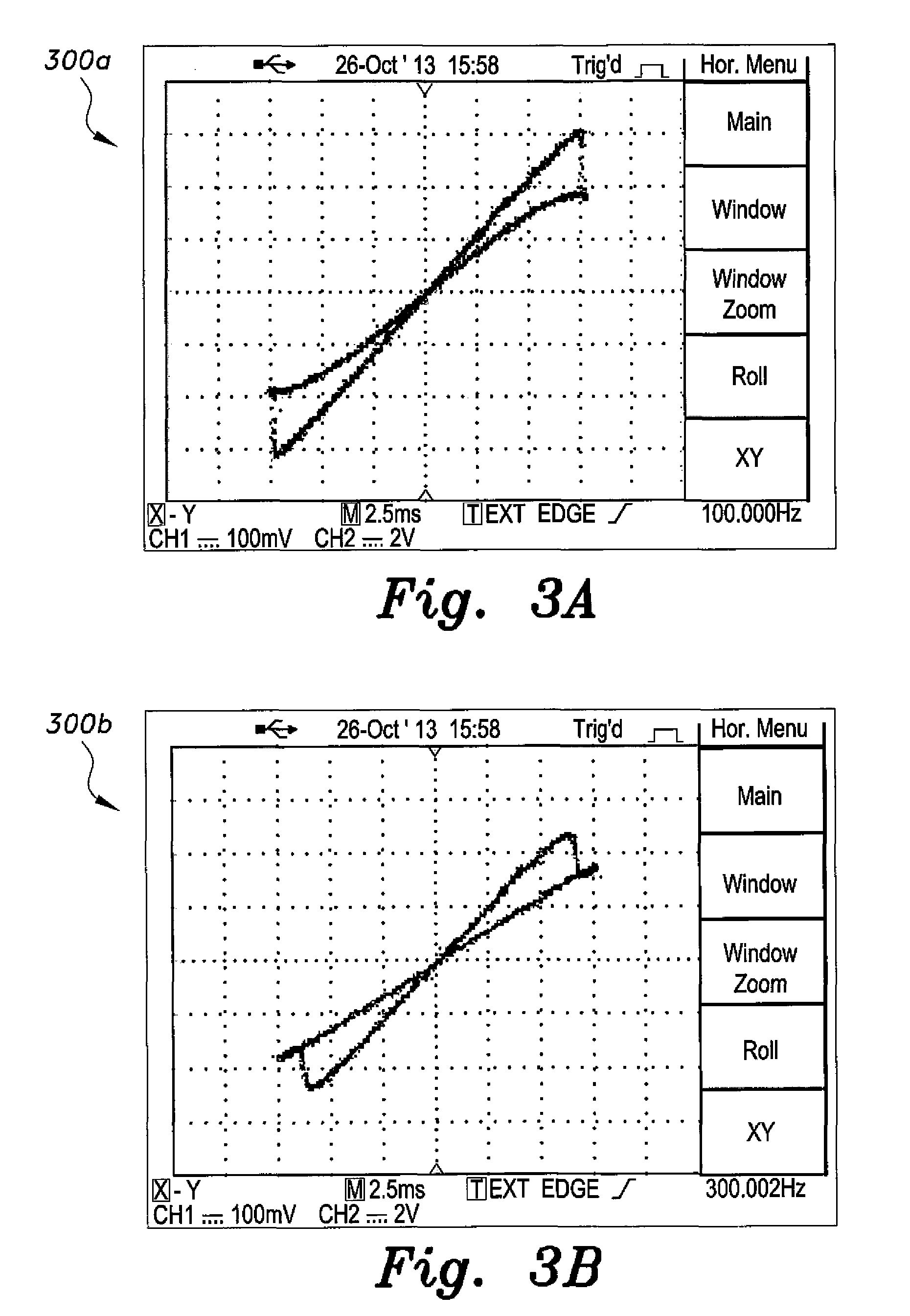

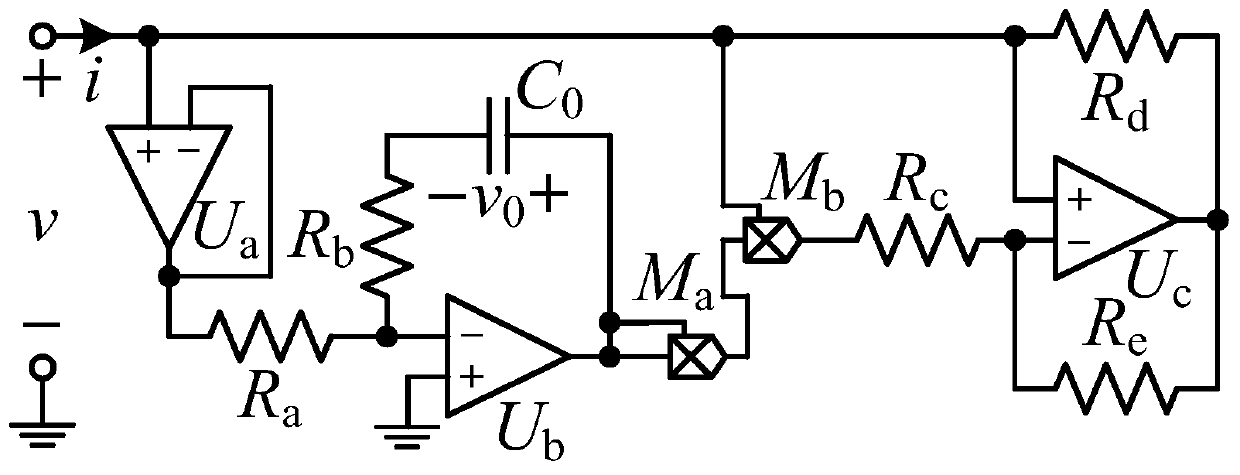

Memristor-based emulator for use in digital modulation

InactiveUS9019030B1Readily apparentDigital computer detailsBiological neural network modelsNonlinear resistorAudio power amplifier

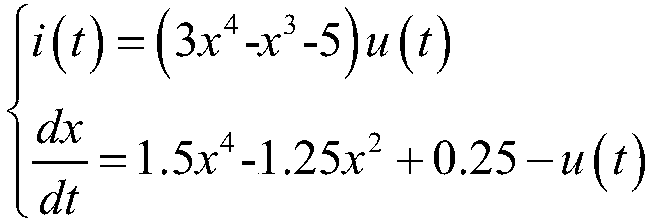

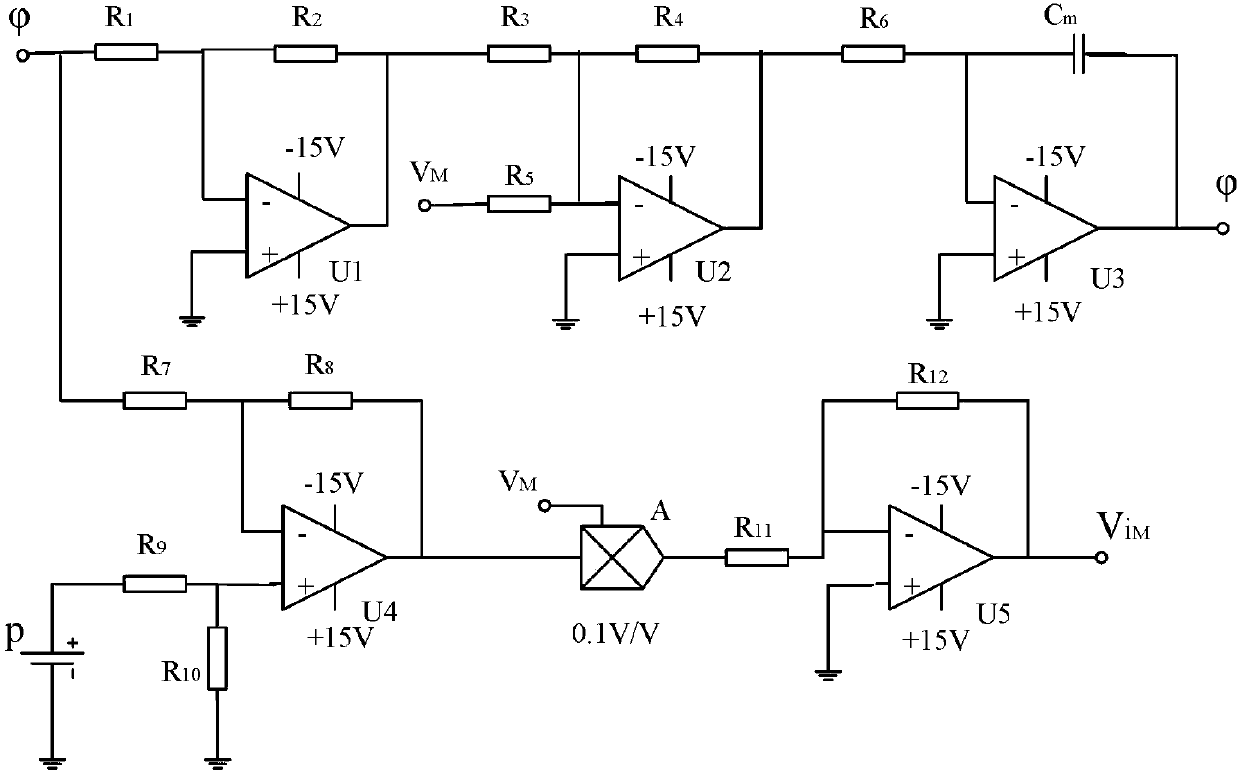

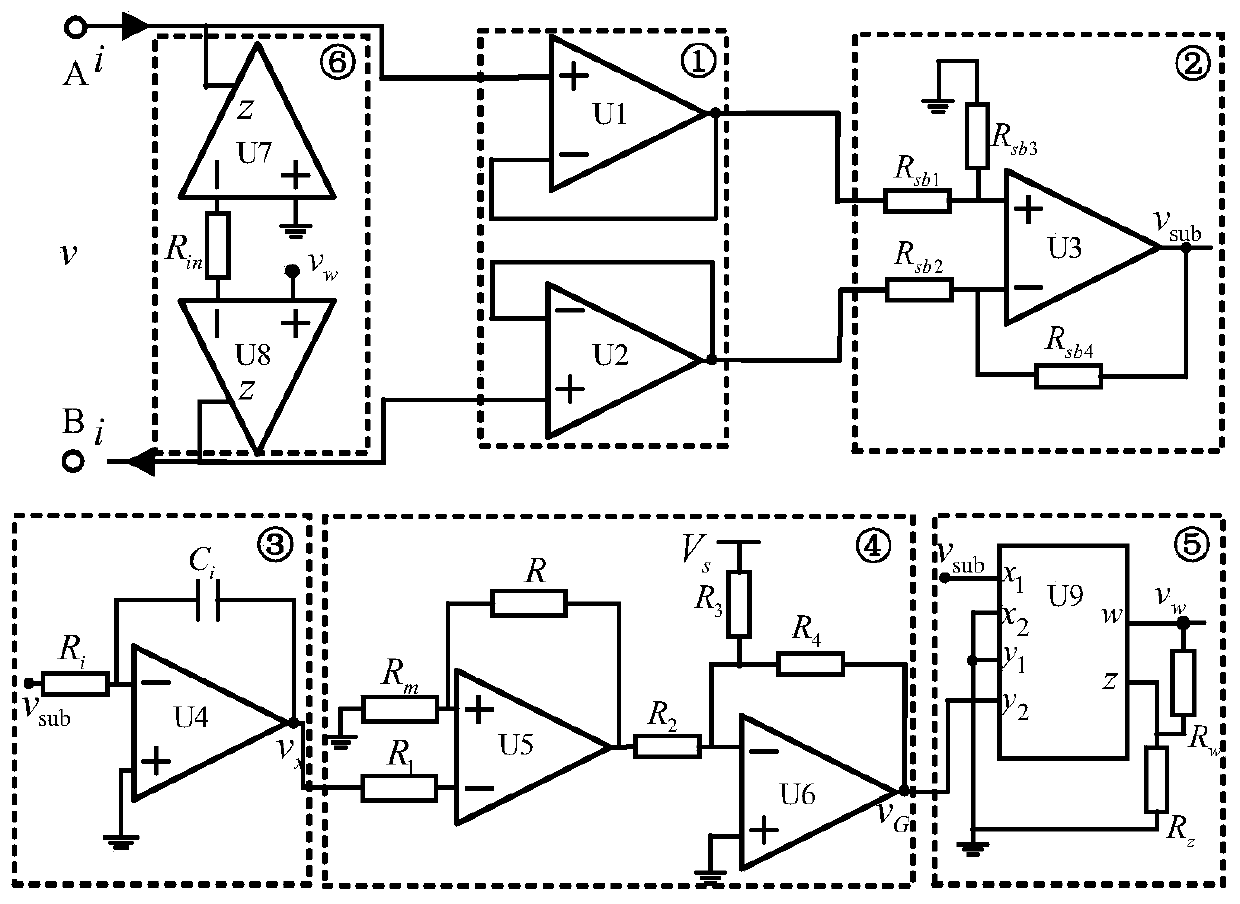

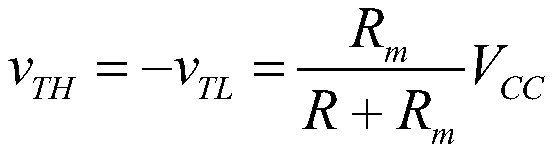

A memristor-based emulator including a memristor circuit for use in digital modulation that includes a first current feedback operational amplifier (CFOA) having multiple terminals in communication with a capacitor Cd and in further communication with a resistor Ri. A second CFOA having multiple terminals is in communication with the first CFOA and is adapted to be in further communication with a voltage vM to provide an input current iM for integration by a capacitor Ci. A nonlinear resistor is in communication with the second CFOA. A third CFOA having multiple terminals is in communication with the nonlinear resistor and is in further communication with the first CFOA and a resistor Rd. The third CFOA and the resistor Rd act as an inverting amplifier associated with the nonlinear resistor to increase a current gain to increase a difference between ON and OFF values of a resistance of a realized memristor.

Owner:KING FAHD UNIVERSITY OF PETROLEUM AND MINERALS

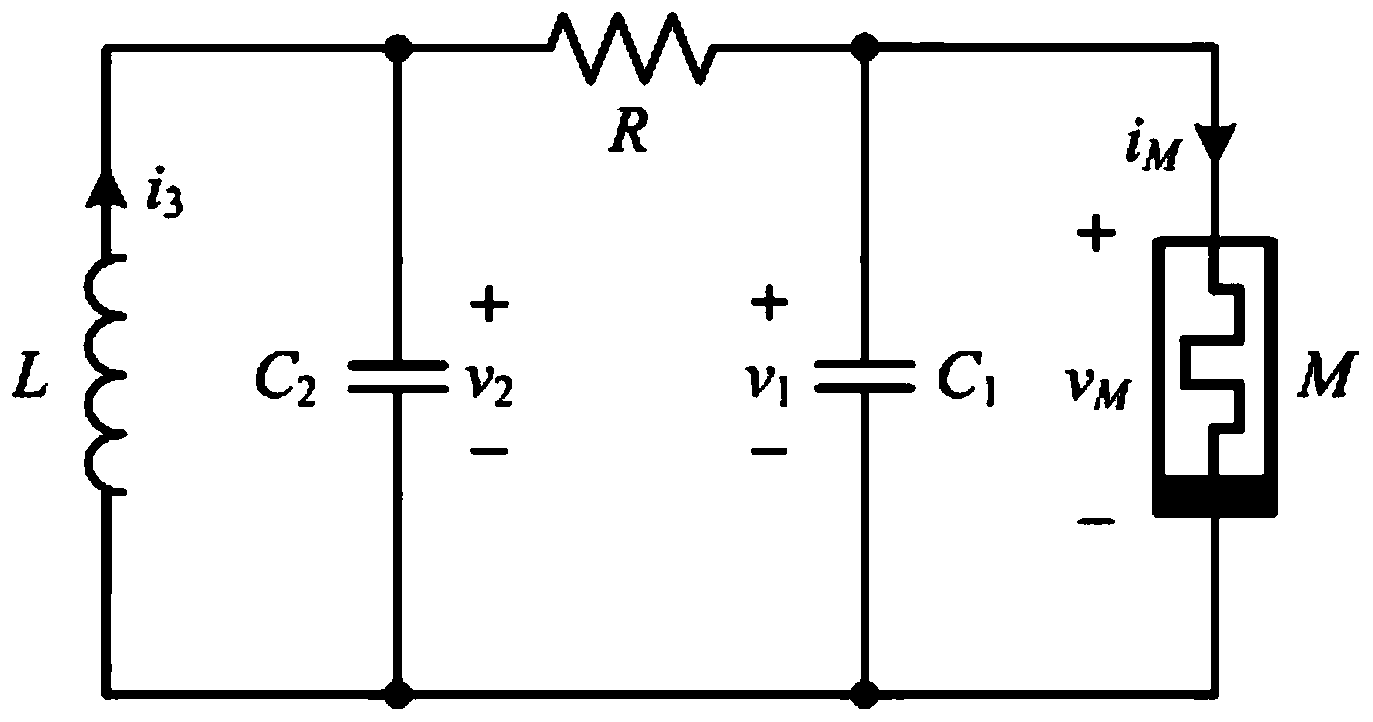

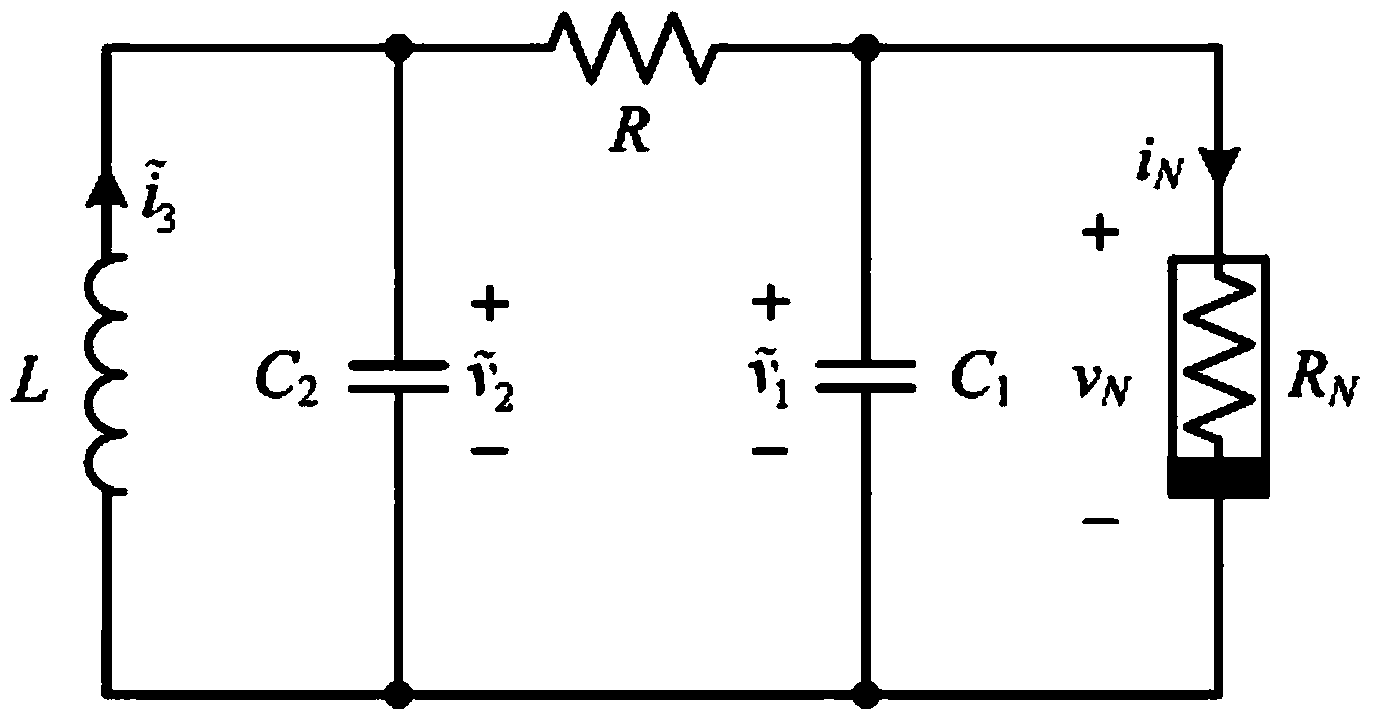

Switchable chaotic signal source by memristor circuit and nonlinear circuit

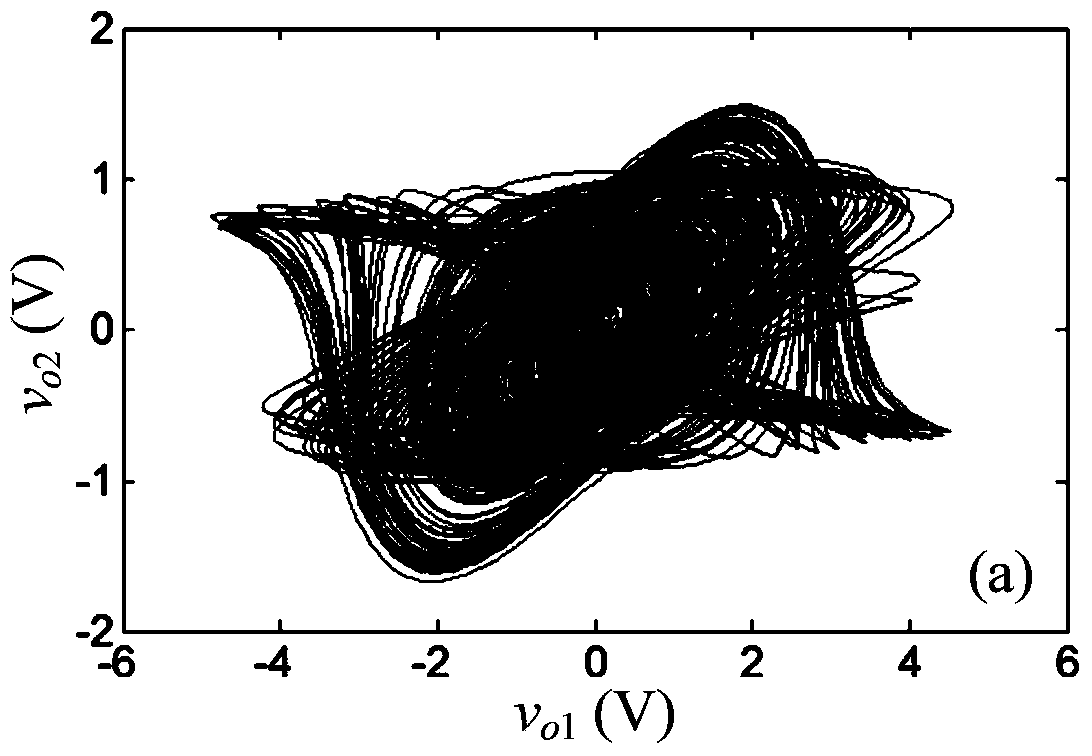

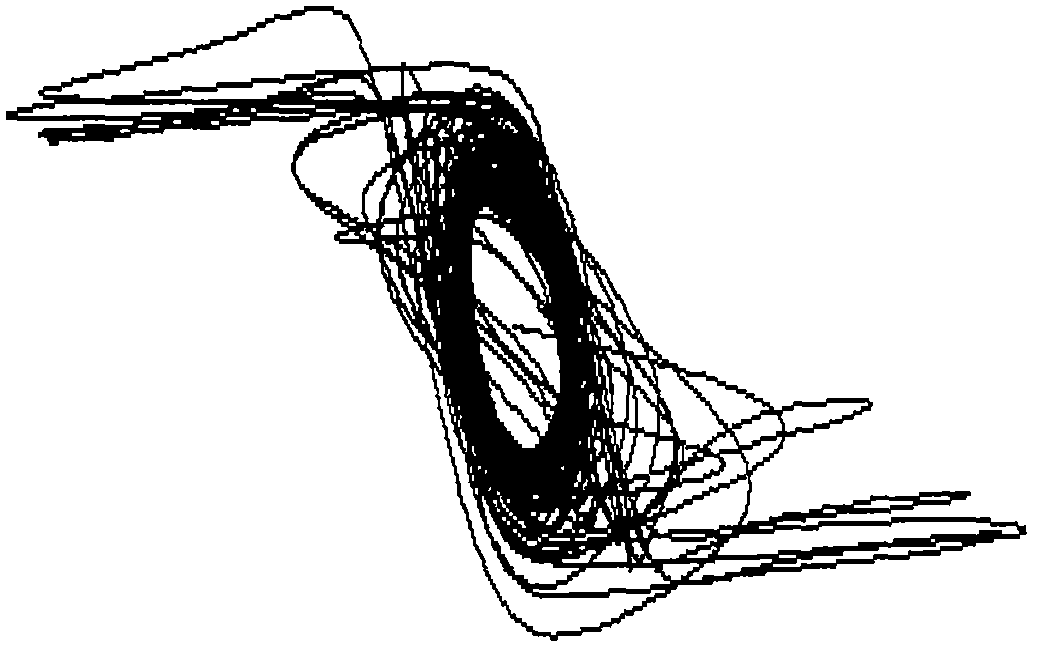

The invention relates to a switchable chaotic analog circuit based on a Chua chaotic circuit system. The switchable chaotic signal source by a memristor circuit and a nonlinear circuit comprises a Chua chaotic circuit post-stage switchable-mode main circuit which is composed of an integrating circuit, a control switch circuit (S) arranged at the post stage of the integrating circuit, an absolute value function circuit (H(.)) disposed at the post stage of the control switch circuit (S), a first multiplying circuit (M1) mounted at the post stage of the absolute value function circuit (H(.)) and a negative resistance circuit arranged at the post stage of the first multiplying circuit (M1). The chaotic analog circuit has characteristics of simple circuit structure and strong implementability. In addition, switching of chaotic signals can be realized by the memristor circuit and the nonlinear circuit. Meanwhile, chaotic systems capable of generating two types of different charotic attractors and complex chaotic scrolls both show complex dynamic characteristics and become a novel chaotic signal source.

Owner:溧阳常大技术转移中心有限公司

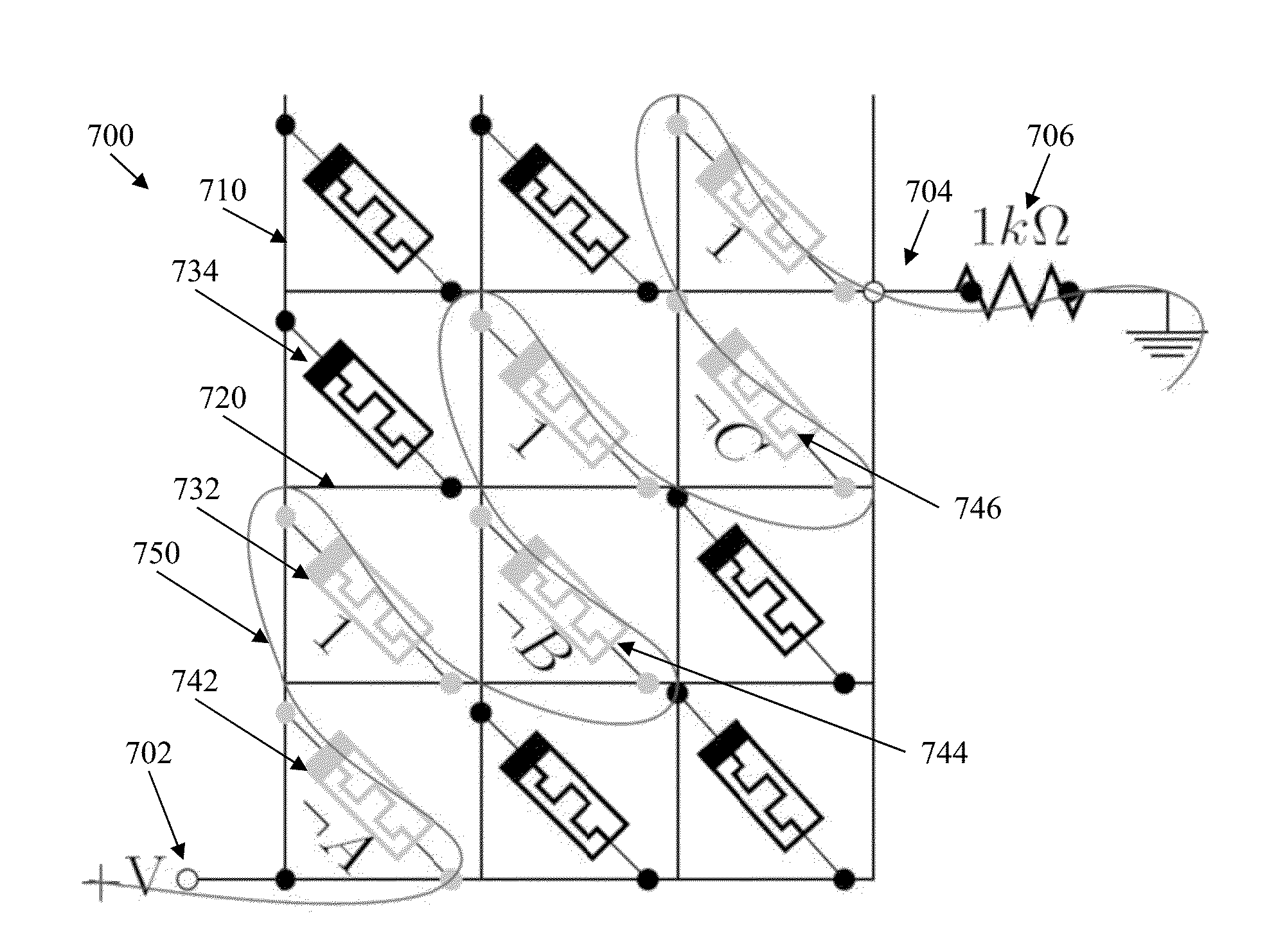

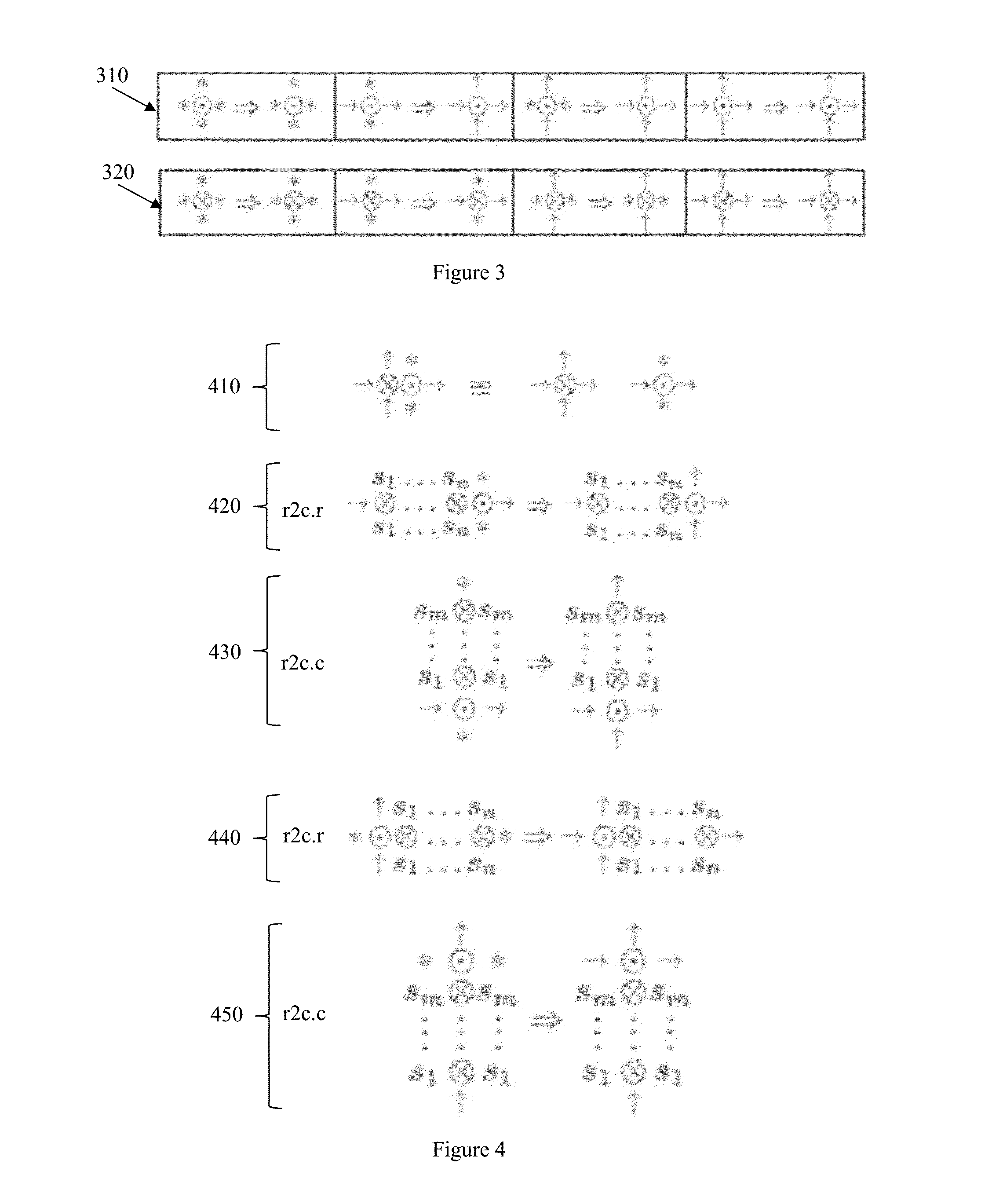

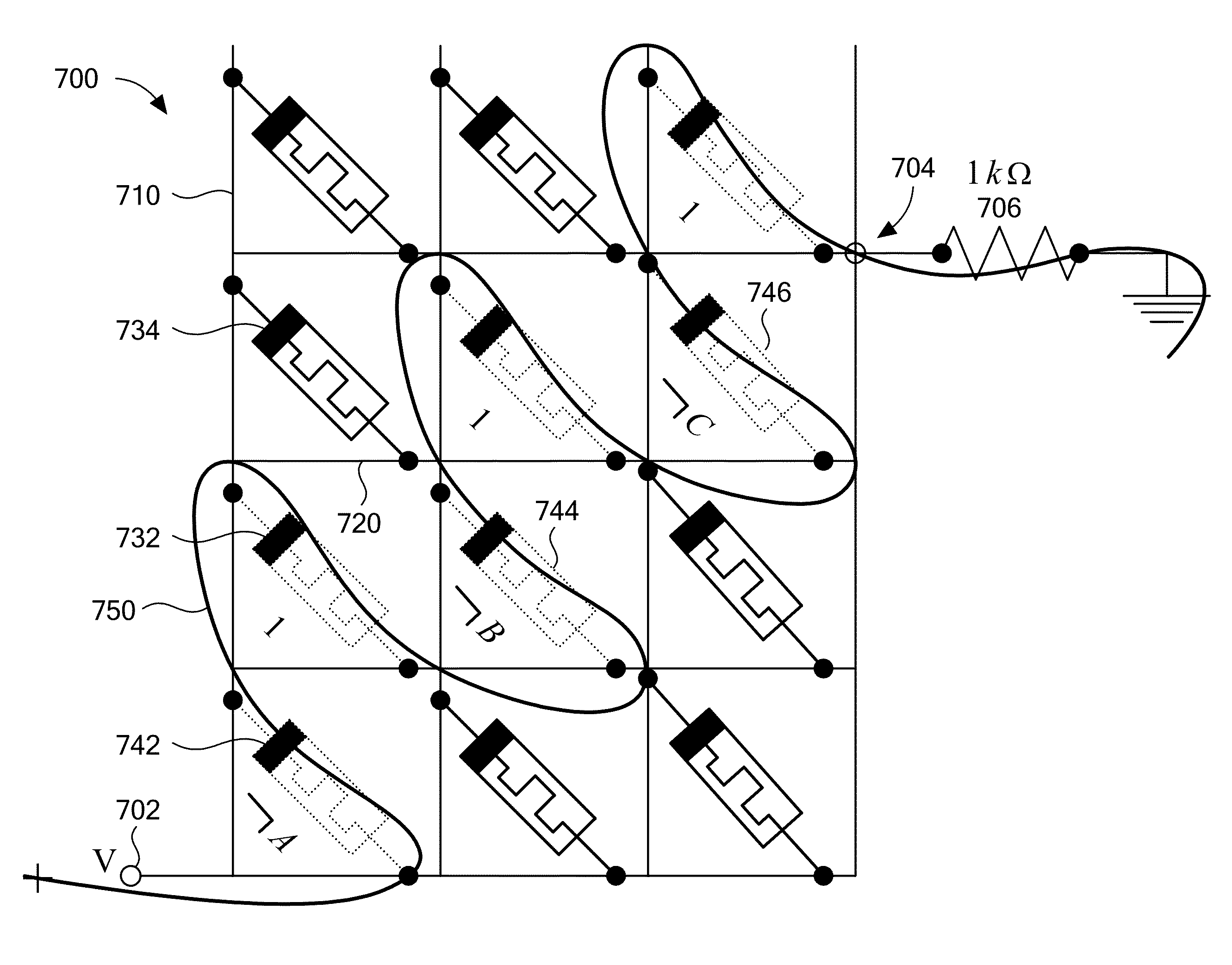

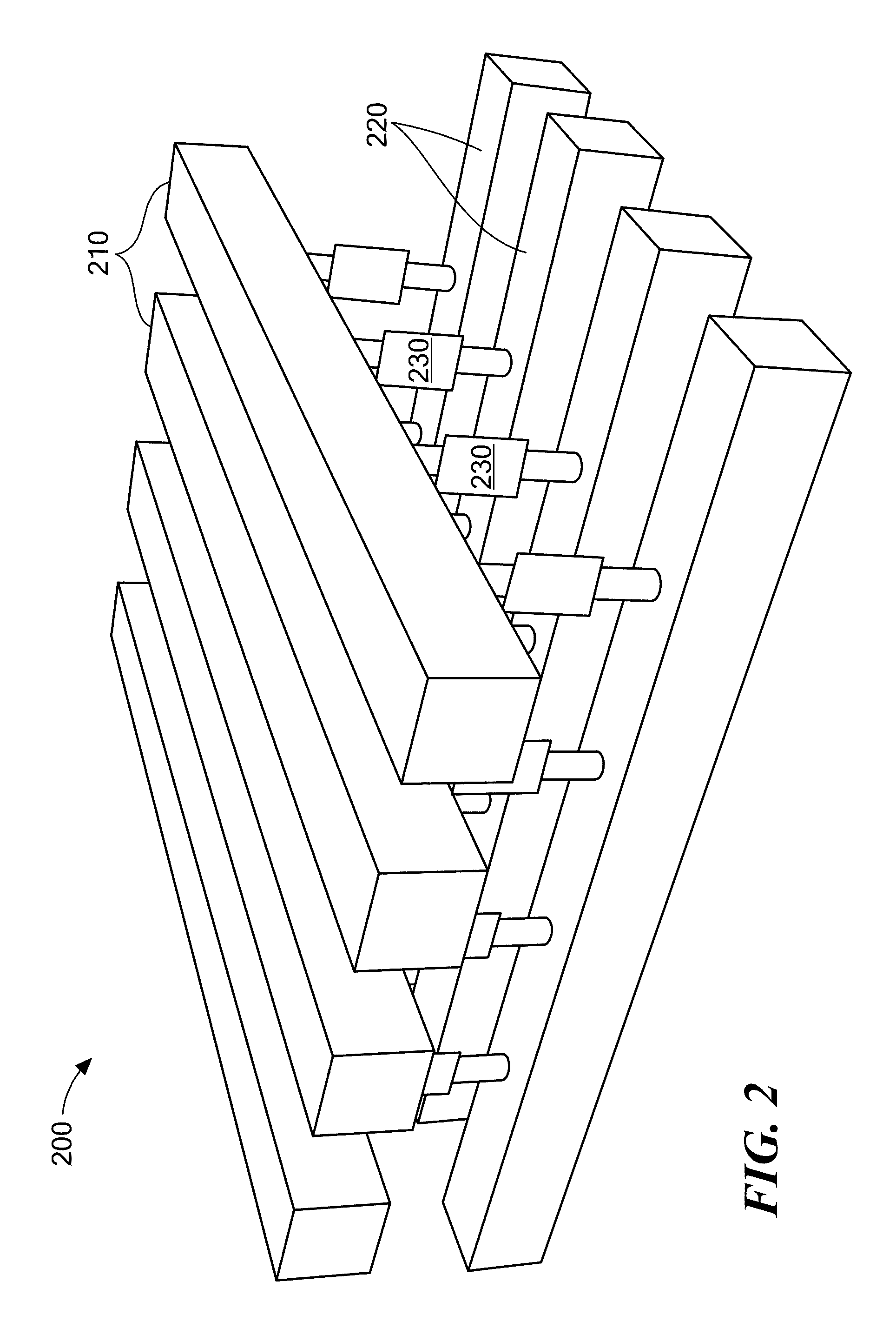

Computation of boolean formulas using sneak paths in crossbar computing

ActiveUS20150171868A1Programmable logic circuit arrangementsLogic circuits using semiconductor devicesGeneral purposeTheoretical computer science

Memristor-based nano-crossbar computing is a revolutionary computing paradigm that does away with the traditional Von Neumann architectural separation of memory and computation units. The computation of Boolean formulas using memristor circuits has been a subject of several recent investigations. Crossbar computing, in general, has also been a topic of active interest, but sneak paths have posed a hurdle in the design of pervasive general-purpose crossbar computing paradigms. Various embodiments are disclosed which demonstrate that sneak paths in nano-crossbar computing can be exploited to design a Boolean-formula evaluation strategy. Such nano-crossbar designs are also an effective approach for synthesizing high performance customized arithmetic and logic circuits.

Owner:THE UNITED STATES OF AMERICA AS REPRESETNED BY THE SEC OF THE AIR FORCE +1

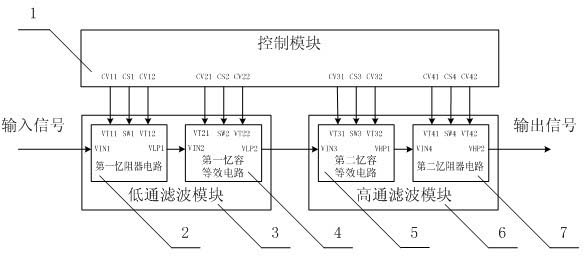

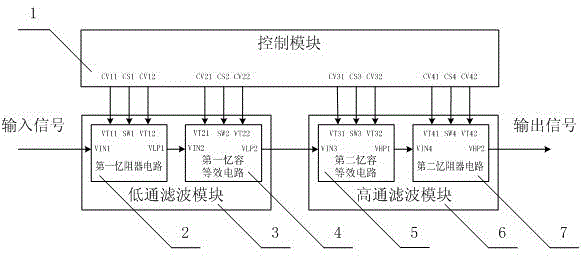

Band-pass filter based on memristor

The invention relates to a band-pass filter based on a memristor. The technical scheme is showed as that the filter comprises a control module (1), a low-pass filter module (3) and a high-pass filter module (6), wherein the low-pass filter module (3) is formed by connection of the output end VLP1 of a first memristor circuit (2) and the input end VIN2 of a first memcapacitor equivalent circuit (4); and the high-pass filter module (6) is formed by connection of the output end VHP1 of a second memcapacitor equivalent circuit (5) and the input end VIN4 of a second memristor circuit (7). The input end of the first memristor circuit (2), the input end of the first memcapacitor equivalent circuit (4), the input end of the second memcapacitor equivalent circuit (5) and the input end of the second memristor circuit (7) are correspondingly connected with the output ends of the control module (1). The input end VIN1 of the first memristor circuit (2) is externally connected with an input signal of a filter; and the output end of the second memristor circuit (7) is externally connected with an output signal of the filter. The band-pass filter provided by the invention has the characteristics of simplicity in structure, highness in precision, easiness to control and the like.

Owner:WUHAN UNIV OF SCI & TECH

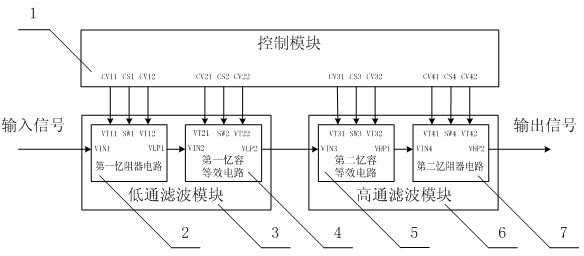

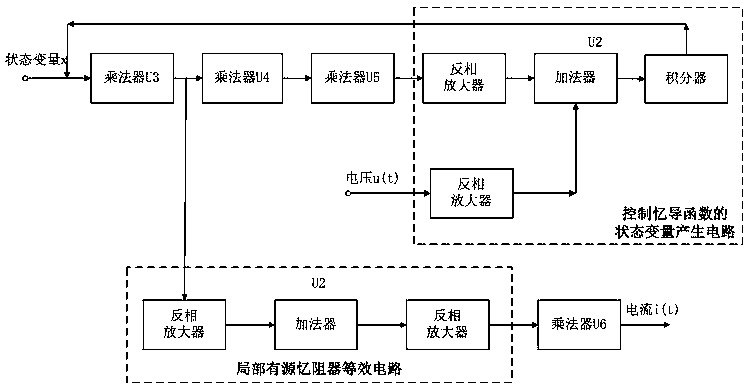

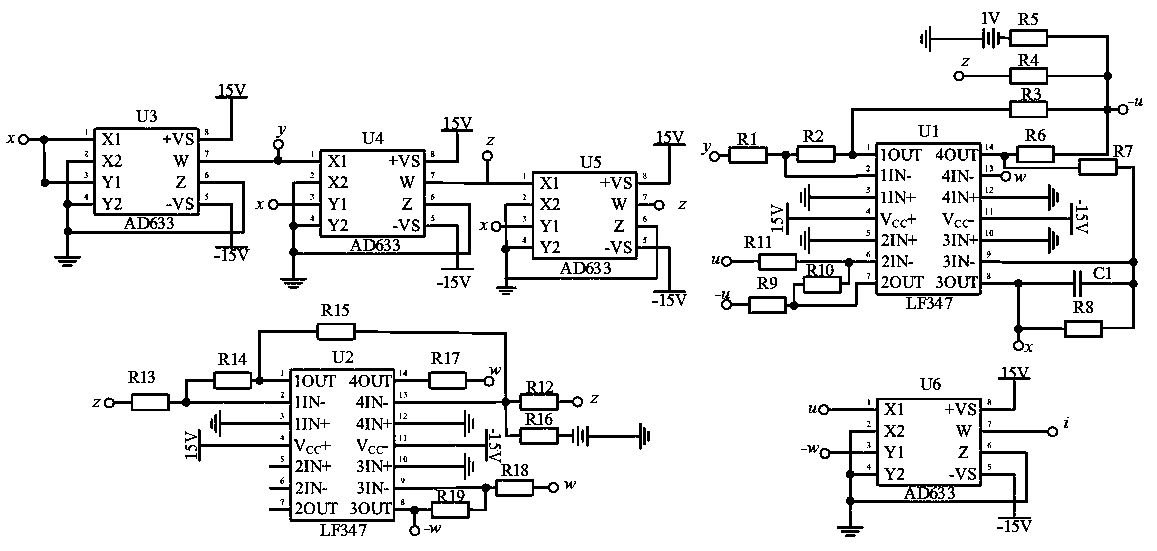

Fourth-order local active memristor circuit model

ActiveCN108846165ACAD circuit designSpecial data processing applicationsState variableCircuit models

The invention discloses a fourth-order local active memristor circuit model. The circuit model comprises an integrated operational amplifier U1, an integrated operational amplifier U2 and multipliersU3, U4, U5, U6. The integrated operational amplifier U1 and the multiplier U6 are respectively connected with the input end, i.e. the voltage and current test end of a local active memristor. The integrated operational amplifier U1 is used for implementing integration operation, summation operation and inversion operation and returning the output signal to the multiplier U3 so as to finally obtainthe state variable for controlling the memory value. The integrated operational amplifier U2 is used for implementing the inversion operation and addition operation so as to obtain the required memory control function. The multiplier U6 multiplies the memory control function and the input voltage so as to obtain the final memristor current. The model is used for simulating the volt-ampere characteristics of the local active memristor and replacing the actual local active memristor for experiment, application and research.

Owner:HANGZHOU DIANZI UNIV

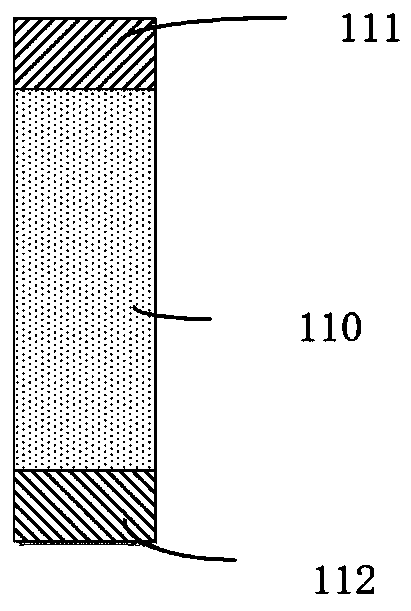

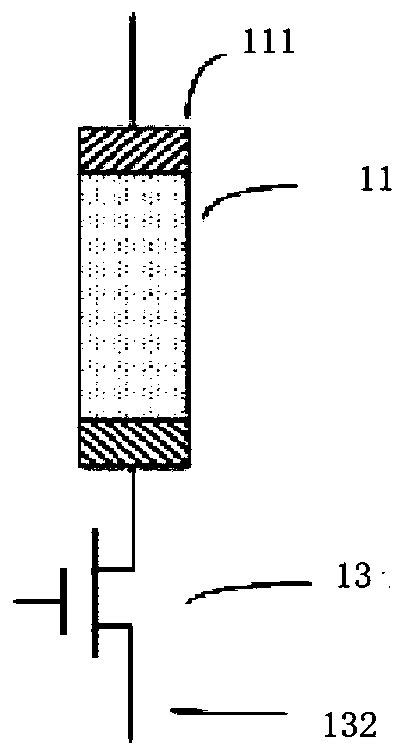

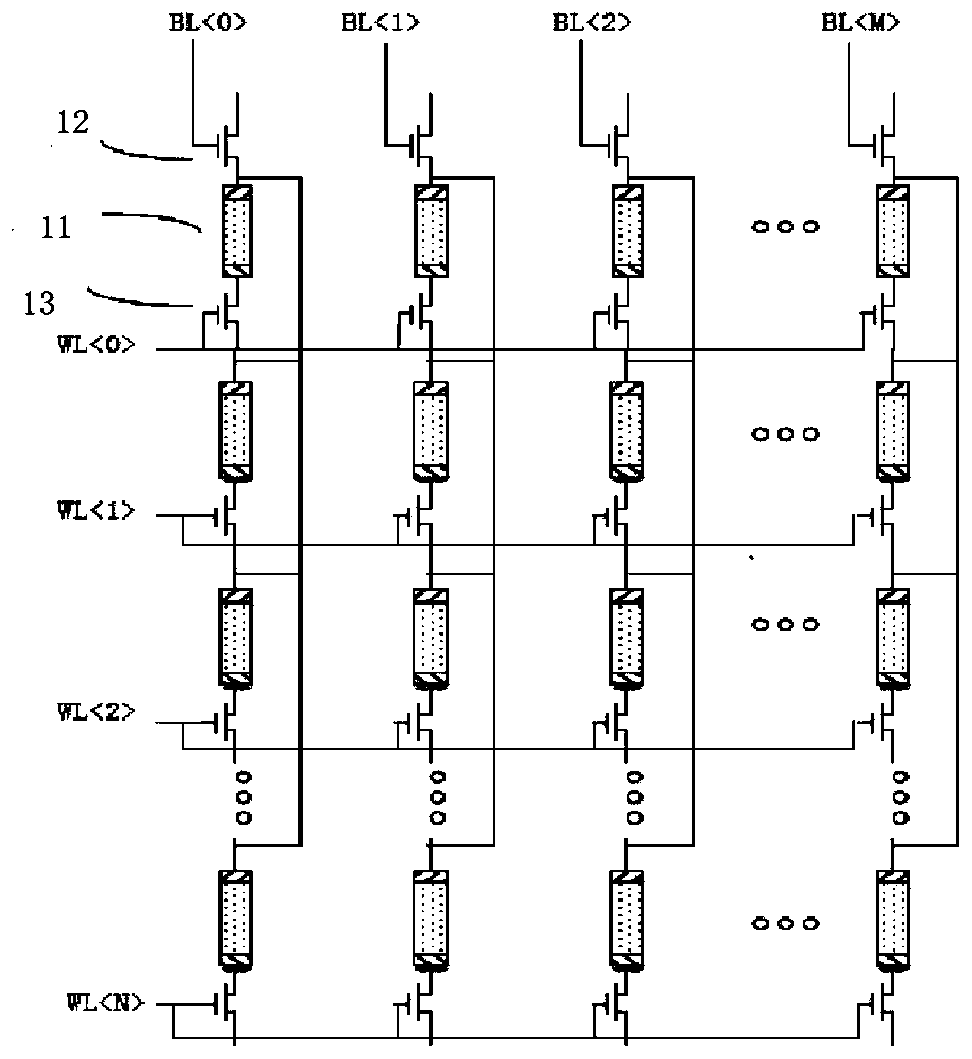

Read-write circuit and read-write method of memristor

Owner:HUAZHONG UNIV OF SCI & TECH

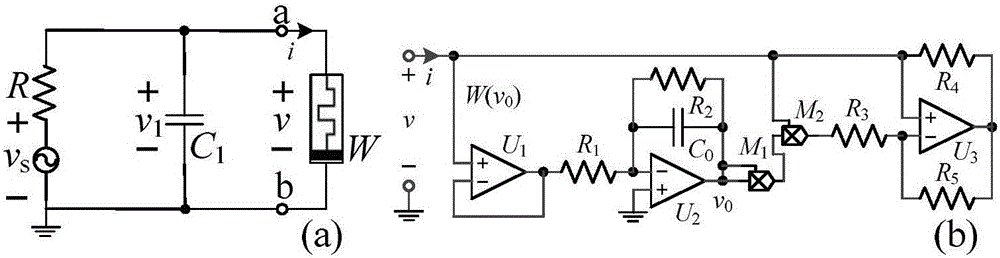

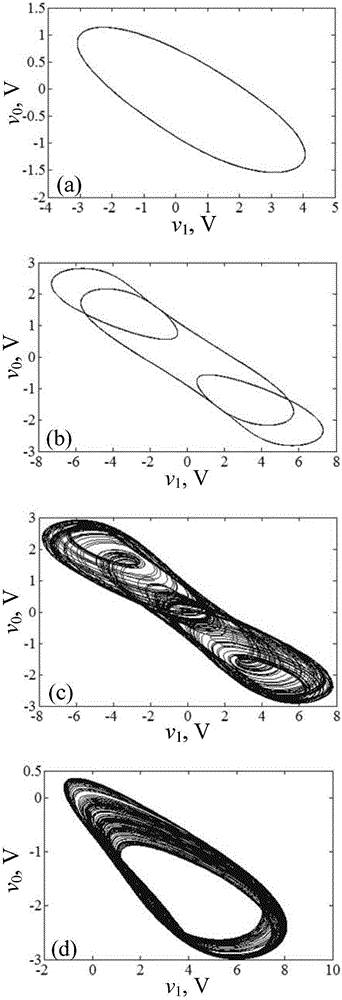

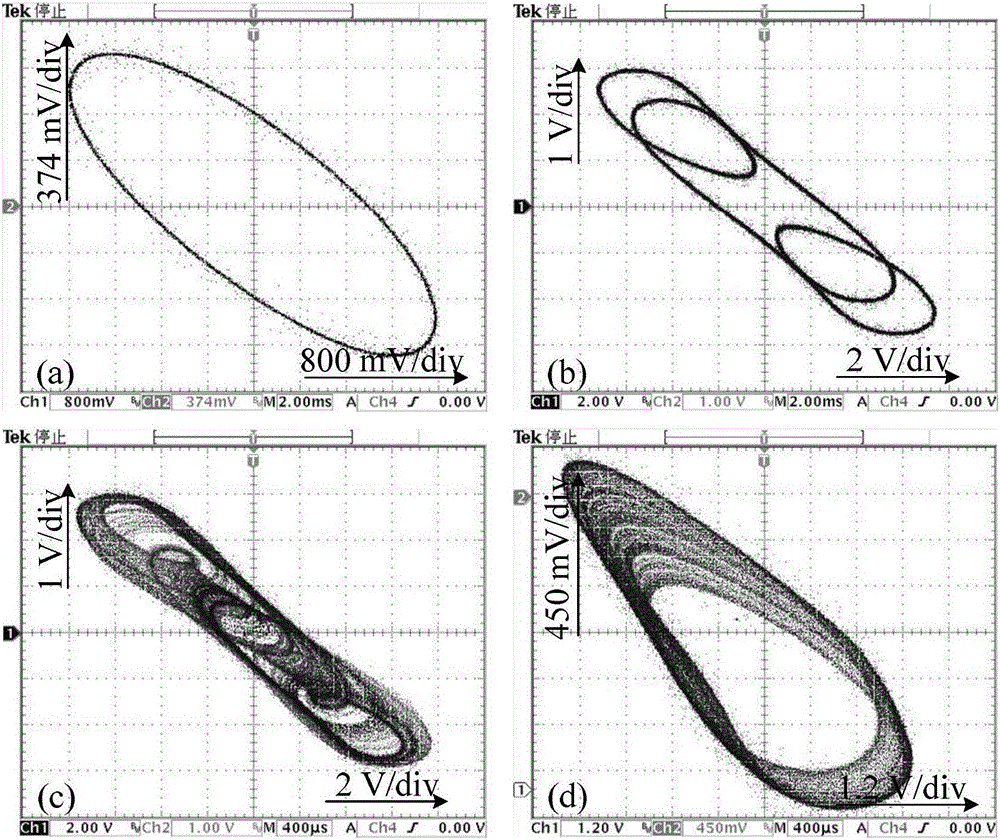

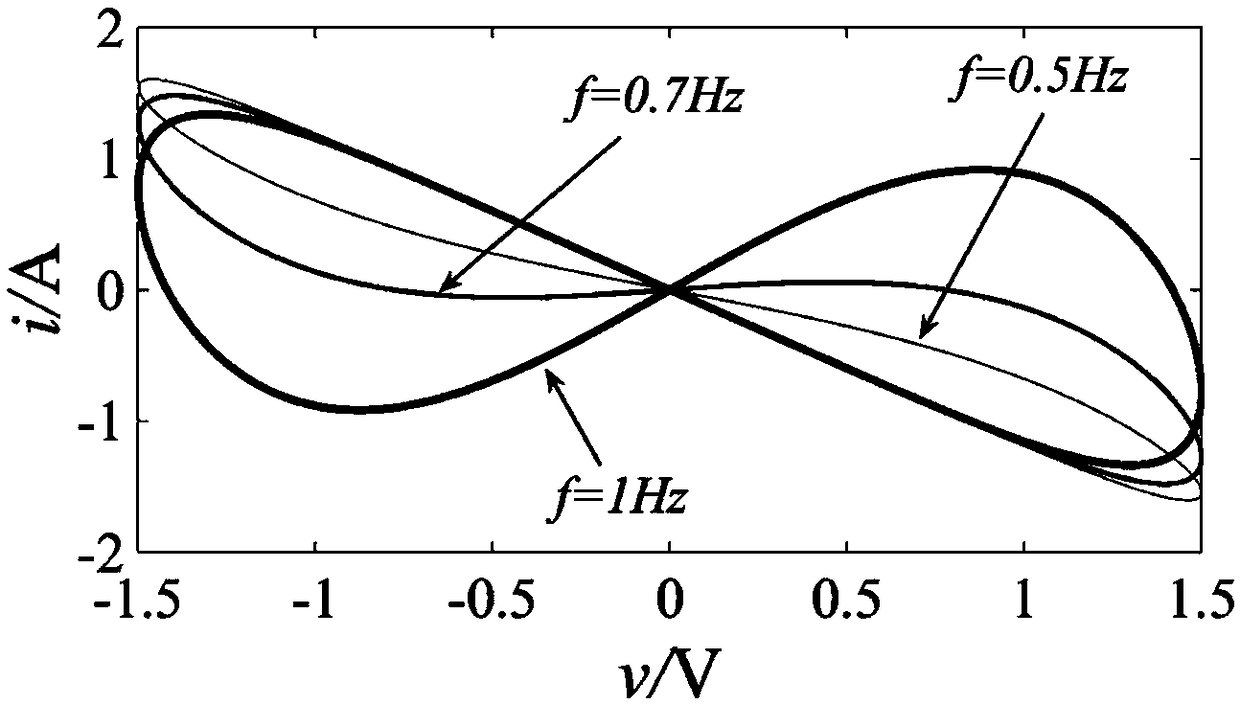

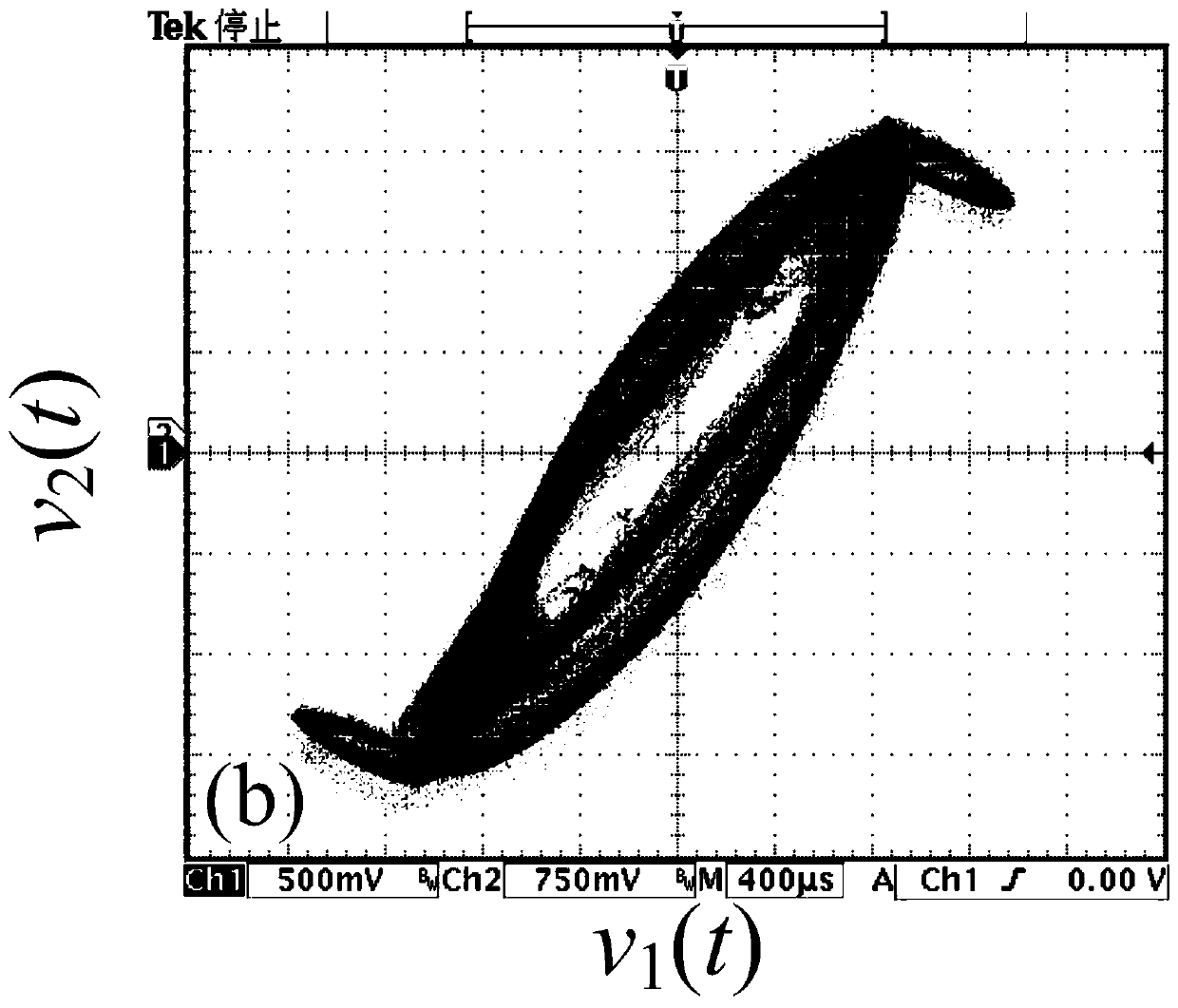

Simple second order non-autonomous memristor chaotic signal generator

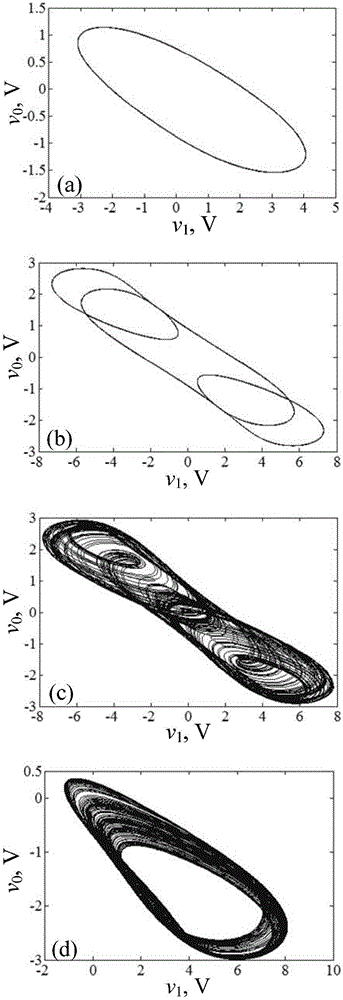

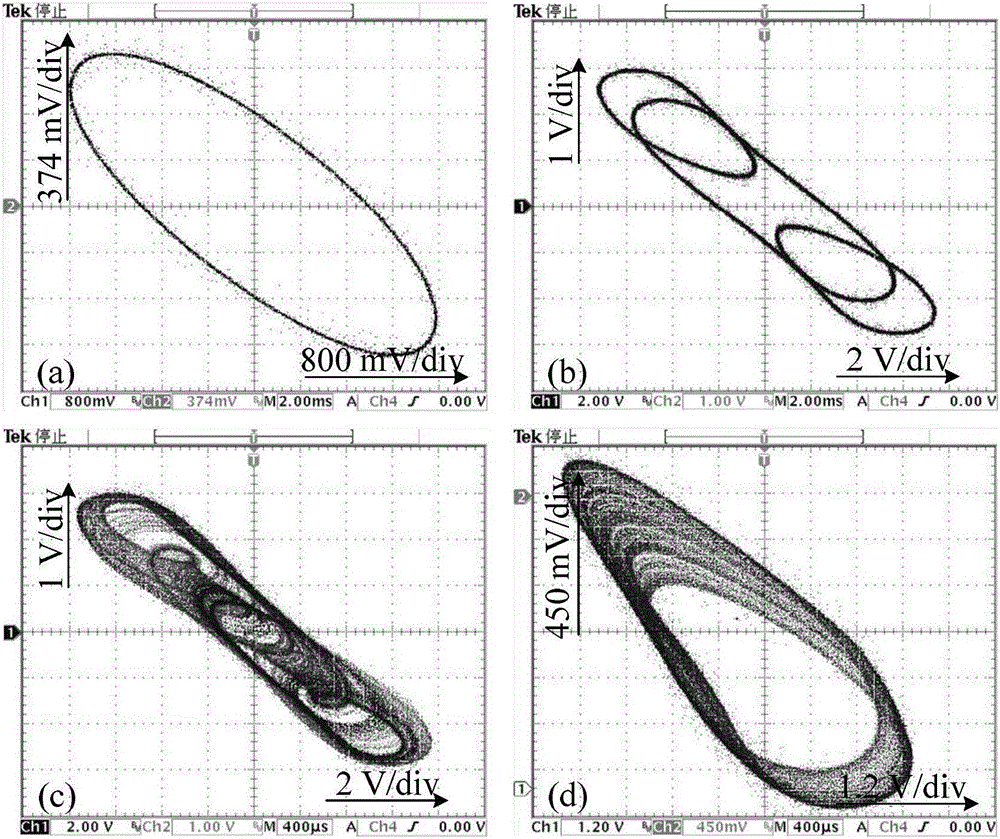

InactiveCN106209345AImprove stabilitySignificant chaotic propertiesSecuring communication by chaotic signalsNonlinear phenomenaEngineering

The invention discloses a simple second order non-autonomous memristor chaotic signal generator, consisting of a memristor driven by a standard sinusoidal voltage signal and a capacitor parallel circuit. The circuit only comprises two dynamic elements, namely a capacitor C1 and a memristor W. The essence of the simple second order non-autonomous memristor chaotic signal generator disclosed by the invention is to replace a passive LC oscillator in a memristor Chua's circuit by using the standard sinusoidal voltage signal to constitute a simple and novel chaotic signal generator, and a chaotic attractor, a periodic limit cycle and other complex phenomena can be generated by adjusting the parameters of the circuit. The circuit is simple in structure, strong in stability and significant in chaotic properties, and plays a relatively large promotion function to the application development of the memristor circuit.

Owner:CHANGZHOU UNIV

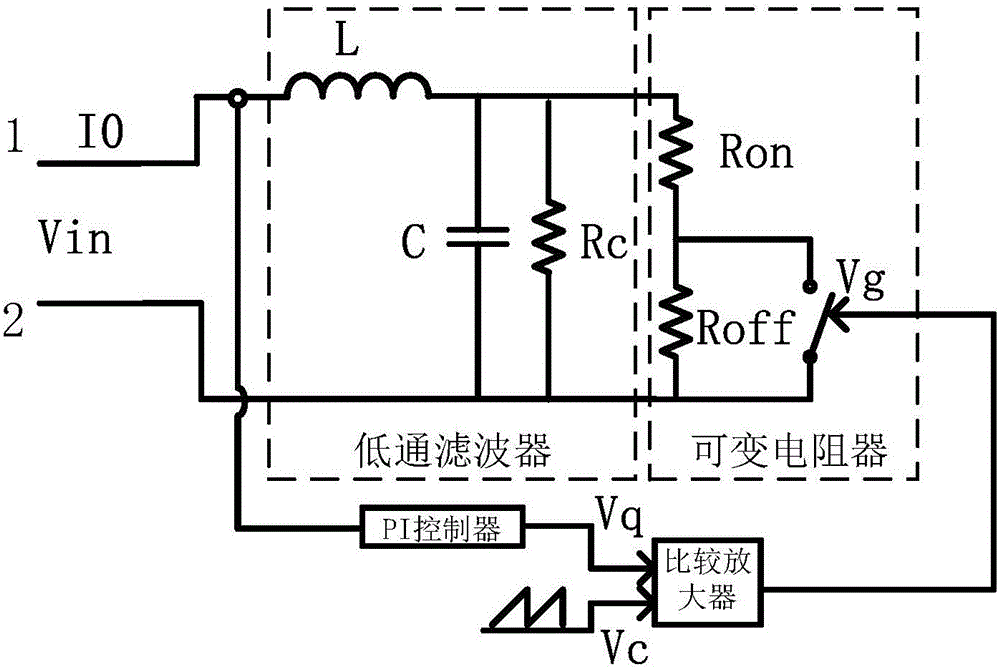

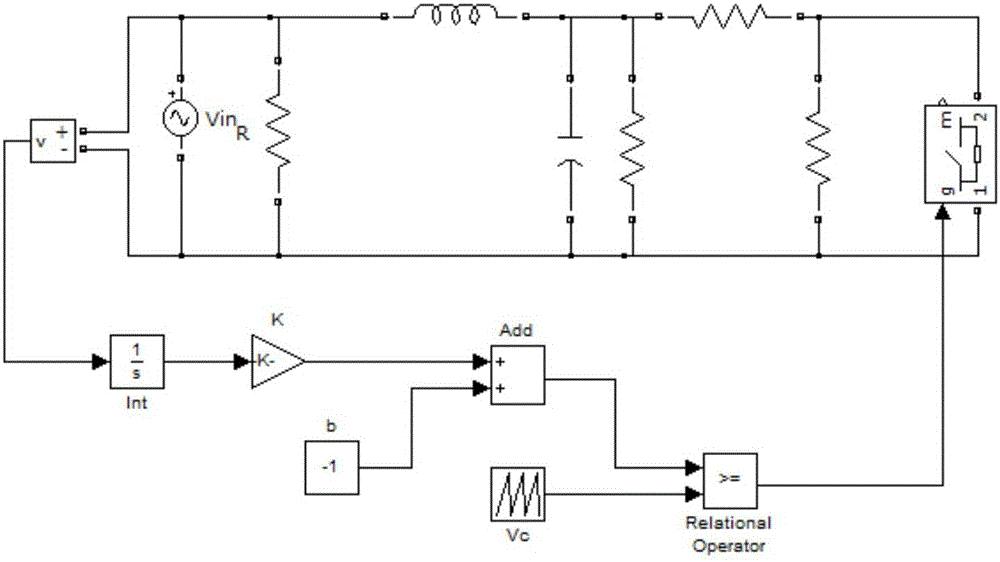

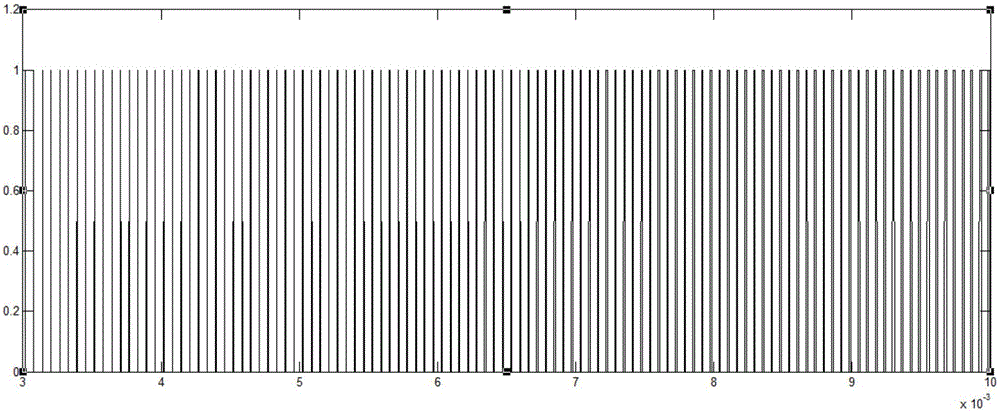

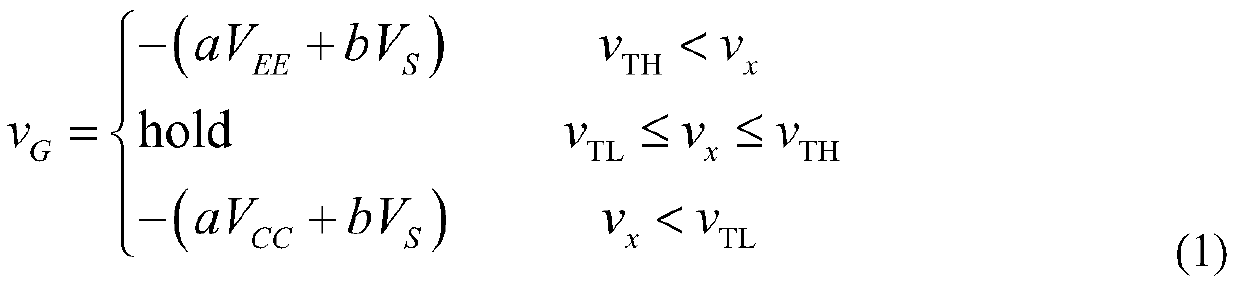

High-power memristor circuit realized by virtue of SPWM control

ActiveCN105976861AMeet the resistance characteristicsSimple structureDigital storageLow-pass filterCarrier signal

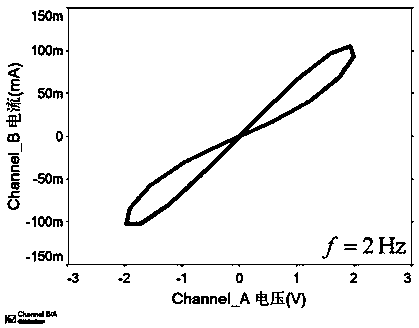

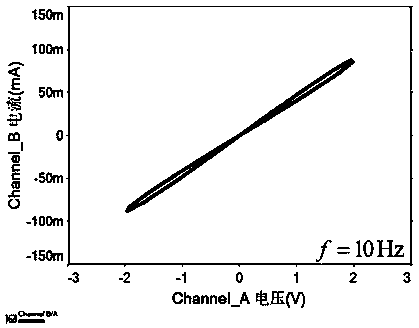

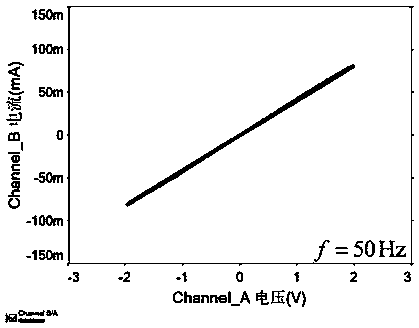

The invention discloses a high-power memristor circuit realized by virtue of SPWM control. The high-power memristor circuit comprises an inductor L, a capacitor C, a resistor Rc, a resistor Ron, a resistor Roff, a thyristor, a PI controller and a comparison amplifier, wherein the inductor L makes current continuous and forms a low pass filter with the capacitor C and the resistor Rc so as to realize the same phase between input voltage and output current; the PI controller integrates the input voltage to obtain a magnetic flux variable, the comparison amplifier makes comparison between the magnetic flux variable and a triangular carrier to obtain an SPWM waveform, and the thyristor and the resistor Roff are connected in parallel to form a variable resistor with a controllable SPWM waveform. According to the high-power memristor circuit, by virtue of the SPWM waveform, the resistance value of the variable resistor is changed to conform to the properties of the resistance value of the memristor; by utilizing the power devices such as the inductor, the capacitor and the thyristor, the circuit structure is simple, and the thyristor with any power level can be theoretically realized; by utilizing the low pass filter, the output current is continuous and has the same phase with the input voltage.

Owner:SOUTH CHINA UNIV OF TECH

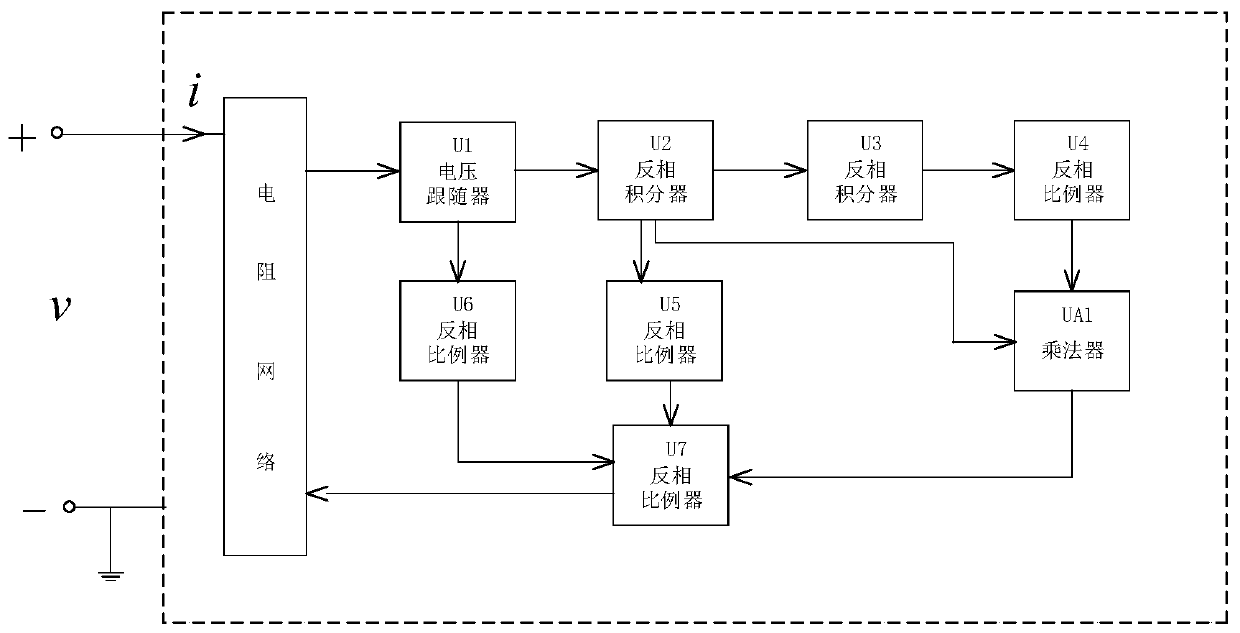

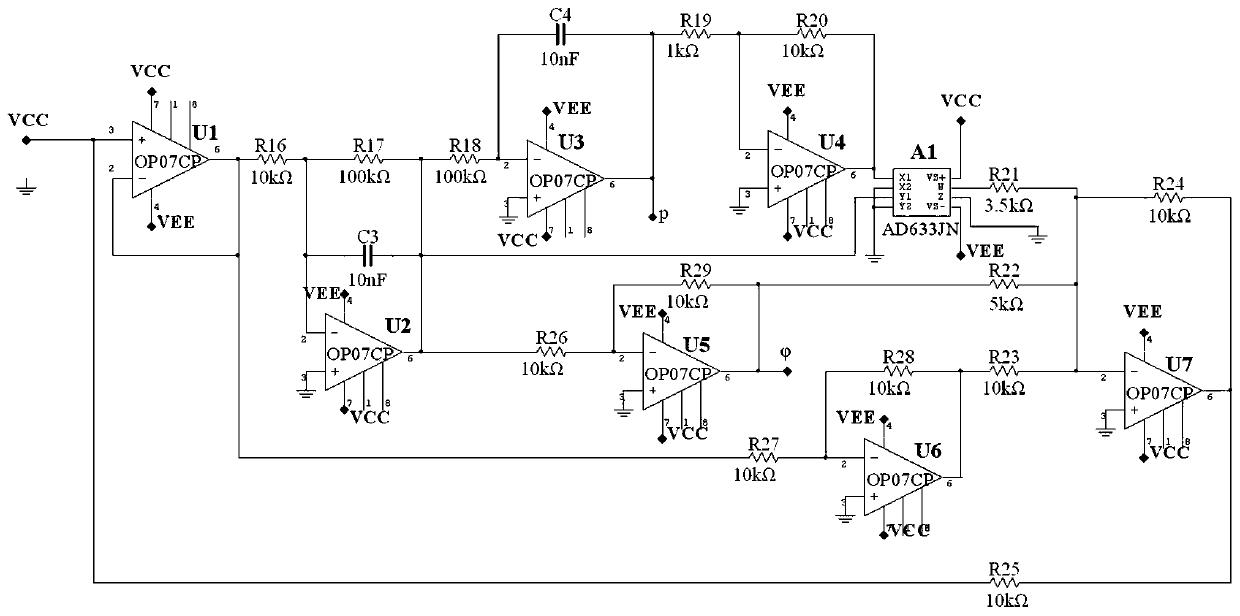

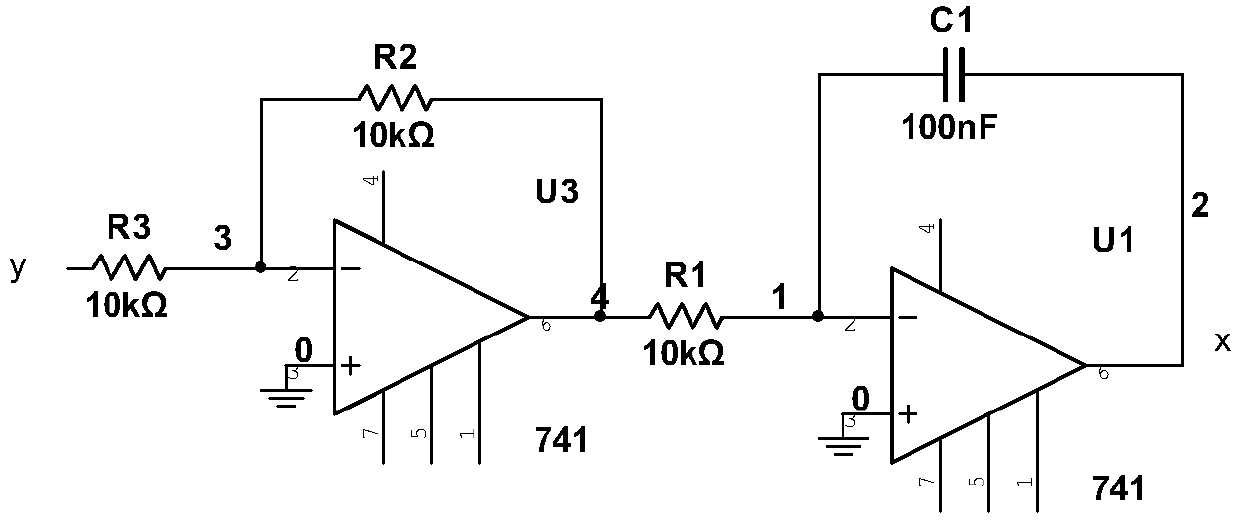

A quadratic curve meminductor equivalent analog circuit

ActiveCN109885858AAchieving volt-ampere characteristicsRealize the productSpecial data processing applicationsAudio power amplifierOperational amplifier

The invention discloses a quadratic curve meminductor equivalent analog circuit, belongs to the technical field of circuit design, and designs an analog equivalent circuit capable of realizing volt-ampere characteristics of a meminductor. The volt-ampere characteristic of the meminductor is realized by utilizing an analog circuit; specifically, a quadratic curve meminductor volt-ampere characteristic is realized. An integrated operational circuit is used for achieving the corresponding operation in the characteristics of a meminductor, the analog circuit comprises seven operational amplifiersand a multiplier, the integrated operational amplifier is mainly used for achieving voltage following, inverting integration and inverting proportional operation, and the multiplier is used for achieving the product of two input signals. The memristor circuit is simple in structure, can replace an actual meminductor to realize circuit design, experiment and application related to the meminductor under the condition that a nano-scale single isolated memristor device cannot be obtained at present and in the future, and has the important significance for characteristic and application research ofthe meminductor.

Owner:SHANDONG UNIV OF SCI & TECH

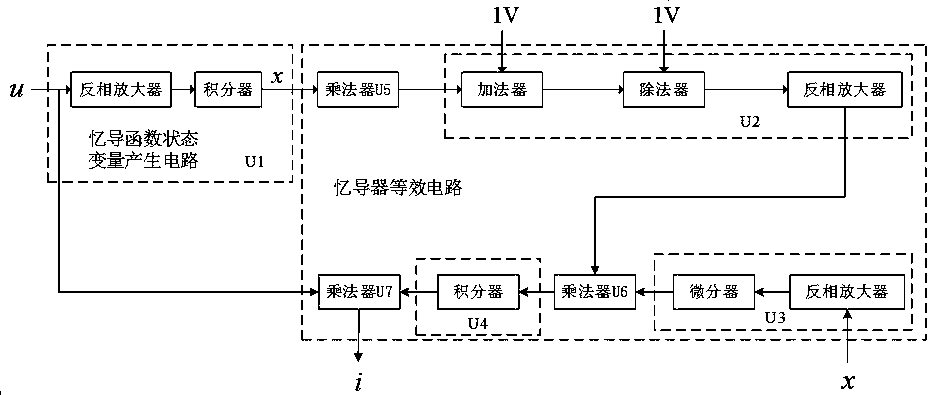

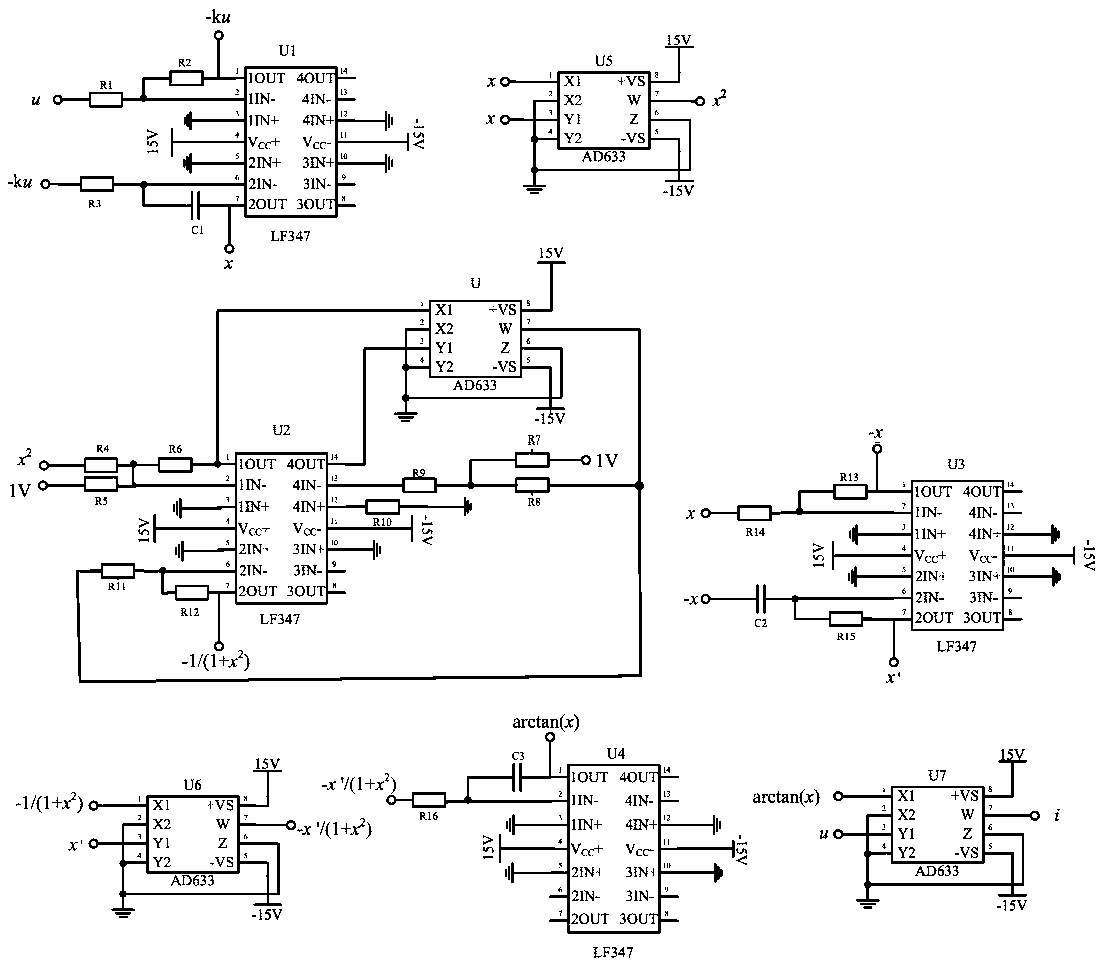

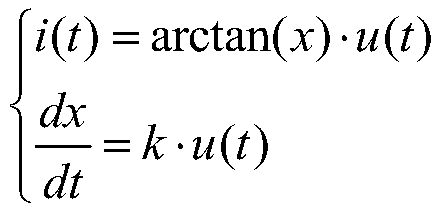

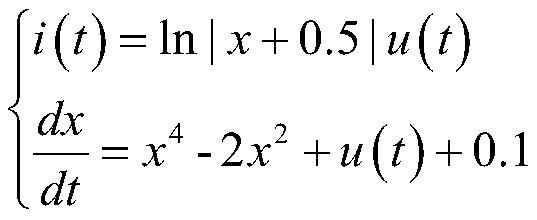

Arc tangent trigonometric function memristor circuit model

PendingCN111079365AComputer aided designSpecial data processing applicationsBinary multiplierControl signal

The invention discloses an arc tangent trigonometric function voltage-controlled memristor circuit model. An integrated operational amplifier U1 is connected with an input end, namely a voltage and current test end of a memristor; the integrated operational amplifier U1 is used for realizing inverse amplification operation and integral operation, outputting a signal after integral operation and finally solving a state variable for controlling a memristive value, and the integrated operational amplifier U2 is used for realizing additive operation, inverse amplification operation and division operation; the multiplier U3 realizes derivation operation and inverse amplification operation of the signal; the integrated operational amplifier U4 is used for realizing integral operation; the multipliers U5 and U6 are used for realizing multiplication; and the multiplier U7 multiplies the control signal by an input voltage signal to obtain the final memristor point flow. The device is used for simulating volt-ampere characteristics of the memristor and replacing an actual memristor for experiment, application and research.

Owner:HANGZHOU DIANZI UNIV

Simple second-order non-autonomous memristor chaotic signal generator

InactiveCN105827390AImprove stabilitySignificant chaotic propertiesDigital storageSecuring communication by chaotic signalsNonlinear phenomenaEngineering

Owner:CHANGZHOU UNIV

Band-pass filter based on memristor

The invention relates to a band-pass filter based on a memristor. The technical scheme is showed as that the filter comprises a control module (1), a low-pass filter module (3) and a high-pass filter module (6), wherein the low-pass filter module (3) is formed by connection of the output end VLP1 of a first memristor circuit (2) and the input end VIN2 of a first memcapacitor equivalent circuit (4); and the high-pass filter module (6) is formed by connection of the output end VHP1 of a second memcapacitor equivalent circuit (5) and the input end VIN4 of a second memristor circuit (7). The input end of the first memristor circuit (2), the input end of the first memcapacitor equivalent circuit (4), the input end of the second memcapacitor equivalent circuit (5) and the input end of the second memristor circuit (7) are correspondingly connected with the output ends of the control module (1). The input end VIN1 of the first memristor circuit (2) is externally connected with an input signal of a filter; and the output end of the second memristor circuit (7) is externally connected with an output signal of the filter. The band-pass filter provided by the invention has the characteristics of simplicity in structure, highness in precision, easiness to control and the like.

Owner:WUHAN UNIV OF SCI & TECH

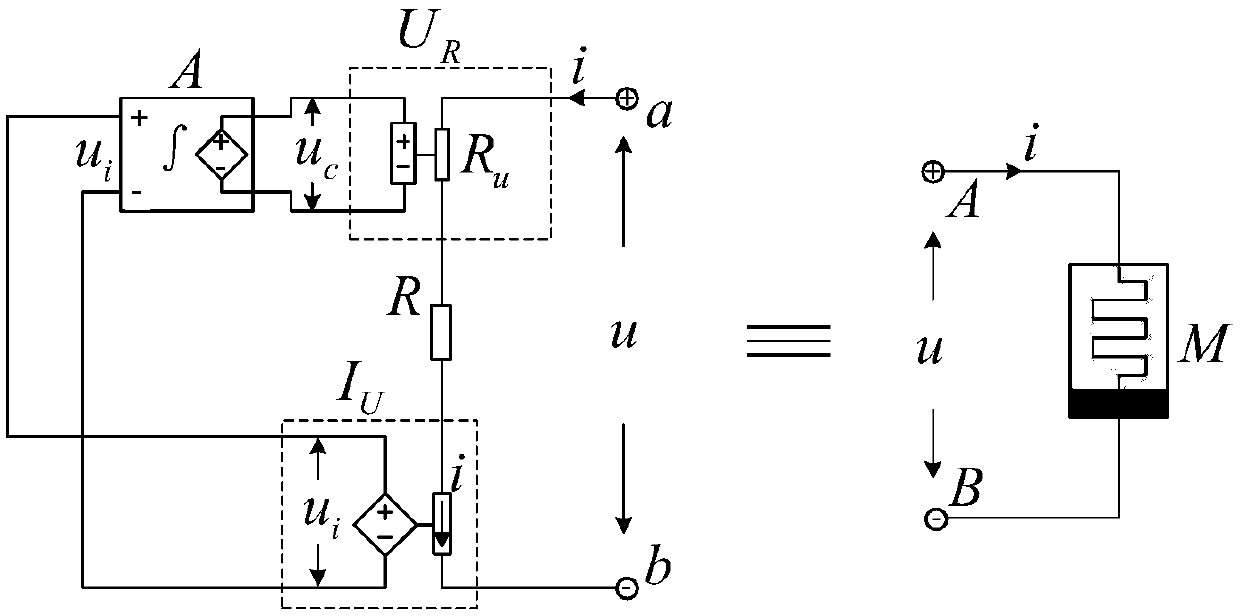

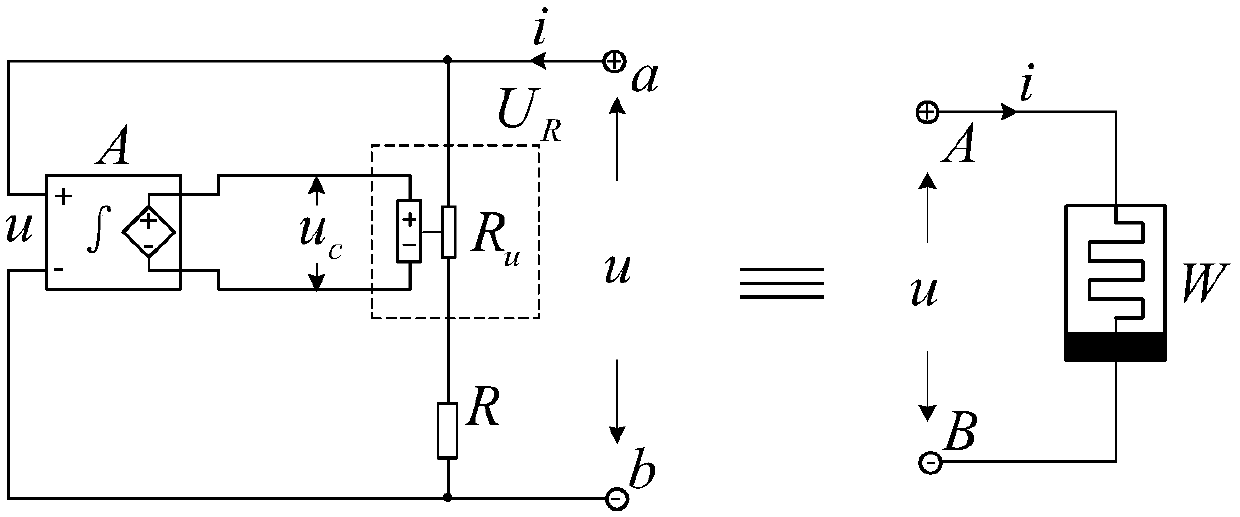

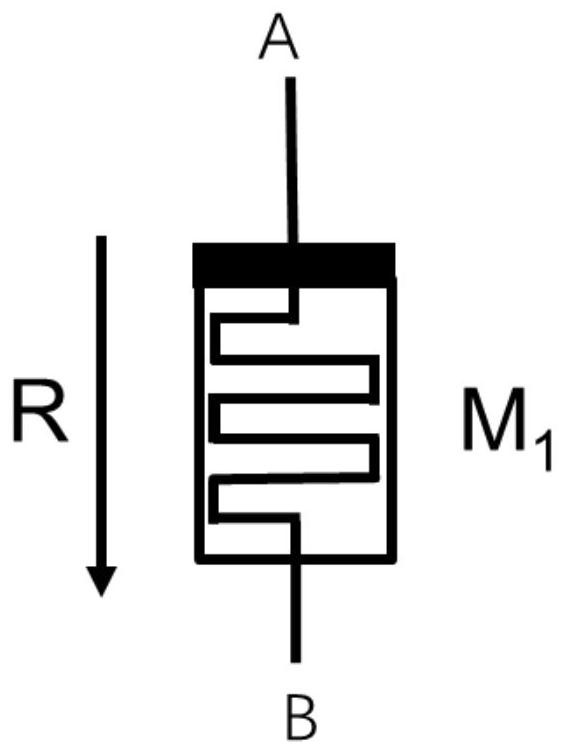

Extremely-simple floating ground charge-controlled memristor circuit simulation model

ActiveCN108846215AReduce complexityReduce component countSpecial data processing applicationsElectrical resistance and conductanceIntegrator

The invention discloses an extremely-simple floating ground charge-controlled memristor circuit simulation model. The model comprises a port a, a port b, a voltage-controlled resistor UR, a resistor R, a current-controlled voltage source IU and a voltage integrator A; the voltage-controlled resistor UR comprises a voltage control end uc and a controlled resistor Ru; the resistance value of the controlled resistor Ru in the voltage-controlled resistor UR is controlled by the voltage value of the voltage control end uc; the current-controlled voltage source IU comprises a current control end i and a voltage source output end ui; the voltage value of the voltage source output end ui in the current-controlled voltage source IU is controlled by the current value of the current control end i; and the voltage integrator A comprises a voltage input end ui and a voltage output end uc. According to the floating ground charge-controlled memristor circuit simulation model provided by the invention, electrical characteristics of the ports a and b are equivalent to the characteristics of the ports A and B of a memristor M; only four elements existing in simulation software need to be used; and besides, the floating ground charge-controlled memristor circuit simulation model is a two-port model, thus the complexity and the number of components of the existing charge-controlled memristor circuit simulation model are further reduced, and the model has the advantages that the grounding of one end is not required, the change range of the memristance is flexible, and the working voltage rangeis wide.

Owner:CHENGDU NORMAL UNIV

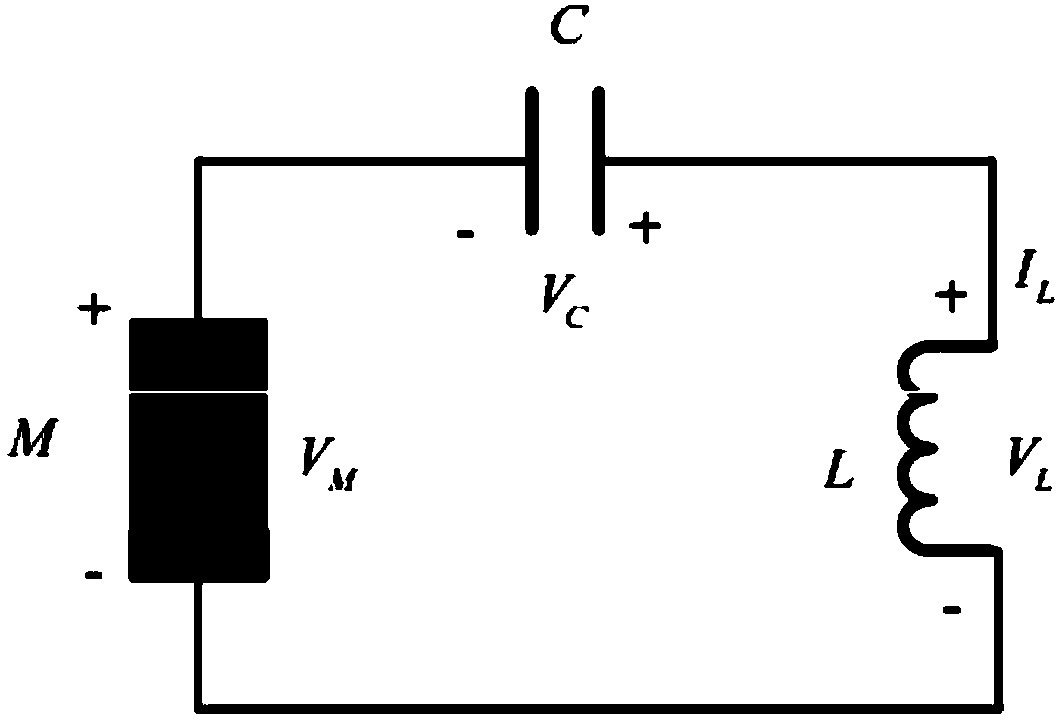

A fourth-order three-dimensional memristor circuit system and a realization circuit

ActiveCN109033602ARich Dynamic BehaviorIncreased complexitySpecial data processing applicationsCapacitanceSecure communication

The invention provides a four-order three-dimensional memristor circuit system and a realizing circuit, the system comprising a capacitor, an inductor and a memristor element connected in series in turn, and the capacitor, the inductor and the memristor element form a ring structure, and a circuit equation of the ring structure is obtained equivalently from the memristor element. The invention constructs a memristor element according to the typical properties of the memristor system, constructs a circuit comprising a capacitor, an inductor and a memristor by using the constructed memristor element, and analyzes the dynamic properties of the memristor element. By using an additive circuit, a multiplying circuit, a proportional circuit and an integrating circuit Mitisim simulation is realized; the simulation circuit comprises three channels, an output signal of the second channel as an input signal of the first channel, an output signal of the first channel, a second channel and a thirdchannel as an input signal of the second channel, and an output signal of the second channel as an input signal of the third channel. The invention can generate abundant dynamic behaviors, and to a certain extent, the complexity and the security of the secure communication are increased.

Owner:ZHENGZHOU UNIVERSITY OF LIGHT INDUSTRY

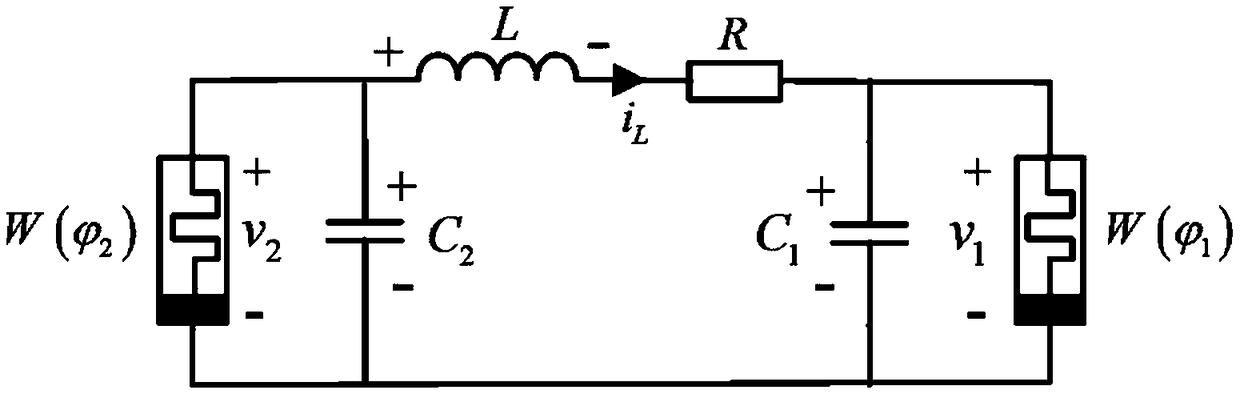

Chaotic oscillator based on multiple memristors

PendingCN110798150AEasy to implementImprove stabilityOscillations generatorsCapacitanceHemt circuits

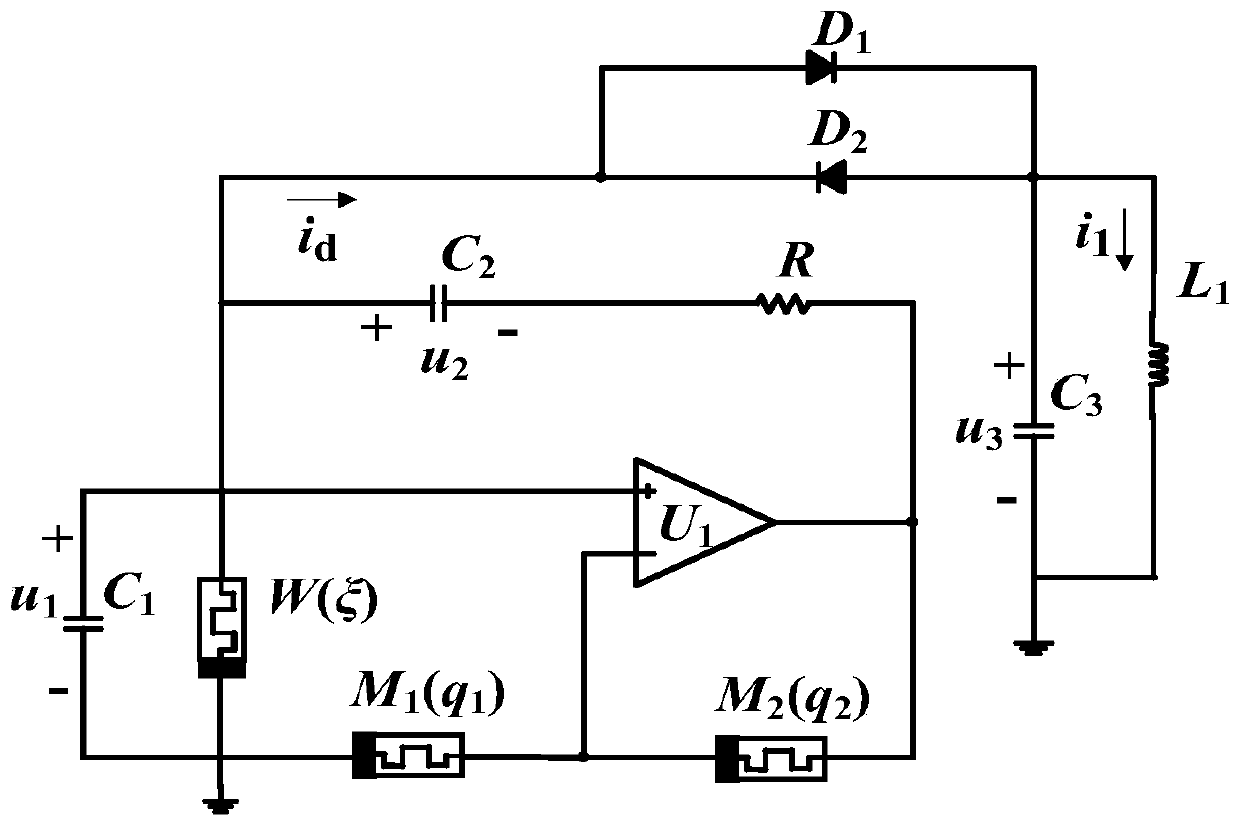

The invention provides a chaotic oscillator based on multiple memristors. The oscillator comprises an operational amplifier U1, capacitors C1, C2 and C3, two positive and negative diodes D1 and D2, aresistor R, an inductor L1, two charge control memristors M1 (q1) and M2 (q2) and a magnetic control memristor W (xi), wherein one end of the magnetic control memristor W (xi) is connected with the positive phase input end of the operational amplifier; wherein one ends of the two charge-controlled memristors are connected with the inverting input end of the operational amplifier, the positive electrode end of the capacitor C1 is connected with the inverting input end of the operational amplifier, the positive electrode end of the capacitor C2 is connected with the positive electrode end of thecapacitor C1, the capacitor C3 and the inductor L1 are connected in parallel and simultaneously connected with one ends of the two positive and negative diodes D1 and D2, and the other end is grounded. The problems that a memristor circuit model in the prior art is too simple in structure, circuit elements involved in a circuit are relatively few, a certain deviation exists between a large numberof single memristor oscillators and the requirement of an ideal commercial memristor circuit model, and the design structure is relatively unreasonable are solved.

Owner:DALIAN MARITIME UNIVERSITY

Computation of boolean formulas using sneak paths in crossbar computing

ActiveUS9319047B2Programmable logic circuit arrangementsLogic circuits using semiconductor devicesGeneral purposeTheoretical computer science

Memristor-based nano-crossbar computing is a revolutionary computing paradigm that does away with the traditional Von Neumann architectural separation of memory and computation units. The computation of Boolean formulas using memristor circuits has been a subject of several recent investigations. Crossbar computing, in general, has also been a topic of active interest, but sneak paths have posed a hurdle in the design of pervasive general-purpose crossbar computing paradigms. Various embodiments are disclosed which demonstrate that sneak paths in nano-crossbar computing can be exploited to design a Boolean-formula evaluation strategy. Such nano-crossbar designs are also an effective approach for synthesizing high performance customized arithmetic and logic circuits.

Owner:THE UNITED STATES OF AMERICA AS REPRESETNED BY THE SEC OF THE AIR FORCE +1

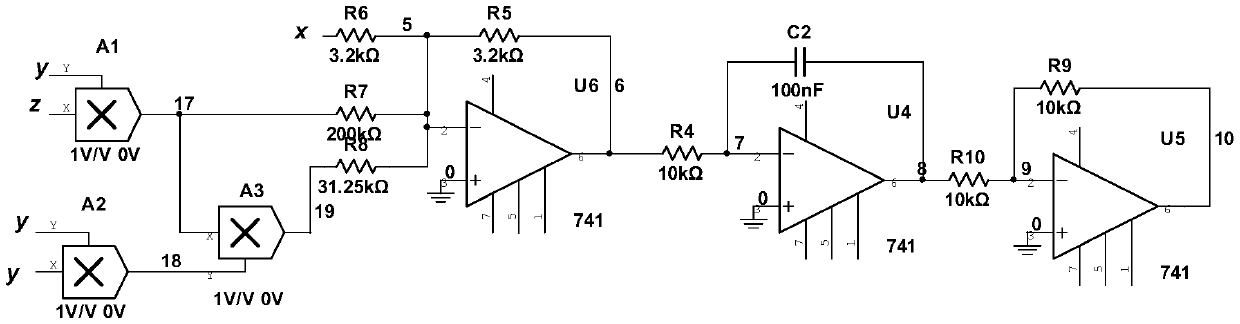

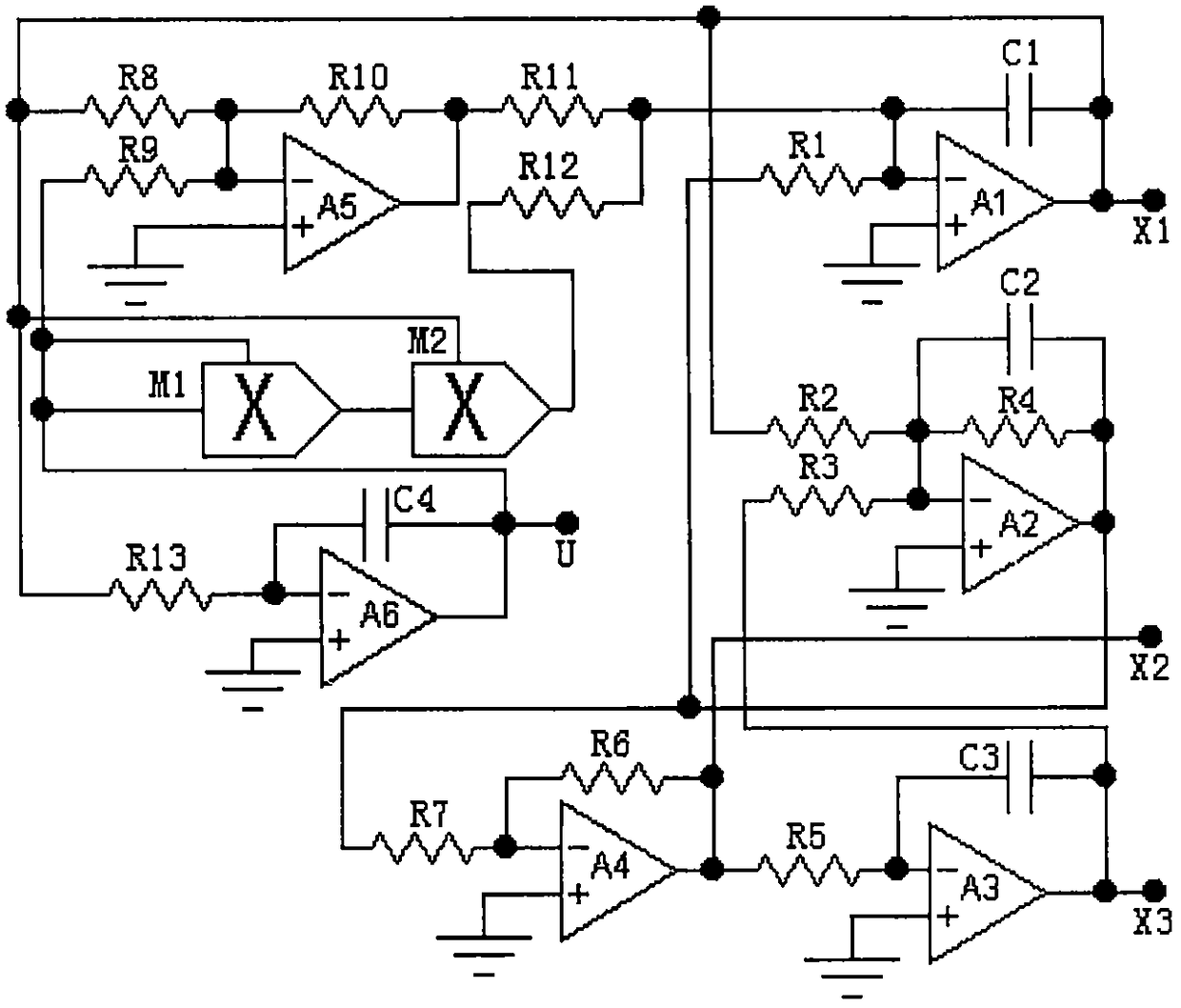

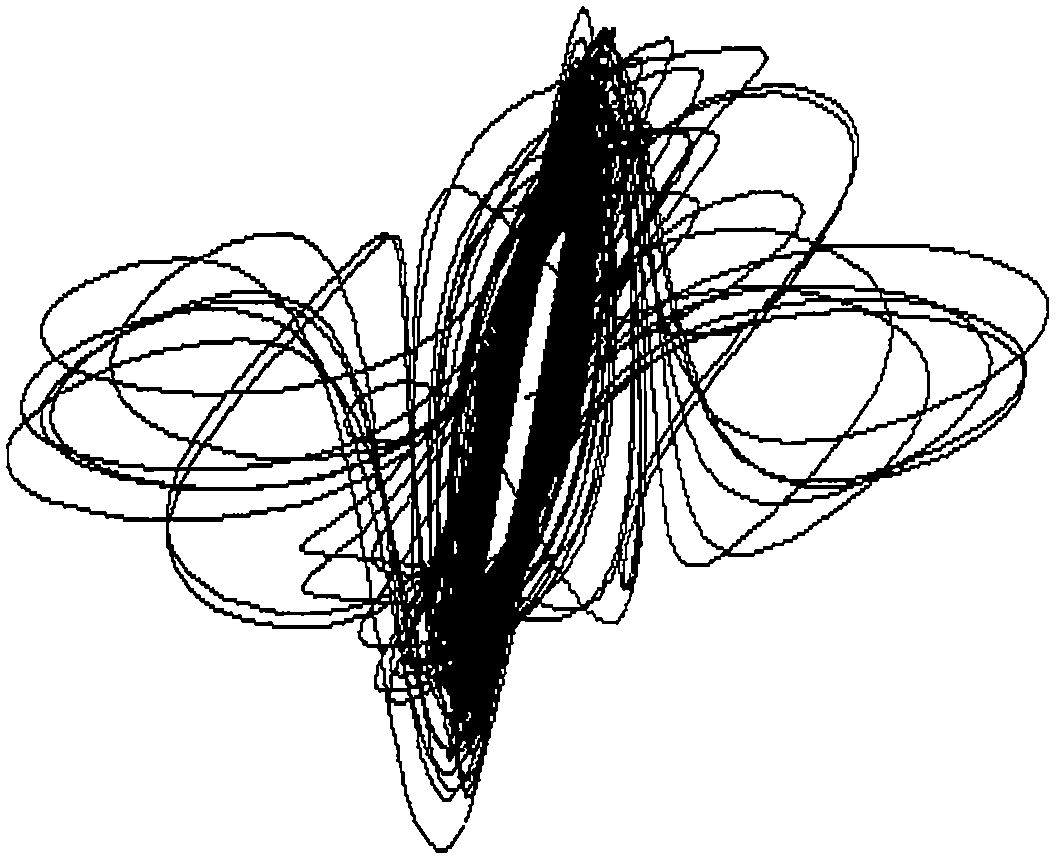

Memristor chaotic circuit based on Chua's circuit

The invention relates to a memristor chaotic circuit based on the Chua's circuit, which is characterized in that a first operational amplifier A1, a second operational amplifier A2 and a third operational amplifier A3 constitute a linear phase-reversing integrator, a fourth operational amplifier A4 constitutes a linear phase-reversing amplifier, and the output ends of the first operational amplifier A1, the fourth operational amplifier A4, the third operational amplifier A3 and a sixth operational amplifier A6 are respectively a chaotic signal output end X1, a chaotic signal output end X2, a chaotic signal output end X3 and a chaotic signal output end U; a phase-reversing integrator A1 is connected with a phase-reversing integrator A2, a phase-reversing integrator A6 and a second analog multiplier M2; the phase-reversing integrator A2 is connected with the first operational amplifier A2 and the fourth operational amplifier A4; the phase-reversing integrator A3 is connected with the phase-reversing integrator A2; the A1, A2, A3 and A4 constitute a third-order dynamic integrator circuit; and the A5, A6, M1 and M2 constitute a memristor circuit. Disclosed by the invention is a chaoticcircuit which can output various waveforms, phase diagrams and chaotic evolution curves of a memristor chaotic circuit based on the Chua's circuit and can form a chaotic secure communication system.

Owner:HEXI UNIV

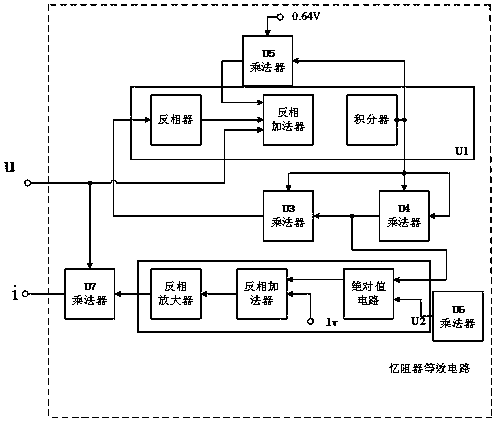

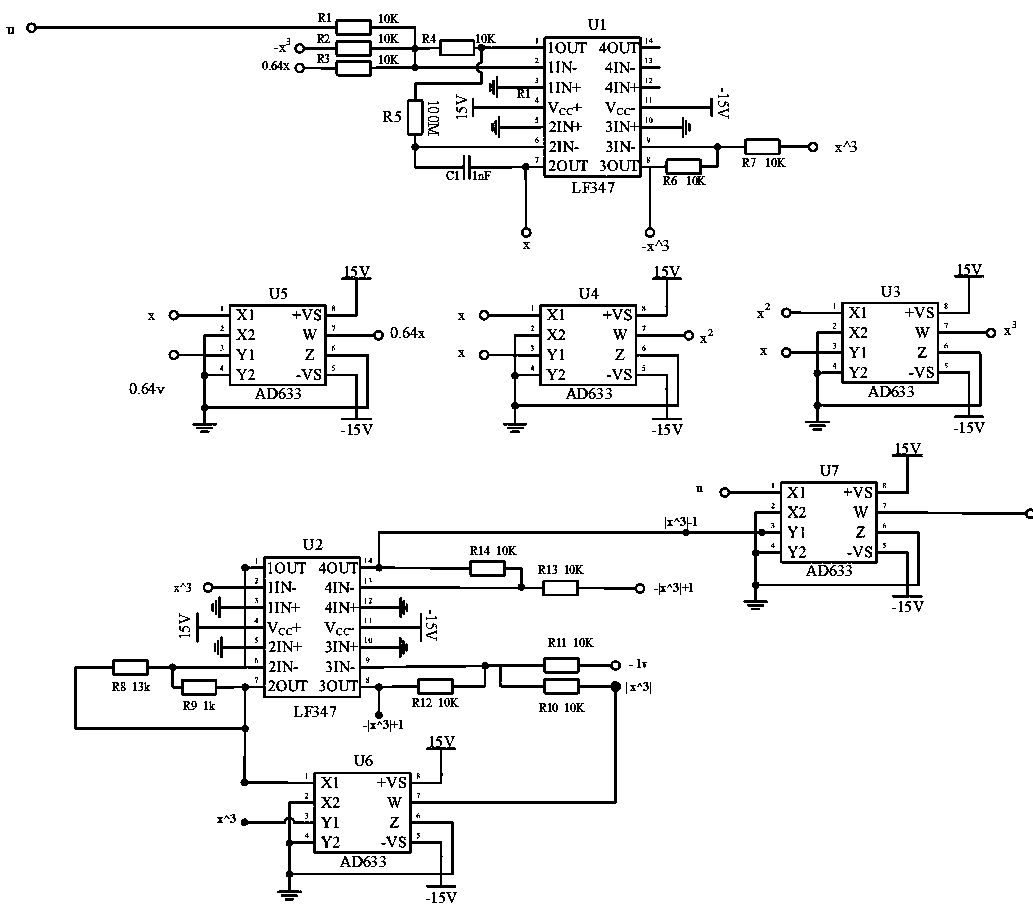

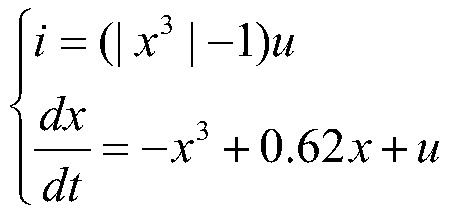

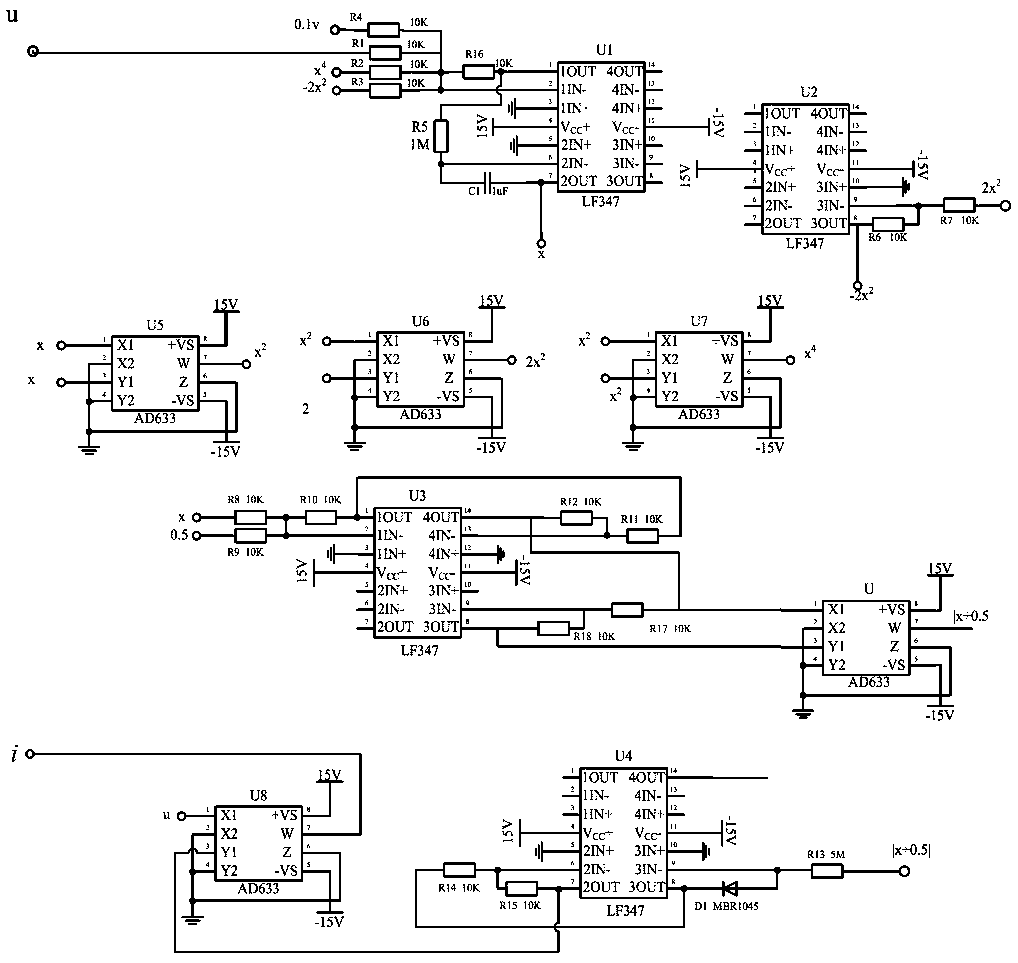

Third-order absolute value local active memristor circuit model

PendingCN110222451ASimple structureSpecial data processing applicationsEnergy efficient computingElectrical resistance and conductanceControl signal

The invention discloses a mathematical model of a three-order absolute value local active memristor and an equivalent circuit model thereof. The circuit model comprises an integrated operational amplifier U1, an integrated operational amplifier U2, multipliers U3, U4, U5, U6 and U7, and component resistors and capacitors. The integrated operational amplifier U1 is used for realizing integral operation, addition operation and reverse-phase amplification operation. The integrated operational amplifier U2 is used for absolute value operation, addition operation and inverse operation to obtain a required control signal. The multipliers U3, U4, U5, U6 and U7 realize multiplication of signals. An equivalent circuit of the local active memristor is designed by using the integrated operational amplifier and the multiplier, and an actual local active memristor is replaced for experiment, application and research.

Owner:HANGZHOU DIANZI UNIV

Floating geomagnetically controlled memristor simulator based on a transconductance operational amplifier

PendingCN109918863AAvoid Integral Drift PhenomenonHigh precisionSpecial data processing applicationsCapacitancePower flow

The invention discloses a floating geomagnetically controlled memristor simulator based on a transconductance operational amplifier. comprising a port a, a port b, a transconductance operational amplifier U1, a transconductance operational amplifier U2, a current feedback operational amplifier U3, a voltage feedback operational amplifier U4, a capacitor C1, a resistor R1, a resistor R2, a resistorR3, a resistor R4, a resistor R5, a resistor R6, a resistor R7, a resistor R8, a resistor R9, a resistor R10 and a resistor R11.The model of the transconductance operational amplifier U1 is LM13600,and the model of the transconductance operational amplifier U2 is LM13600. The electrical characteristics of the floating geomagnetically controlled memristor simulator port a and the floating geomagnetically controlled memristor simulator port b are equivalent to the port characteristics of a magnetically controlled memristor, one end is not required to be grounded, and the floating geomagnetically controlled memristor simulator port a and the floating geomagnetically controlled memristor simulator port b can be widely applied to design and testing of memristor circuits (memristor chaotic circuits, memristor oscillating circuits and the like).

Owner:CHENGDU NORMAL UNIV

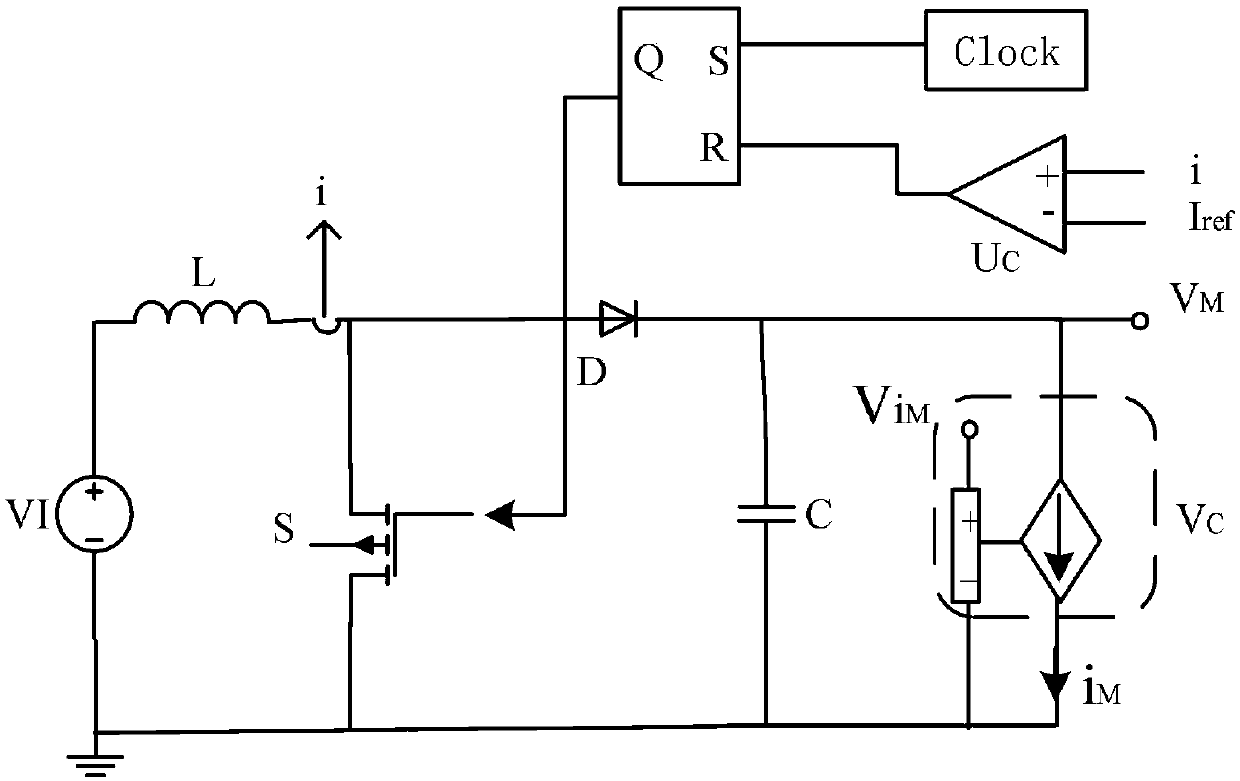

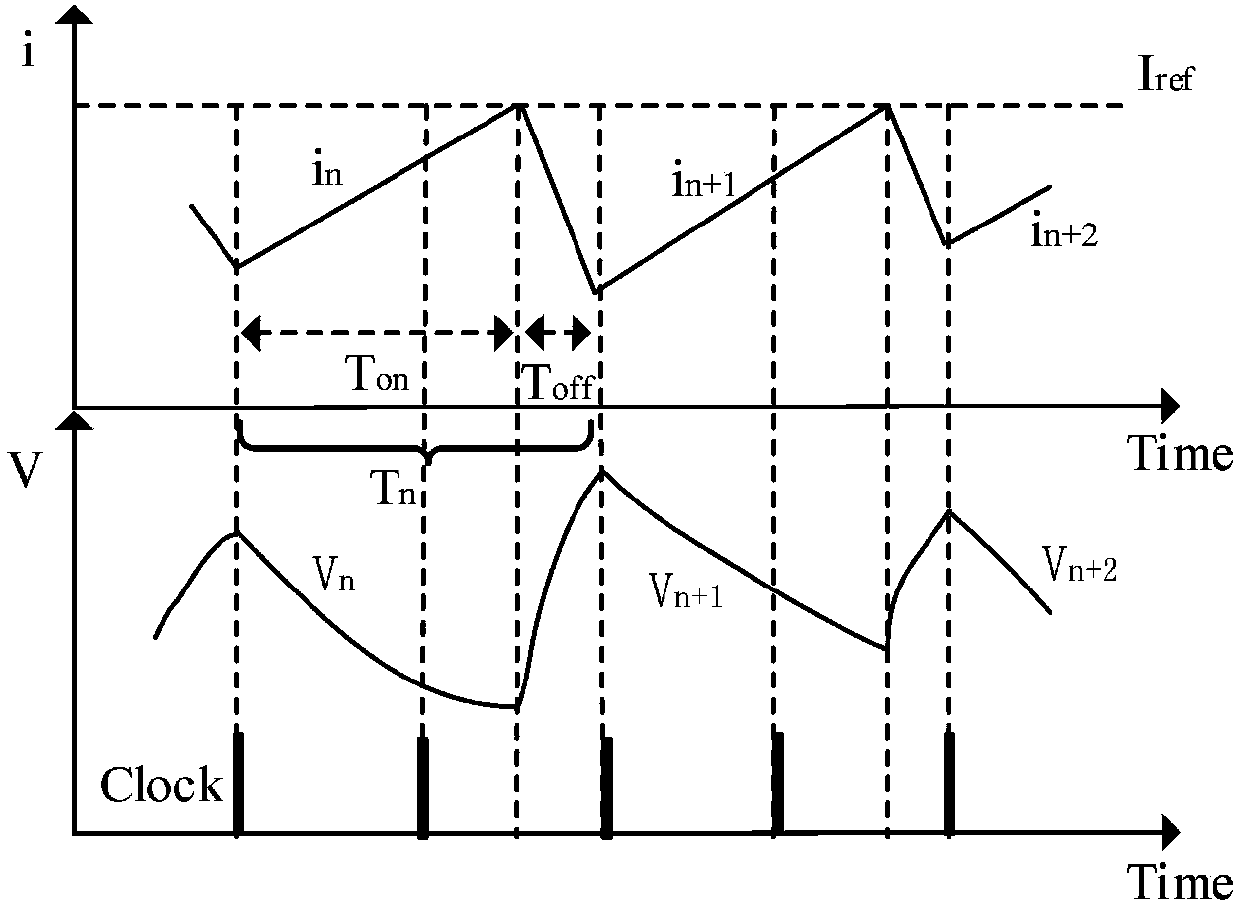

Boost convertor circuit with memristor load

InactiveCN108539972AExcited chaosGet dynamic propertiesDc-dc conversionElectric variable regulationEngineeringVoltage control

The invention discloses a Boost converter circuit with memristor load. The Boost converter circuit with the memristor load comprises a Boost converter circuit; the voltage output terminal of a Boost converter is connected in parallel with a voltage control current source; the voltage input terminal of the voltage control side in the voltage control current source is connected with the output terminal of a memristor circuit; and the ratio of the voltage of the voltage control side of the voltage control current source to the current of the current control side is 1:1. The Boost converter circuit applies the memristor circuit to the Boost converter, and realizes a nonlinear switched circuit with a memristor load, thereby constructing novel circuit topology, so that on the one hand, a novel chaos phenomenon can be stimulated, and novel dynamic characteristics are obtained, and on the other hand, the boost mechanism is improved.

Owner:TIANJIN UNIV

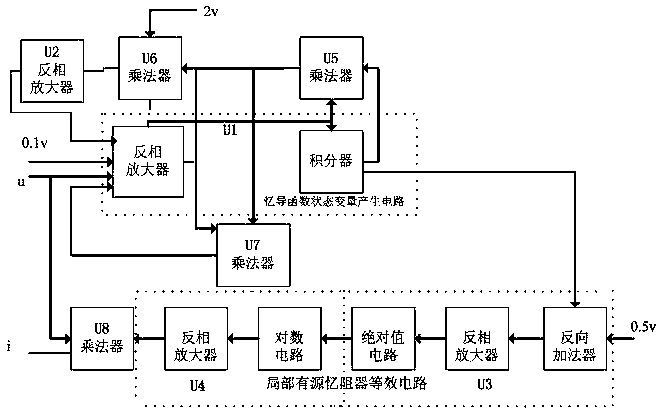

Novel logarithmic absolute value local active memristor circuit model

ActiveCN110245421ASimple structureCAD circuit designEnergy efficient computingAudio power amplifierState variable

The invention discloses a novel logarithmic absolute value local active memristor circuit model. An integrated operational amplifier U1 and a multiplier U8 are respectively connected with an input end; the integrated operational amplifier U1 is used for realizing inverse addition operation and integral operation and returning an output signal to the multiplier U5; the integrated operational amplifier U2 is used for realizing inverse amplification operation and returning the output signal to the integrated operational amplifier U1, and finally obtaining a state variable for controlling a memristor value. The integrated operational amplifier U3 is used for realizing inverse addition operation, inverse amplification operation and absolute value operation; the integrated operational amplifier U4 is used for realizing logarithm operation and inverse amplification operation to obtain a required memristor control function, and the multiplier U8 is used for multiplying the memristor control function by an input voltage quantity to obtain a final memristor current quantity. The novel logarithmic absolute value local active memristor circuit model is used for simulating the volt-ampere characteristic of the local active memristor and replacing an actual local active memristor to carry out experiment, application and research.

Owner:HANGZHOU DIANZI UNIV

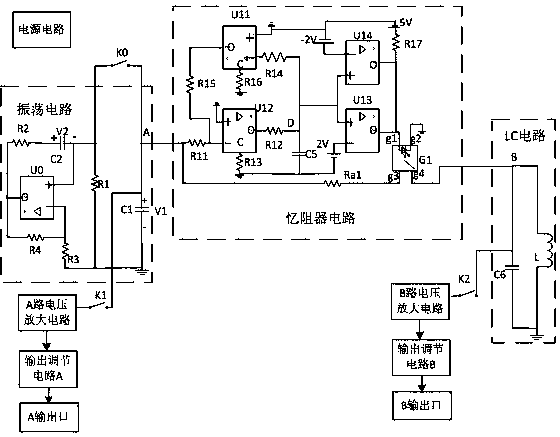

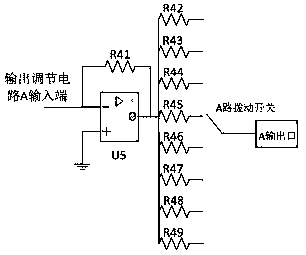

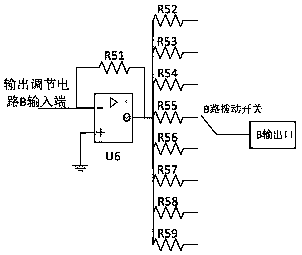

Chaotic signal generator with dual output

PendingCN109525383AImprove stabilityImprove anti-interference abilitySecuring communication by chaotic signalsSecure communicationSignal generator

The invention discloses a chaotic signal generator with dual output. The generator comprises a power supply circuit, a starting switch K0, an oscillation circuit, a memristor circuit, an LC circuit, an A-channel switch K1, an A-channel voltage amplifying circuit, an output adjusting circuit A, an A output port, a B-channel switch K2, a B-channel voltage amplifying circuit, an output adjusting circuit B, and a B output port. The memristor circuit, the LC circuit and the oscillating circuit work together to generate a chaotic signal with complex dynamic behaviors. When the switch K1 is closed, the chaotic signal passes through a signal amplifying circuit A and the output adjusting circuit A from an A channel, and is output from the A output port; and when the switch K2 is closed, the chaoticsignal passes through a signal amplifying circuit B and the output adjusting circuit B from a B channel, and is output from the B port output. According to the chaotic signal generator with dual output, a chaotic signal generator with dual output based on a new memristor circuit is designed by utilizing an oscillator principle. The chaotic signal generator can adjust the amplitude, has characteristics of being good in stability and strong in anti-interference, and is more suitable for application in secure communication.

Owner:XIHUA UNIV

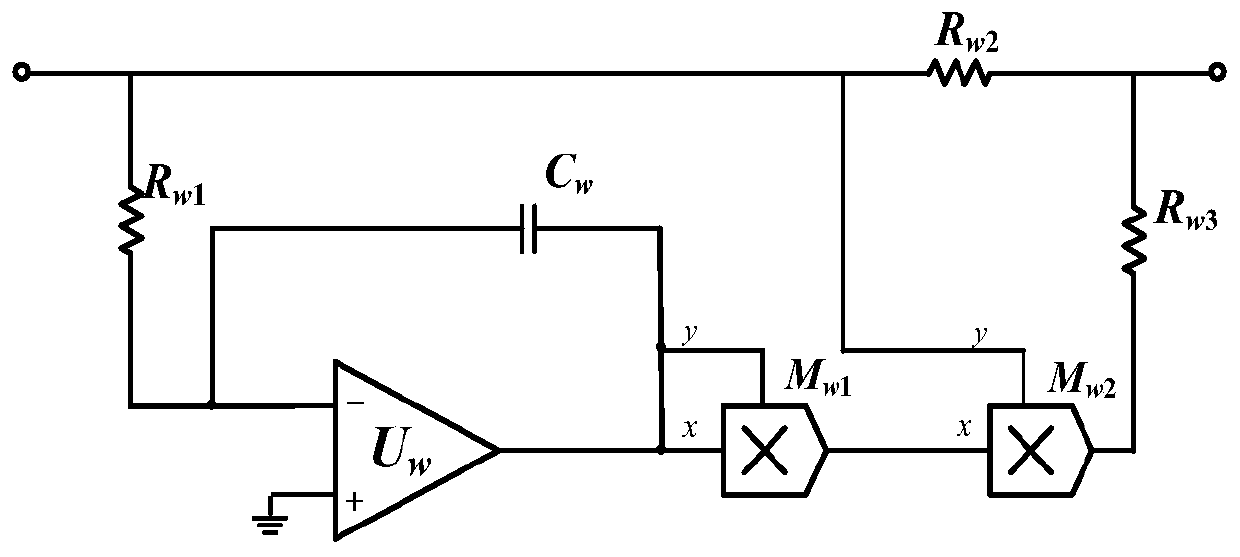

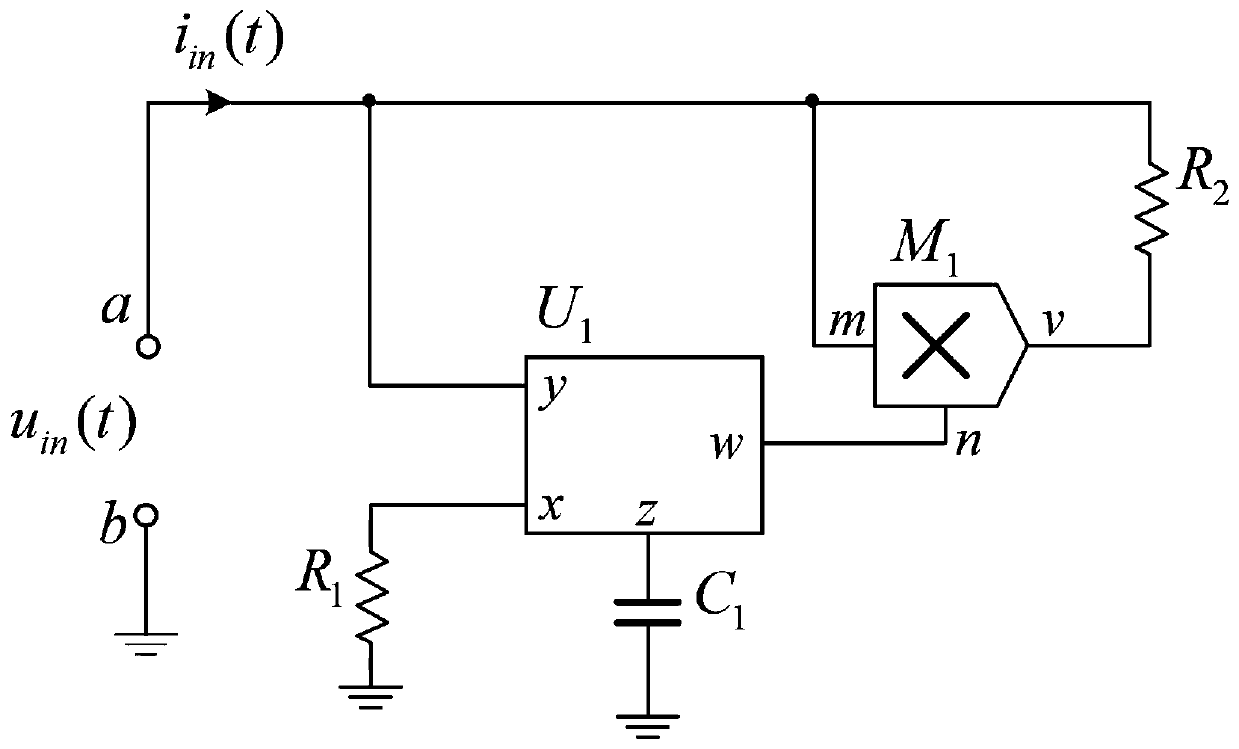

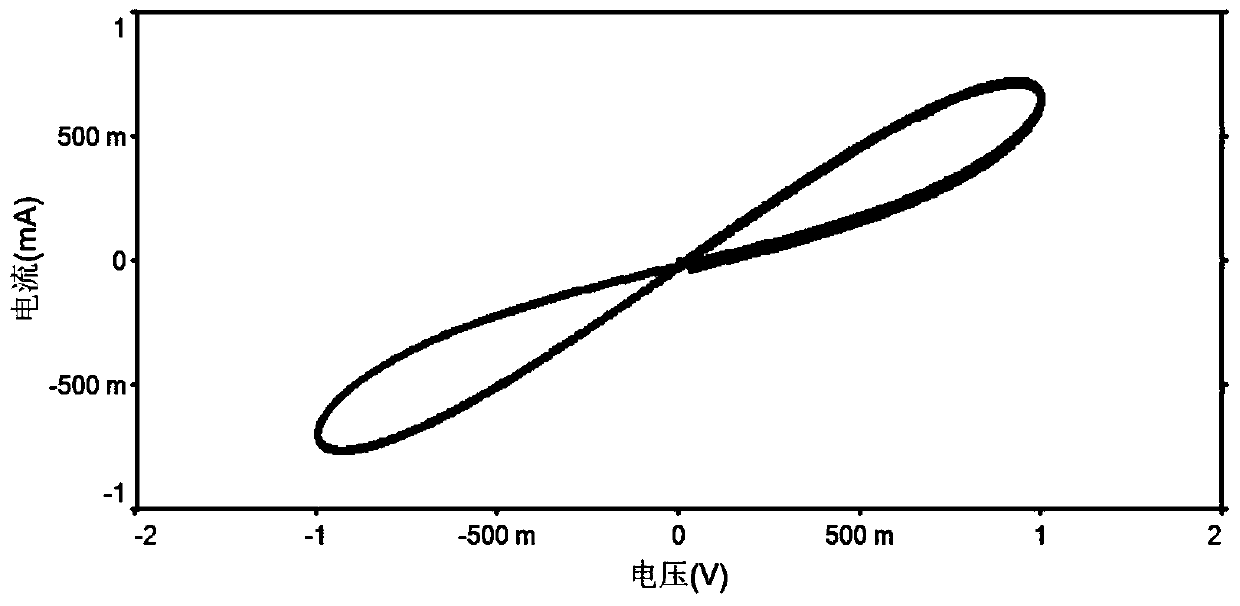

Secondary nonlinear magnetic control memristor simulator based on current transmitter

PendingCN110046472ASimple structureEasy to implementCAD circuit designSpecial data processing applicationsElectrical resistance and conductanceEngineering

The invention discloses a secondary nonlinear magnetic control memristor simulator based on a current transmitter, which comprises an integral operation circuit, a multiplier M1 and a resistor R2, andthe integral operation circuit comprises a current transmitter U1, a resistor R1 and a capacitor C1. The electrical characteristics of the ports a and b of the secondary nonlinear magnetic control memristor simulator are equivalent to the port characteristics of a magnetic control memristor, the input current of the internal integral operation circuit is 0, and circuits such as a voltage followerused for avoiding the load effect do not need to be connected to the input end in series. According to the secondary nonlinear magnetic control memristor simulator, an absolute value operation circuit is not needed, only five circuit components are needed, the structure is simple, implementation is convenient, and the secondary nonlinear magnetic control memristor simulator can be widely appliedto design of various memristor circuits (circuits such as memristor chaos, memristor bridge synapses and memristor neurons).

Owner:CHENGDU NORMAL UNIV

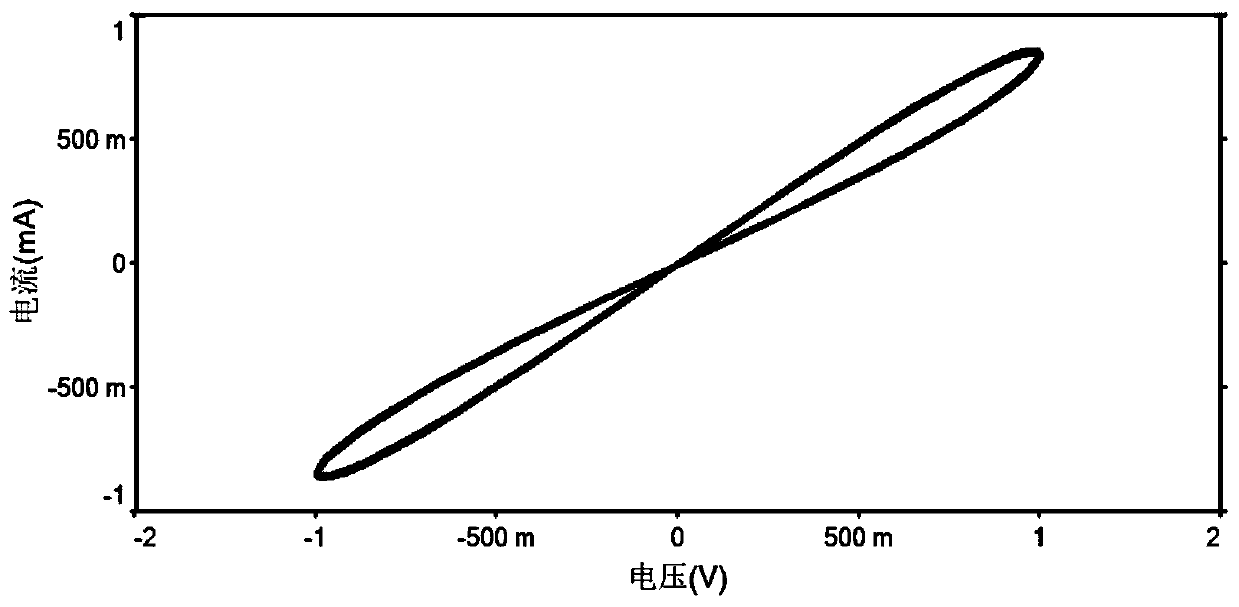

Very simple floating magnetic control memristor circuit simulation model

ActiveCN108804840AReduce complexityReduce component countSpecial data processing applicationsElectrical resistance and conductanceIntegrator

The invention discloses a very simple floating magnetic control memristor circuit simulation model which comprises a port a, a port b, a voltage controlled resistor UR, a resistor R and a voltage integrator A. The voltage controlled resistor UR comprises a voltage control end uc and a controlled resistor Ru; a resistance value of the controllable resistor Ru in the voltage controlled resistor UR is controlled by a voltage value of the voltage control end uc; and the voltage integrator A comprises a voltage input end u and a voltage output end uc. Electrical characteristics of the ports a and bof the floating magnetic control memristor circuit simulation model are equivalent to characteristics of A and B ports of a magnetic control memristor W, only needs to use existing three elements insimulation software, and is a two-port model; complexity and the element number of an existing magnetic control memristor circuit simulation model are further reduced; and the very simple floating magnetic control memristor circuit simulation model has the advantages of flexible memristive value changing range, no grounding limitation, wide working voltage range and easiness for understanding.

Owner:CHENGDU NORMAL UNIV

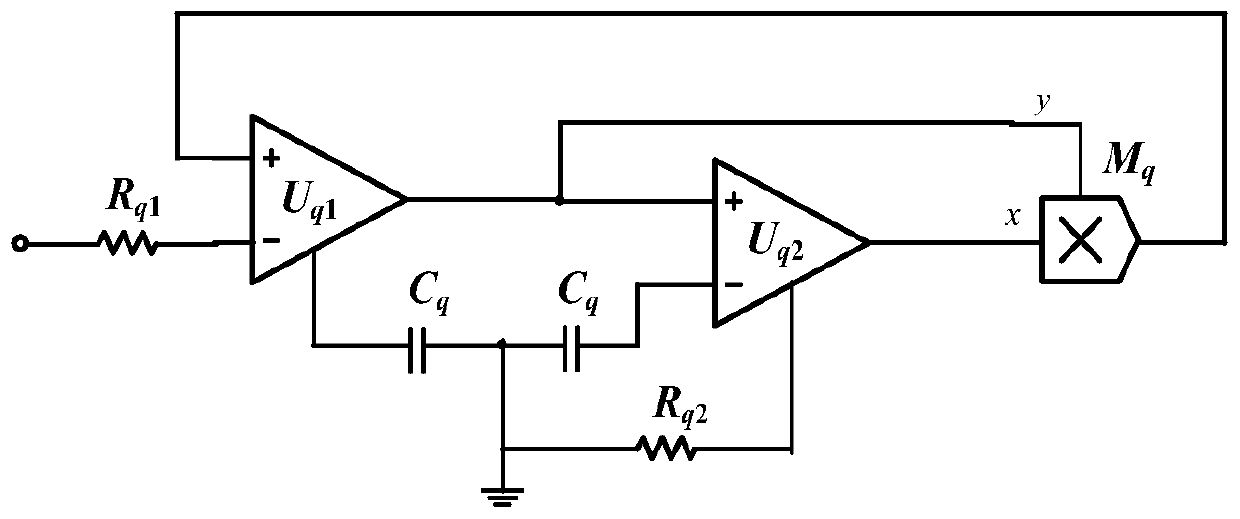

Binary memristor circuit simulator

PendingCN110765718AChange high resistance stateChanging the ratio of the low-resistance stateCAD circuit designEnergy efficient computingCapacitanceSimulation

The invention discloses a binary memristor circuit emulator, which adopts a binary memristor circuit emulator consisting of an operational amplifier, a current transmitter, a multiplier, a resistor and a capacitor, and adapts to different working frequency ranges by selecting integral circuit parameters. A reverse hysteresis circuit is adopted, so that the two resistance states of the memristor can be kept and switched, and the ratio of the high resistance state to the low resistance state can be changed by adjusting the parameters of the reverse addition circuit. The circuit simulator can bedirectly connected with an actual circuit component, and is suitable for research and application of the memristor in the field of digital logic.

Owner:HANGZHOU DIANZI UNIV

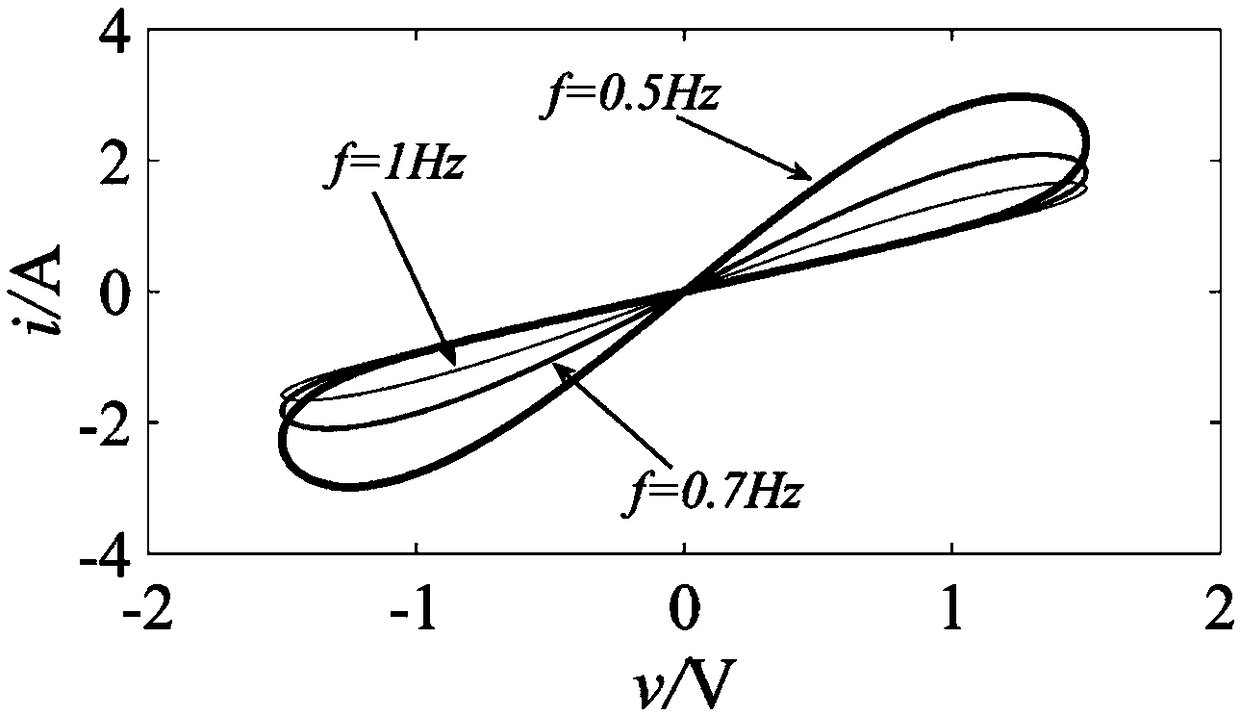

A digital circuit design method of heterogeneous dual-magnetron memristor model based on DSP Builder is presented

ActiveCN109359400AOvercome stabilityEasy to modifySpecial data processing applicationsEnergy efficient computingTheoretical computer scienceNon linear dynamic

A digital circuit design method of heterogeneous dual-magnetron memristor model based on DSP Builder is presented. Firstly, two heterogeneous magnetron memristor models with smooth cubic nonlinearityare constructed. Then a fifth-order heterogeneous magnetron memristor circuit model is constructed by combining two memristor models. Finally, the fifth-order heterogeneous magnetron memristor circuitmodel is digitally realized by DSP Builder platform. The invention overcomes the shortcomings of difficult parameter configuration and unstable performance of the designed chaotic analog circuit, andthe digital fine degree can reach the precision of 12 digits after the decimal point. The invention also has the advantages of easy modification of the parameters, easy design of the dynamics systemand stable performance, and provides a new idea for the digital design of the non-linear dynamics system.

Owner:JIANGXI UNIV OF SCI & TECH

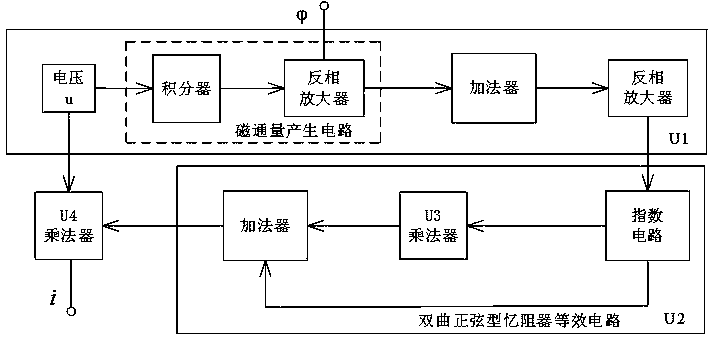

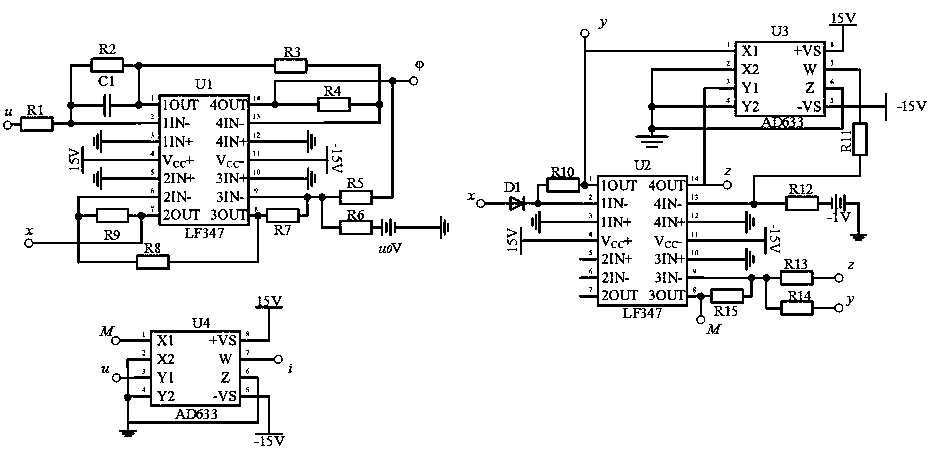

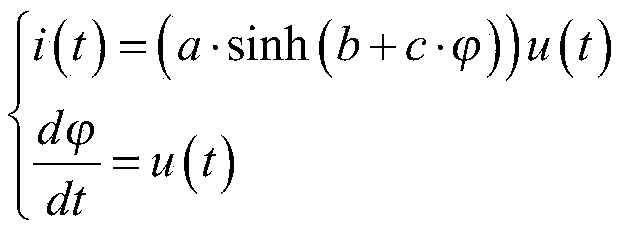

Hyperbolic sine type memristor circuit model

ActiveCN111079363ASimple structureCAD circuit designEnergy efficient computingControl signalHemt circuits

Owner:HANGZHOU DIANZI UNIV

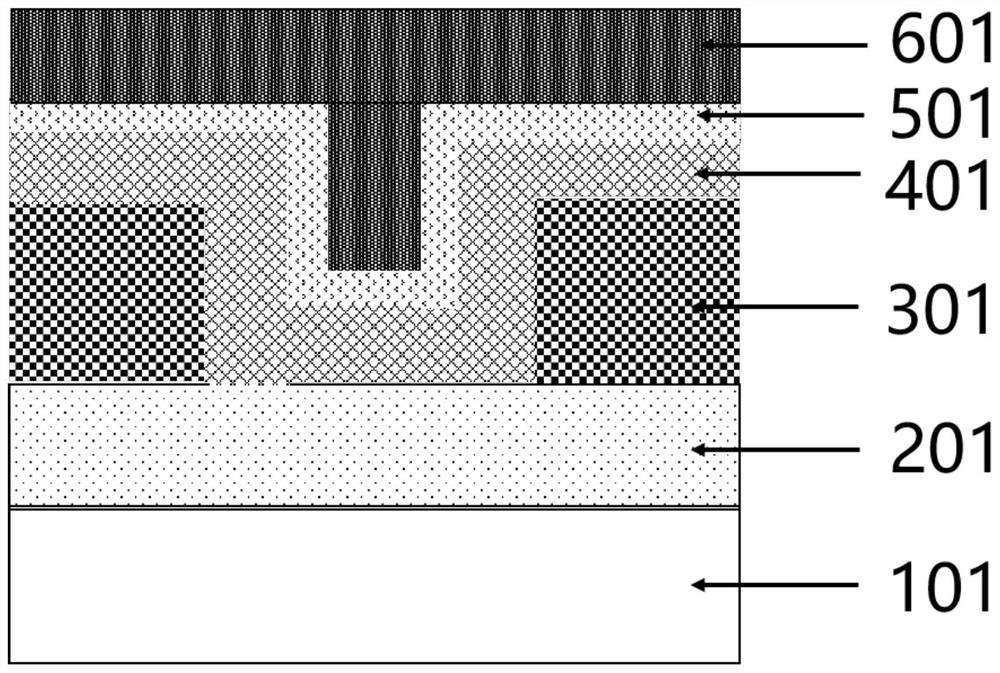

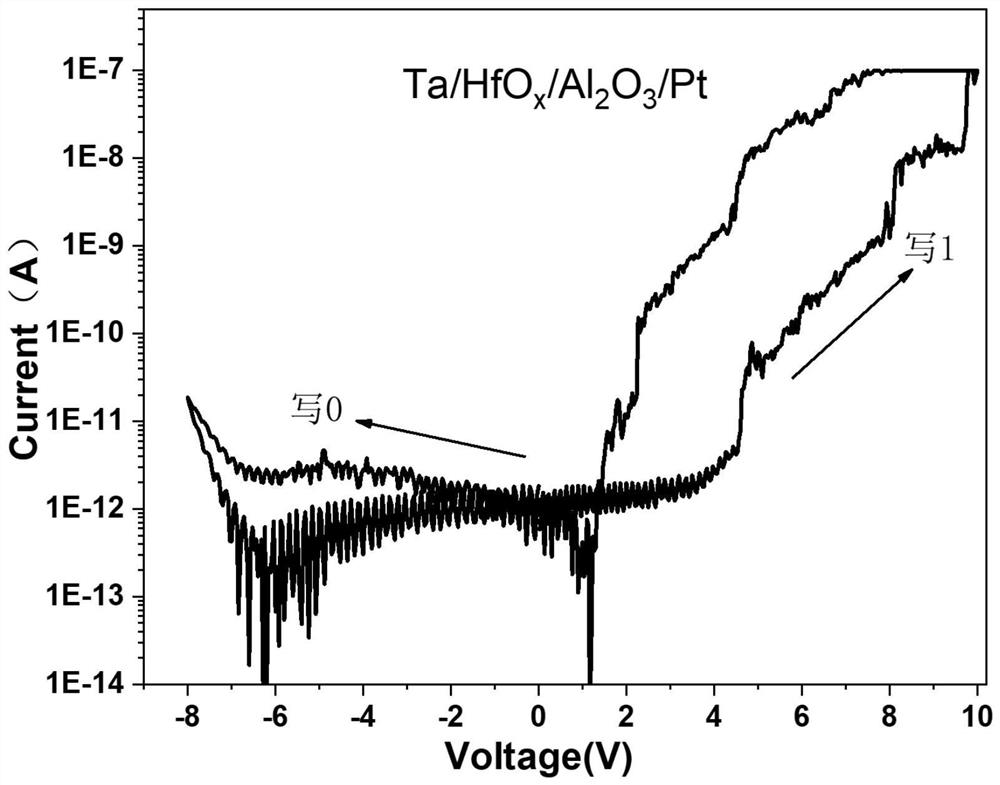

Storage and calculation integrated operation method and application of self-rectification memristor circuit

ActiveCN112951995AImplement cascading operationsEasy to operateElectrical apparatusEnergy efficient computingControl signalLogical operations

The invention provides a storage and calculation integrated operation method and application of a self-rectification memristor circuit, and belongs to the field of microelectronics. The method specifically comprises the following steps: based on different logic operations, applying different control signals to a self-rectification memristor to carry out data storage and calculation so as to realize different logic functions, wherein the logic operation acquisition method is based on a single self-rectification memristor, and comprises that logic operations corresponding to current input quantities of different self-rectification memristors are acquired by utilizing a logic operation formula according to a logic scheme of four variables, namely a current resistance value state of the self-rectification memristor, voltage application conditions of an upper electrode and a lower electrode and a reading direction of the self-rectification memristor, or based on the memristor circuit, the lower electrodes of the two self-rectification memristors are connected, and 16 complete logic operations can be realized by adjusting the current resistance value states of the self-rectification memristors P and Q. According to the invention, the self-rectification memristor logic operation and storage calculation integrated architecture provides theoretical support for the self-rectification memristor logic operation and storage calculation integrated architecture.

Owner:HUAZHONG UNIV OF SCI & TECH

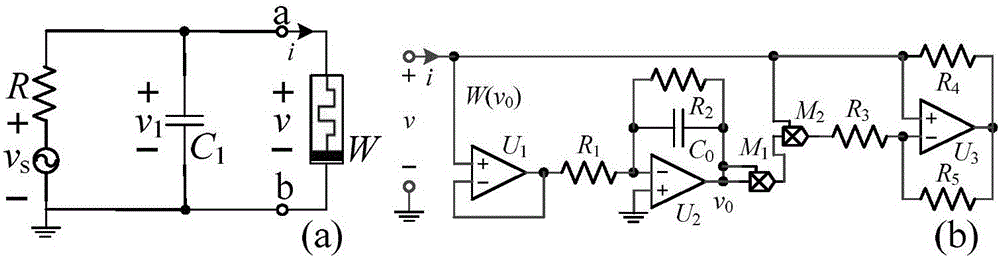

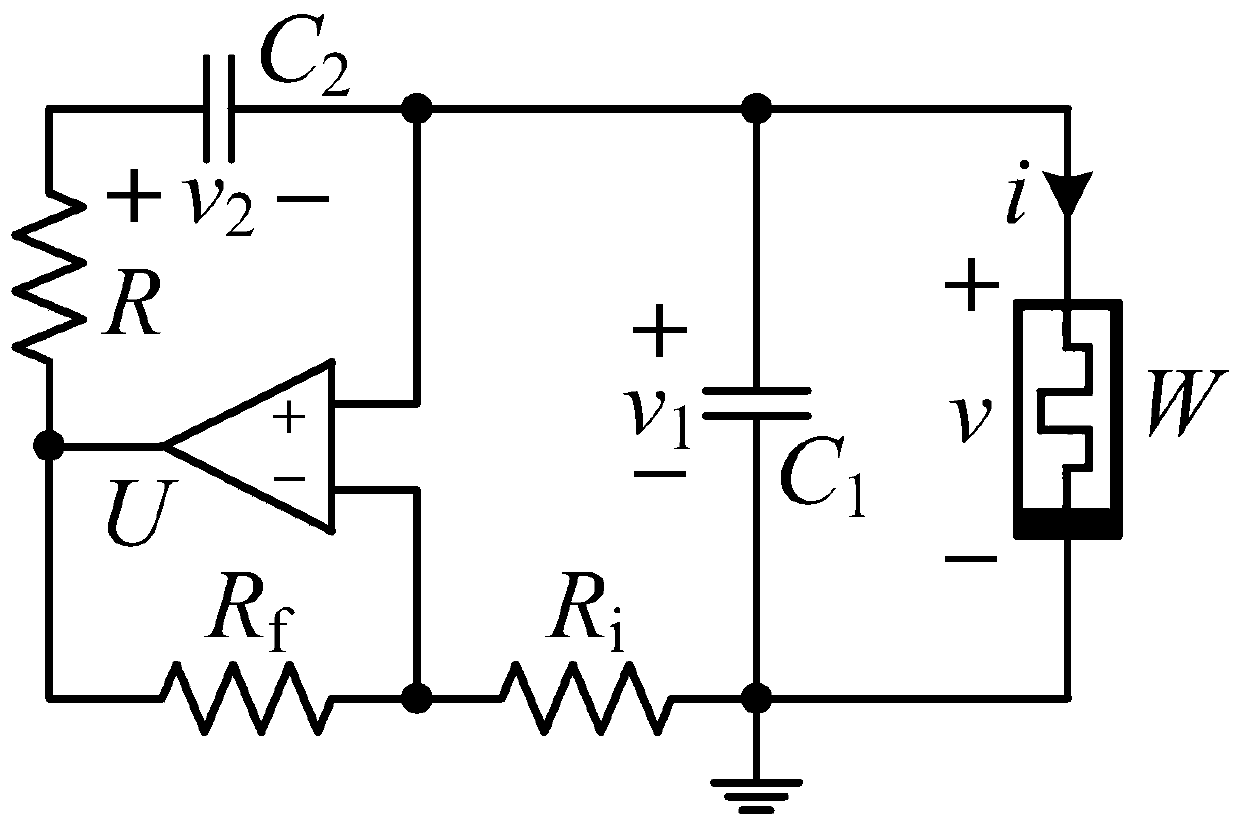

A third-order memristor Wien bridge chaotic oscillator

InactiveCN109831289ASimple structureStable jobSecuring communicationCapacitanceAudio power amplifier

The invention relates to a chaotic signal generation device, in particular to a third-order memristor Wien bridge chaotic oscillator which is simple in structure and stable in work, and can generate complex chaotic signals. The memristor circuit comprises an operational amplifier U, two capacitors C1 and C2, three resistors R, Rf and Ri and a memristor W. A resistor Rf is bridged between the inverting input end and the output end of the operational amplifier U, one end of the resistor Ri is connected with the inverting input end of the operational amplifier U, and the other end of the resistorRi is grounded. The positive end of the capacitor C1 is connected with the in-phase input end of the operational amplifier U, and the negative end of the capacitor C1 is grounded; wherein the negative electrode end of the capacitor C2 is connected with the in-phase input end of the operational amplifier U, the positive electrode end of the capacitor C2 is connected with the output end of the U after being connected with the resistor R in series, the positive electrode end of the memristor W is connected with the in-phase input end of the operational amplifier U, and the negative electrode endof the memristor W is grounded.

Owner:JIANGSU UNIV OF TECH