An FPGA and a system thereof, which support multi-bit stream downloading

A streaming download and bit stream technology, applied in the field of FPGA and its system, can solve the problems of large-scale use cost, configuration data leakage, single function, etc., and achieve the effect of increasing use efficiency, increasing robustness, and convenient updating.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

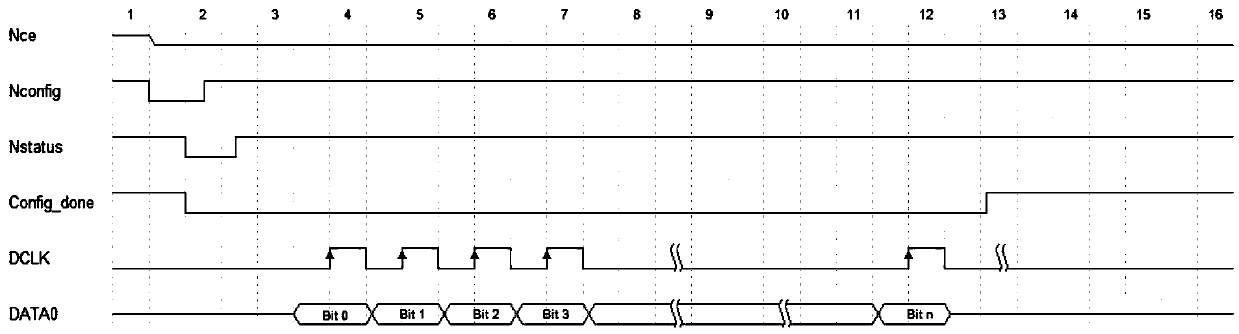

[0038] The existing FPGA configuration methods are generally divided into active configuration AS mode and passive configuration PS mode. Take ALTERA FPGA (Altera Corporation Altera) as an example: Among them,

[0039] The AS mode is: FPGA acts as a controller every time it is powered on, and the FPGA device guides the configuration operation process, controls the external memory and the initialization process, and actively sends a read data signal to the configuration device, thereby converting the bits of the EPCS (serial memory) The stream data is read into the FPGA, and the bit stream data is sent to the FPGA through the FPGA_DATA0 pin, and is synchronized on the FPGA_DCLK, and one clock transmits one bit of data.

[0040] PS mode: the configuration process is controlled by an external computer or controller, and it is completed through configuration devices such as enhanced configuration devices (EPC16, EPC8). EPCS is used as a control device, FPGA is used as a memory, an...

Embodiment 2

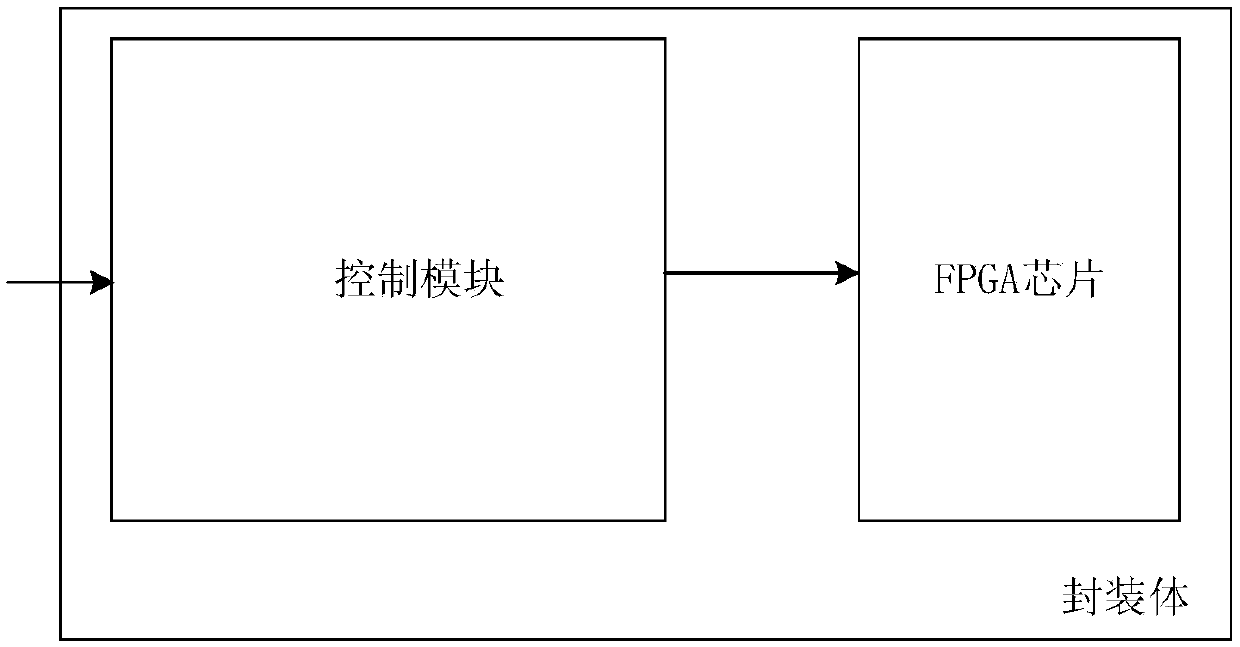

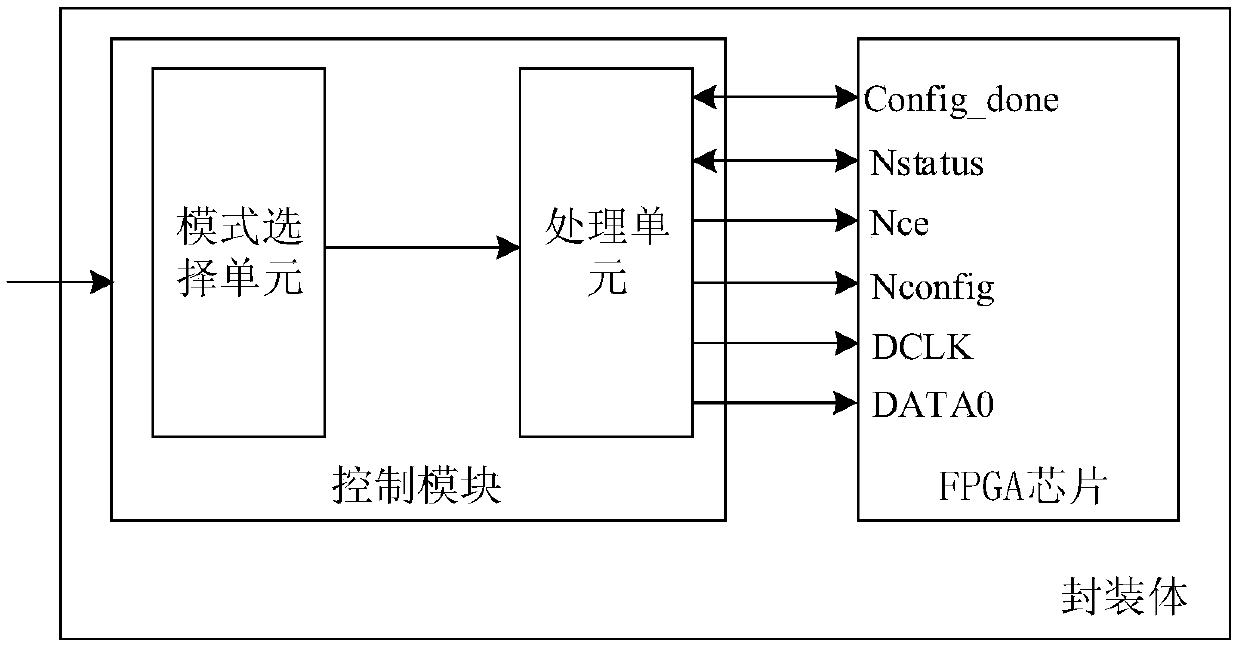

[0048] See figure 2 with image 3 , figure 2 A schematic structural diagram of another FPGA supporting multi-bit stream download provided by the present invention, image 3 A structural schematic diagram of another FPGA supporting multi-bit stream download provided by the present invention. In this embodiment, on the basis of the foregoing embodiments, a single-chip microcomputer chip is used as a control module and a memory card is used as an external storage device as an example, and the internal structure of the control module is further described in detail as follows.

[0049] The single-chip microcomputer chip may include a mode selection unit and a processing unit; wherein the mode selection unit is connected to the processing unit for selecting bit stream data. The processing unit is connected to the FPGA chip for downloading the bit stream data to the FPGA chip. Since there are multiple bit stream data with different functions stored in the external storage devic...

Embodiment 3

[0053] See Figure 4 with Figure 5 , Figure 4 A schematic structural diagram of another FPGA supporting multi-bit stream download provided by the present invention, Figure 5 A schematic structural diagram of yet another FPGA supporting multi-bit stream download provided by the present invention. This embodiment focuses on describing the decryption process of the FPGA of the present invention on the basis of the foregoing embodiments.

[0054] For some high-demand scenarios, bitstream data needs to be encrypted to protect data security. When the encrypted multi-bit stream data needs to be encrypted, corresponding data decryption needs to be performed.

[0055] The control module of this embodiment may include a decryption unit and a key unit. Wherein, the secret key unit is used to provide a secret key to the decryption unit; the decryption unit is used to decrypt the bit stream data to be transmitted with the secret key. Specifically, when configuring the FPGA through...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More