Semiconductor structures and methods of forming them

A semiconductor and graphics layer technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as poor performance of semiconductor structures

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] There are many problems in the method of forming the semiconductor structure, for example, the performance of the formed semiconductor structure is poor.

[0037] In combination with the formation method of the semiconductor structure, the reasons for the poor performance of the formed semiconductor structure are analyzed:

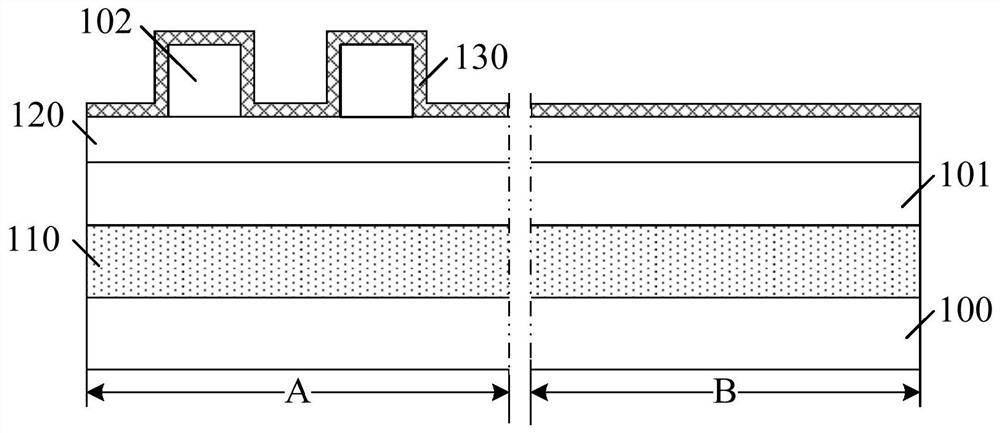

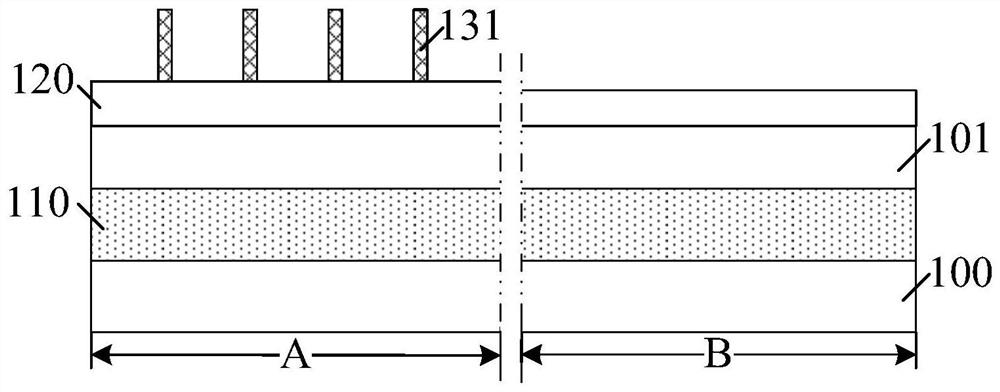

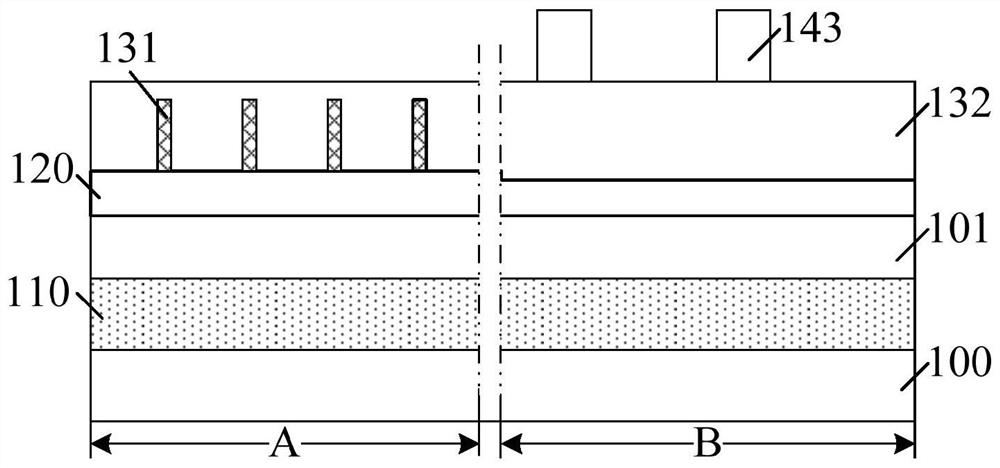

[0038] A substrate is provided, the substrate includes a first region and a second region; a dummy gate layer is formed on the substrate in the first region and the second region; a plurality of discrete first gate layers are formed on the dummy gate layer A pattern layer; a second pattern layer is formed on the dummy gate layer in the second region; the distance between the centers of adjacent second pattern layers is greater than or equal to twice the distance between adjacent first pattern layers; The first pattern layer and the second pattern layer are used as masks to etch the dummy gate layer to form a dummy gate.

[0039] Wherein, in order t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More