A method for measuring trap states of gate dielectric layer for insulated gate type hemt

A technology of insulating gate type and gate dielectric layer, which is applied in the field of microelectronics, can solve the problems that the quality of the dielectric layer cannot be determined, and the extraction of the dielectric layer cannot be applied.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0066] DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS An AlGaN / GaN heterojunction MIS-HEMT is taken as an example for illustration.

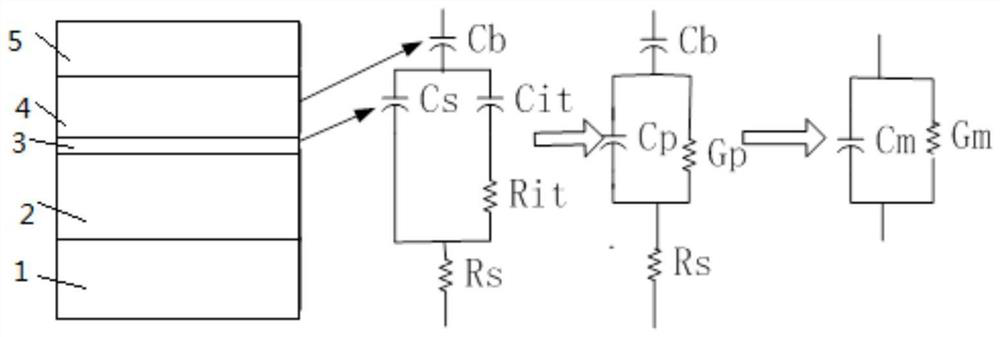

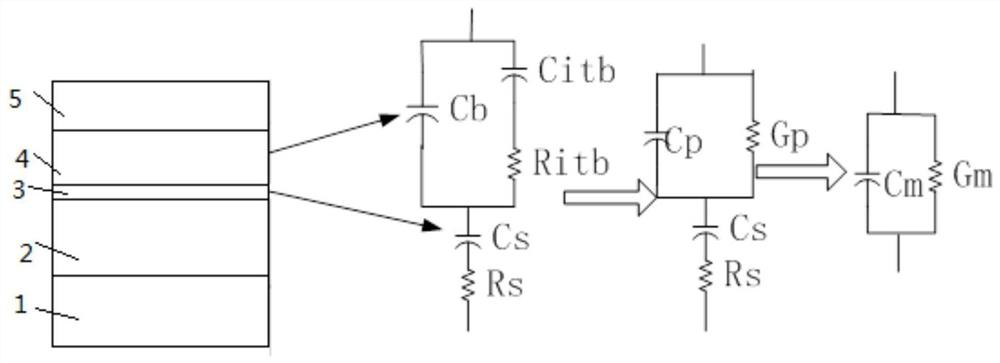

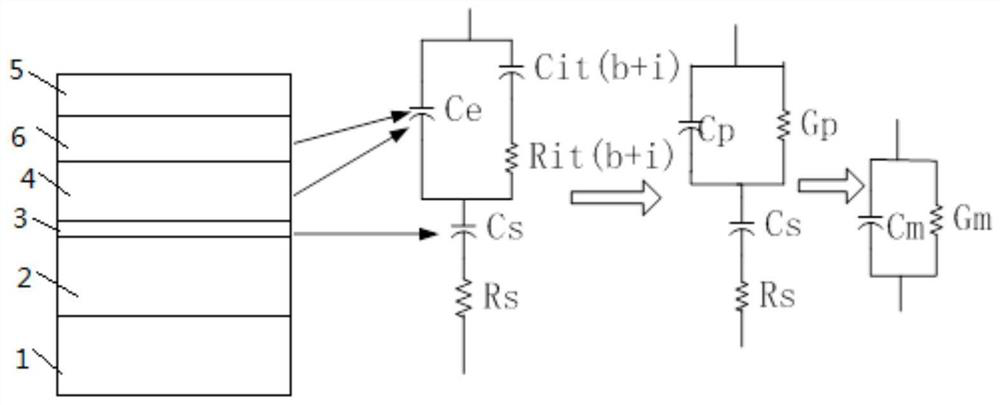

[0067] refer to figure 1 and figure 2 , the common HEMT structure used in the present invention, the structure is from bottom to top: substrate 1, transition layer 2, dielectric layer 3, barrier layer 4 and protection layer 5. refer to image 3 , The MIS-HEMT structure used in the present invention is as follows from bottom to top: substrate 1 , transition layer 2 , dielectric layer 3 , barrier layer 4 , insulating layer 6 and protection layer 5 .

[0068] The method for extracting the internal trap state of the gate dielectric layer in the present invention is as follows:

[0069] Step 1: Carry out the C-V characteristic test on the MIS-HEMT device and HEMT device used, obtain the corresponding C-V curve diagram, and determine the depletion voltage of the corresponding device according to the curve diagram; the C-V characteristic test cu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More