Inverted T-shaped tunneling field effect transistor

A tunneling field effect and transistor technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of low on-state current, low tunneling efficiency, and difficult to meet, and achieve low sub-threshold swing and good gate. The effect of control

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention will be further described below in conjunction with the accompanying drawings and embodiments.

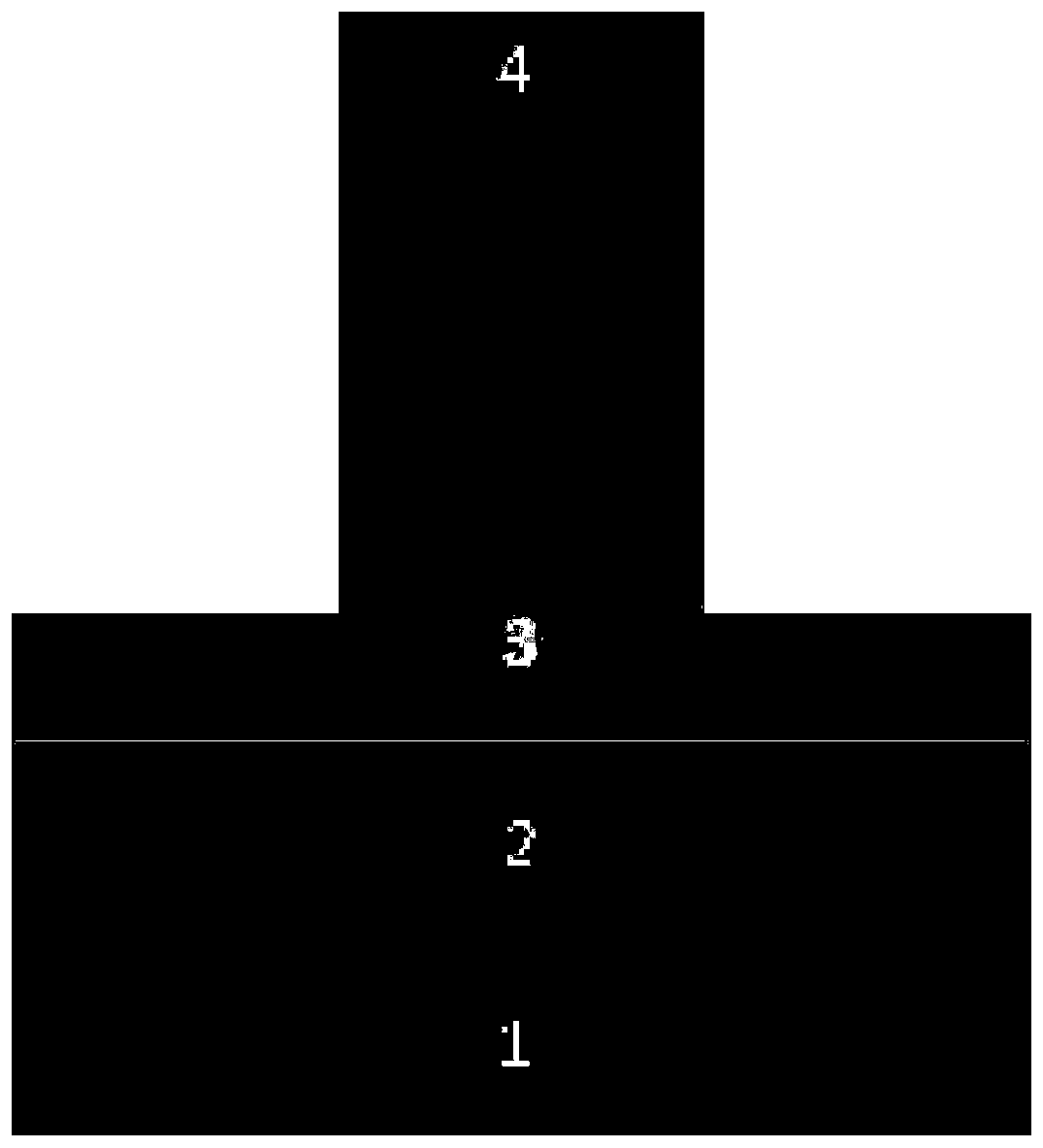

[0029] An inverted T-type tunneling field effect transistor, comprising a silicon substrate of an SOI wafer, a substrate insulating layer of the SOI wafer above the silicon substrate of the SOI wafer, and a heavily doped substrate above the insulating layer of the SOI wafer The impurity source region, two single crystal silicon thin films and two heavily doped drain regions, in which the heavily doped source region is located in the middle above the substrate insulating layer, and the two single crystal silicon thin films are both L-shaped, located at the heavily doped source The two heavily doped drain regions are located on the L-shaped bottom of the monocrystalline silicon film and are close to the outer edge of the lateral edge of the substrate insulating layer of the SOI wafer, and are located on the substrate insulating layer. above; there is a ga...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More