Semiconductor structures and methods of forming them

A semiconductor and conductive structure technology, applied in the field of semiconductor structure and its formation, can solve the problems of MOSFET performance to be improved, and achieve the effect of increasing size, reducing loss and improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] There are many problems in the semiconductor structure in the prior art, for example, the performance of the formed semiconductor structure is poor.

[0033] Combining with a semiconductor structure, the reason for the poor performance of the existing semiconductor structure is analyzed:

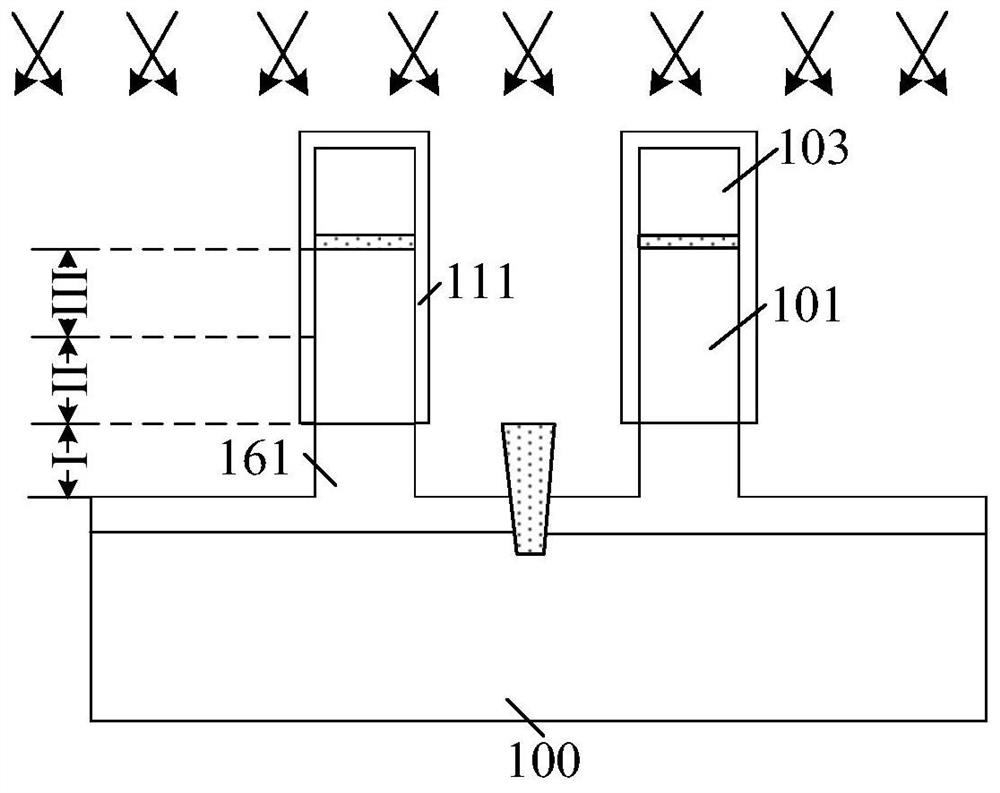

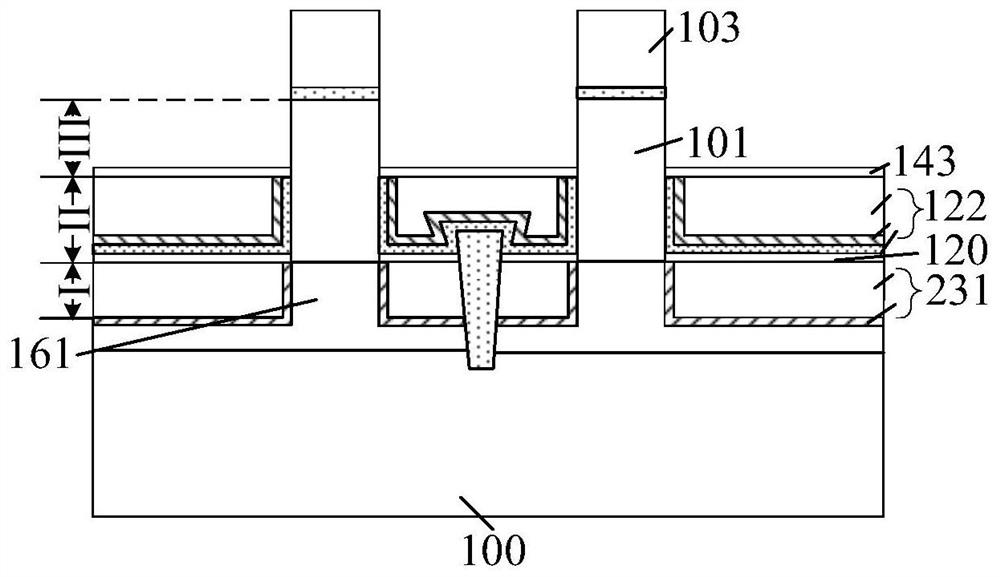

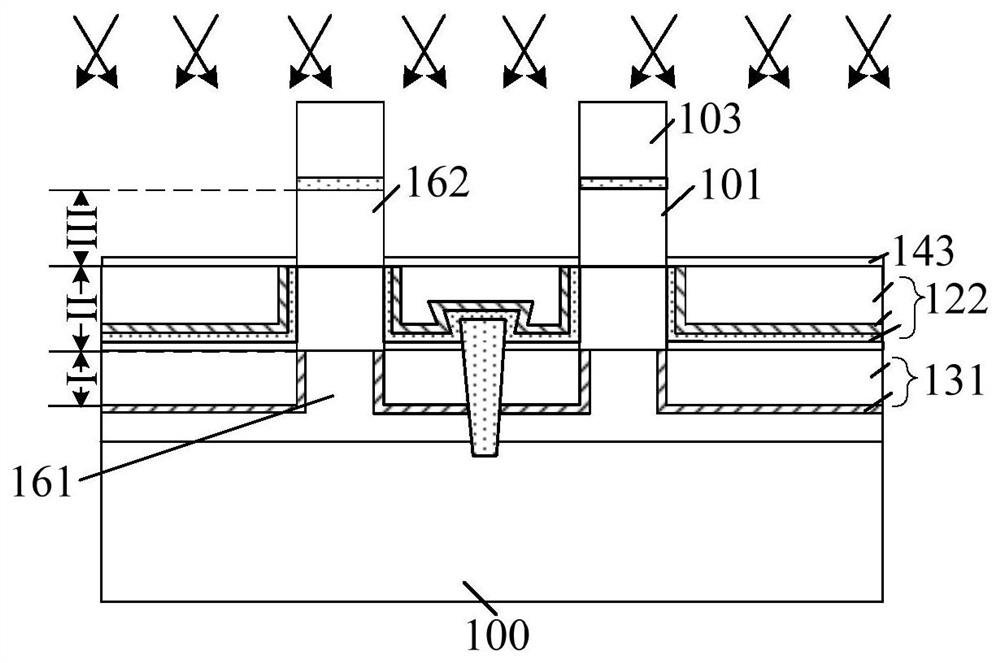

[0034] Figure 1 to Figure 3 It is a structural schematic diagram of each step of a method for forming a semiconductor structure.

[0035] Please refer to figure 1 , providing a substrate 100 having a fin post 101 thereon, the fin post 101 comprising a bottom region I; a channel region II located on the bottom region I; a channel region II located on the channel region II The top region III of the fin pillar 201 has a mask layer 203 on it.

[0036] continue to refer figure 1 , forming a sidewall 111 covering the top region III and the channel region II of the fin column 101; using the sidewall 111 as a mask to perform the first ion implantation on the fin column 101, in the fin c...

PUM

| Property | Measurement | Unit |

|---|---|---|

| size | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| height | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More