CMOS combination logic circuit

A combinatorial logic circuit, low-level technology, applied to logic circuits with logic functions, etc., can solve problems such as difficulty in meeting server performance requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

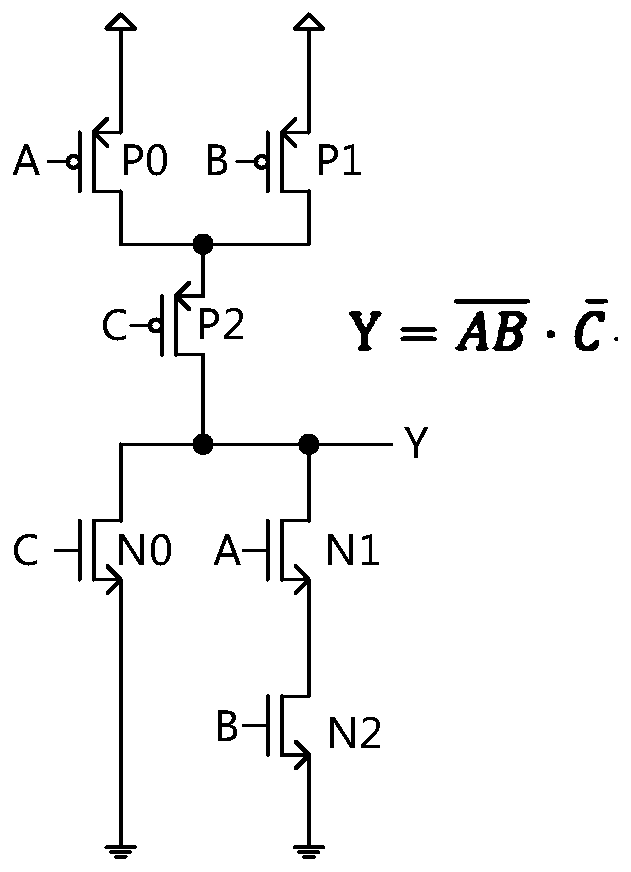

[0021] The technical solutions in the embodiments of the present invention will be clearly and completely described below with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only a part of the embodiments of the present invention, but not all of the embodiments.

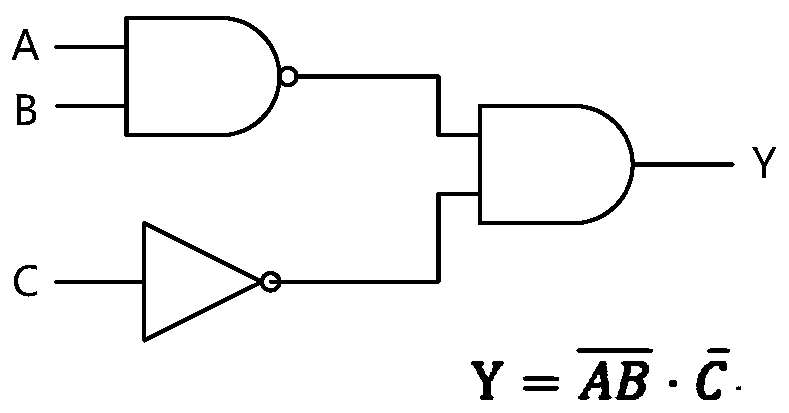

[0022] like figure 1 As shown, the present invention provides a circuit unit structure that realizes Logical operation function.

[0023] In the PMOS network, the first transistor, the second transistor and the third transistor are all PMOS transistors. The gate G of the first transistor P0 is connected to the first input signal A, the source S is connected to the power supply voltage VDD, the drain D is connected to the drain D of the second transistor P1 and the source S of the third transistor P2; The gate G of the transistor P1 is connected to the second input signal B, the source S is connected to the power supply voltage VDD, and t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com