A kind of array substrate and its manufacturing method and display panel

A technology of array substrates and substrate substrates, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., and can solve problems such as thinner thickness, short circuit of data lines, poor coverage, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

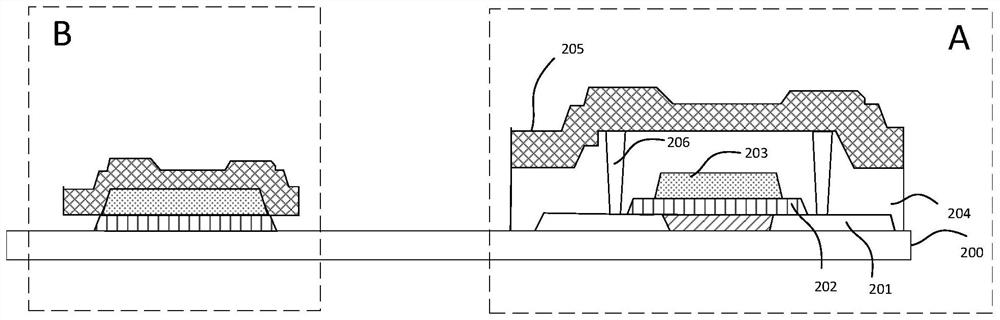

[0043] In order to make the purpose, technical solutions and advantages of the present application clearer, the technical solutions in the embodiments of the present application will be clearly and completely described below in conjunction with the drawings in the embodiments of the present application.

[0044] At present, there is no GI Tail in the metal traces of the array substrate, which leads to wrinkles at the intersection of the ILD and the Gate metal traces. After the SD metal traces are overlapped, the folds lead to gaps between the Gate metal traces and the SD metal traces. The thickness of the ILD film layer becomes thinner due to poor covering ability, and at the same time, a similar tip phenomenon will be formed after SD metal deposition, which is prone to DGS failure.

[0045] In view of this, the difference between the length of the gate insulating layer and the length of the gate in the metal wiring area of the array substrate in the embodiment of the present...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More