An automatic fault injection method for edif netlist-level combinational logic circuits

A technology of combinational logic circuits and fault injection, which is used in the detection of faulty computer hardware, electrical digital data processing, instruments, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

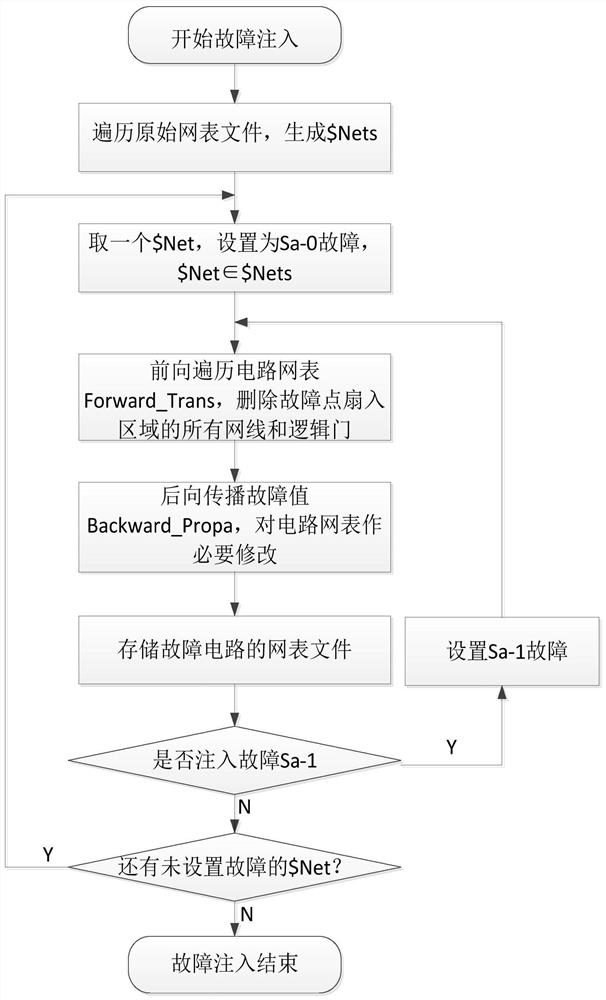

[0022] Embodiment 1: The specific process of an automatic fault injection method for an EDIF netlist-level combinational logic circuit in this embodiment is:

[0023] The root cause of circuit failure is a physical defect in the manufacturing process, which exhibits errors under certain excitation conditions, and eventually leads to system failure when the error exceeds a certain limit. Defect types include wafer defects, lithography defects, mask problems, process deviations, and oxidation problems, such as large bubbles in the material, surface ions, irregular tilting or shape deformation of components or connecting lines. Because the causes of physical failures are many and related to the process, physical failures are generally not studied directly, but modeled logical failures. Common logic fault models of integrated circuits include fixed faults, bridging faults, transient faults and time-delay faults. The fixed fault model mainly reflects the uncontrollability of a sig...

specific Embodiment approach 2

[0035] Embodiment 2: The difference between this embodiment and Embodiment 1 is that in step 1, the original netlist file is traversed, and the original netlist file is preprocessed; the specific process is:

[0036] Extract all network cables in the original netlist file, remove the initial input and initial output, and construct a network cable list $Nets, which is convenient for subsequent insertion of fault points.

[0037] Other steps and parameters are the same as in the first embodiment.

specific Embodiment approach 3

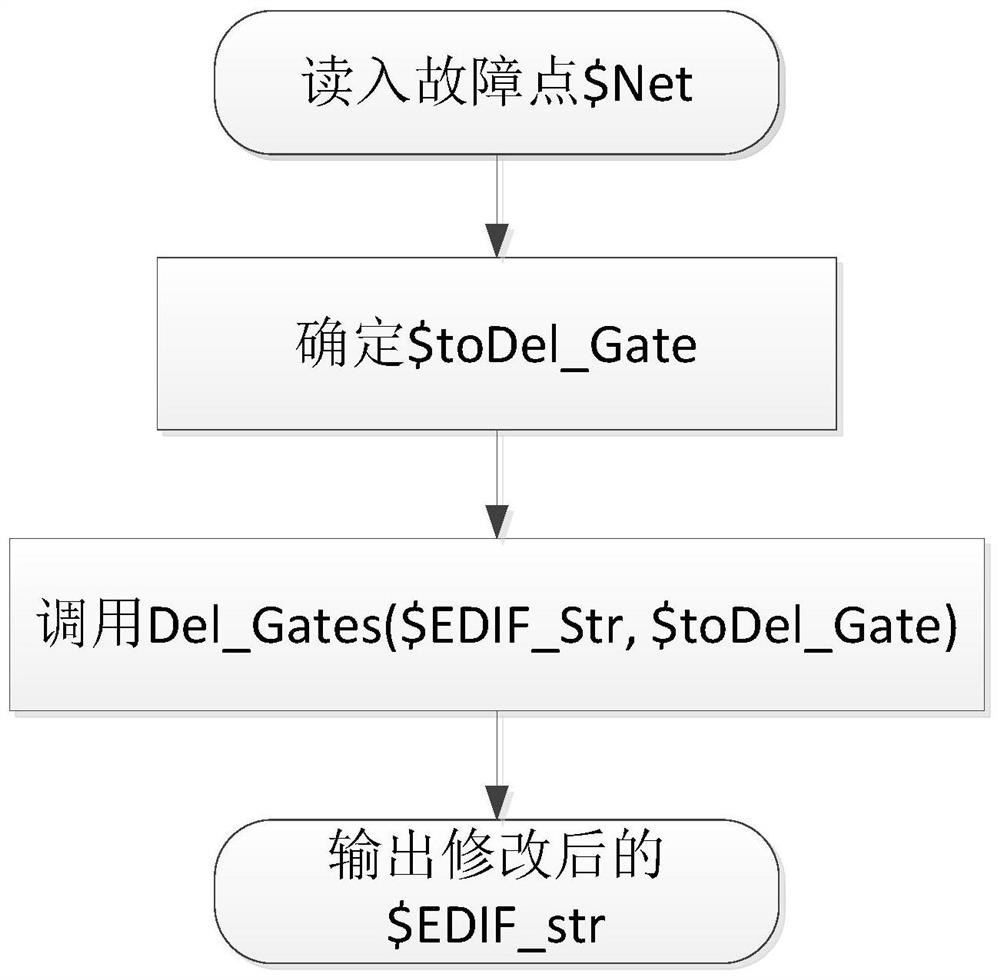

[0038]Embodiment 3: The difference between this embodiment and Embodiment 1 or 2 is that in step 3, forward traversal is performed according to the fault point, and the network cable corresponding to the fault point is deleted by reverse search to the input end of the logic gate. The logic gate $toDel_Gate connected to $Net, and the logic gate associated with the network cable corresponding to the fault point (the logic gate in the fan-in area); the specific process is:

[0039] First find the logic gate $toDel_Gate whose output terminal is connected to the network cable $Net corresponding to the fault point, then call the function Del_Gates($EDIF_str, $toDel_Gate) to delete the logic that the output terminal is only connected to the network cable $Net corresponding to the fault point Door.

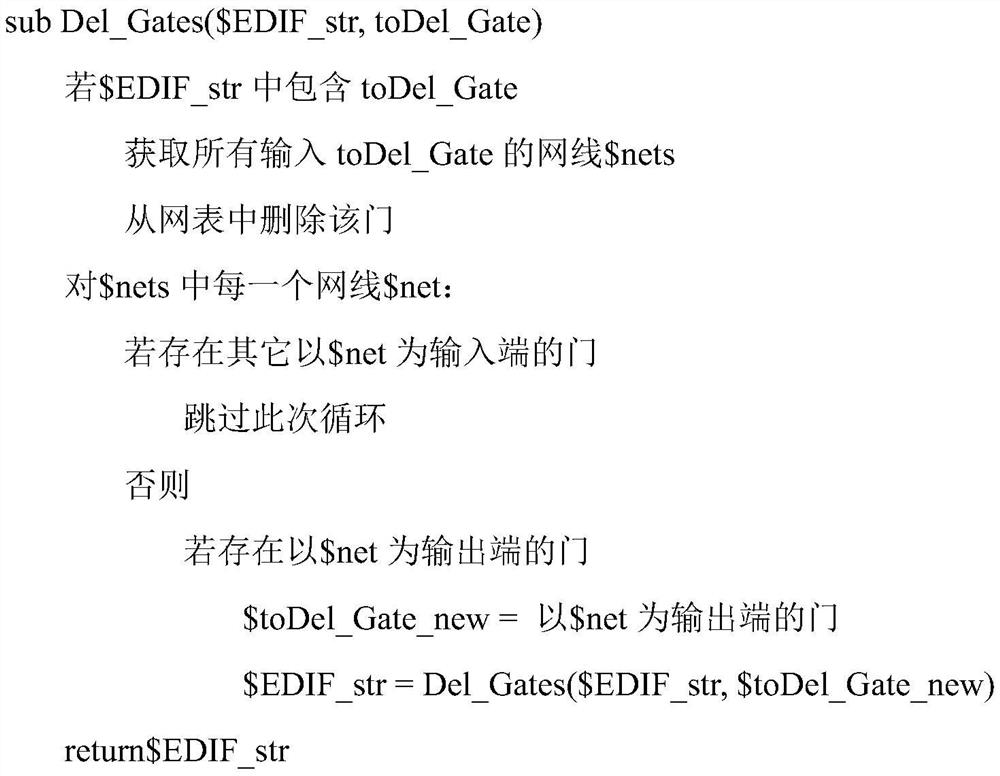

[0040] Among them, the Del_Gates($EDIF_str,toDel_Gate) function is a recursive function, and its pseudocode is described as follows:

[0041]

[0042] The backward propagation process...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More