Edge detection circuit and edge conversion circuit of integrated magnetic isolation chip

An edge detection and magnetic isolation technology, applied in pulse shaping, pulse description, etc., can solve problems affecting data transmission rate, the frequency of square wave signals should not be too high, complex encoding and decoding circuits, etc., to achieve voltage stability and improve stability and reliability, the effect of fast switching speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

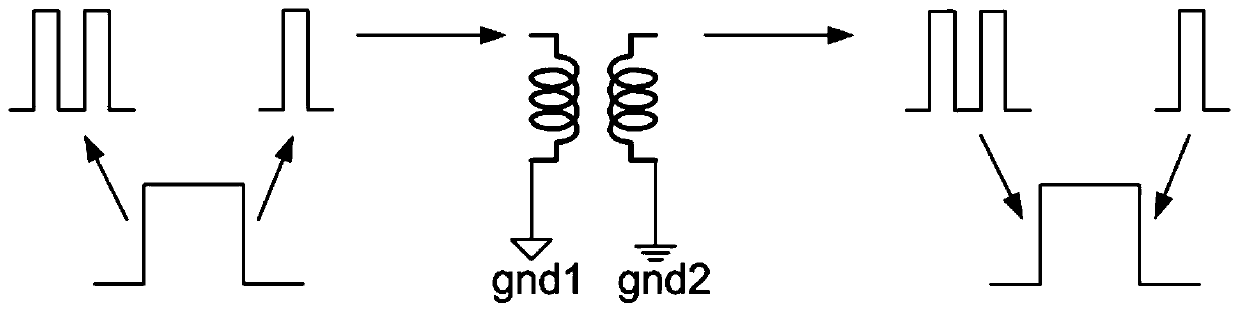

[0036] Existing edge detection circuits use the delay effect of digital logic gates to generate short pulses, such as Figure 4 and Figure 5 shown, where Figure 4 Used to detect the rising edge of the input square wave, Figure 5 Used to detect the falling edge of the input square wave. The input square wave signal reaches the AND gate or the NOR gate through two channels, one channel arrives directly, and the other channel passes through an odd number of inverters to delay and invert the input square wave, and finally obtain an AND rising signal at the output terminal of the AND gate. A short pulse corresponding to the edge, and a short pulse corresponding to the falling edge is obtained at the output of the NOR gate. The duration of the pulse depends on the delay time of the delay circuit. The role of the capacitor is to increase the delay time of the delay circuit. There is an obvious disadvantage of using an inverter for time delay, that is, the time delay of the in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More