MEMS wafer-level vacuum packaging method

A vacuum packaging, wafer-level technology, applied in decorative arts, measuring devices, microstructure devices, etc., can solve the problems of low vacuum degree of vacuum packaging, high gas leakage rate, and difficulty in maintaining vacuum degree for a long time, so as to improve the degree of vacuum , the effect of solving the problem

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0048] The invention provides a MEMS wafer-level vacuum packaging method, comprising the following steps:

[0049] S1, preparing the substrate layer,

[0050] Follow the sub-steps below:

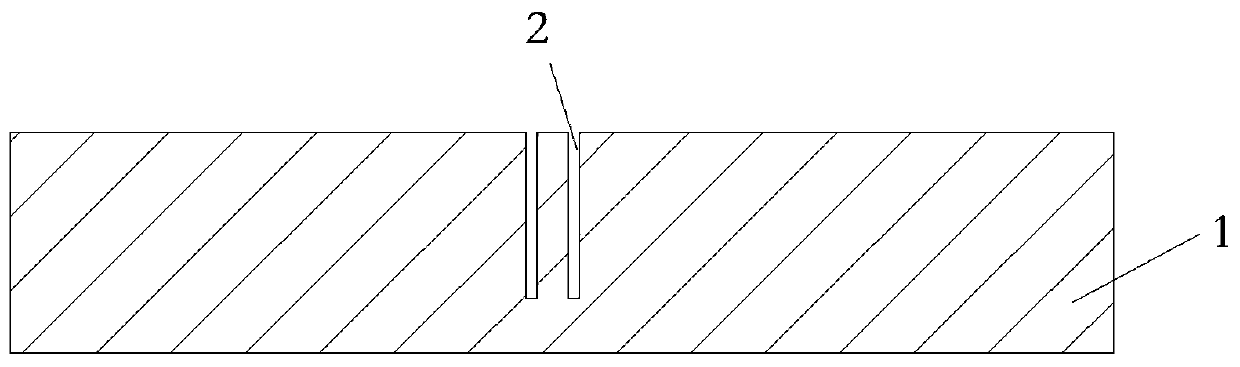

[0051] S11, such as figure 1 As shown, a double-polished silicon wafer with a thickness of 300-400 μm is used as the substrate layer silicon wafer 1, and an annular groove 2 is etched in the center of the top surface of the substrate layer silicon wafer 1 by photolithography; the depth of the annular groove 2 is 200-300 μm;

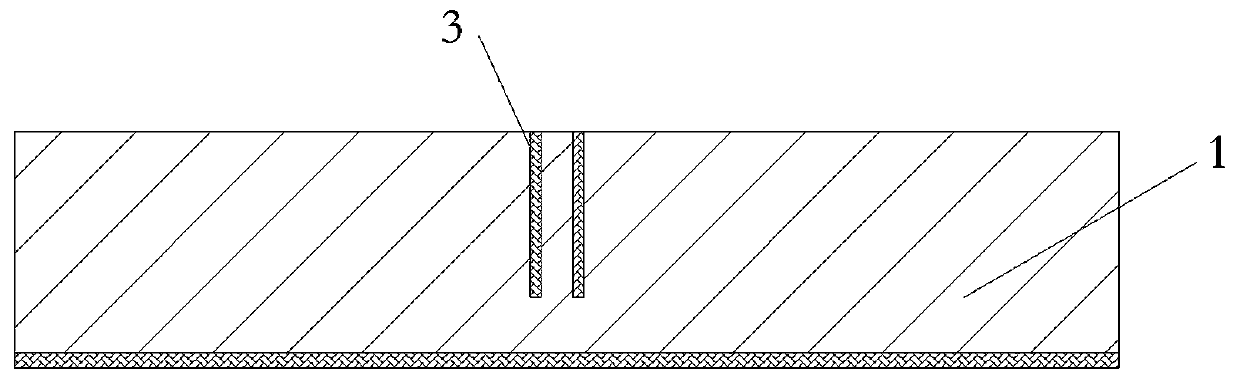

[0052] S12. Combination figure 2 As shown, an insulating layer with a thickness of 0.5 to 1 μm is grown on the side wall of the annular groove 2 by an oxidation process, and then polysilicon 3 is deposited on the surface of the substrate layer silicon wafer 1 by an LPCVD process to fill the annular groove 2;

[0053] S13. Combination image 3 As shown, the front surface of the silicon wafer 1 of the substrate layer is polished by a CMP process to expose the surface...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More