Method for direct growth of SOI

A direct and epitaxial growth technology, applied in the field of microelectronics, can solve the problems of complex preparation process and high production cost, and achieve the effects of simplifying the preparation process, saving consumables, and reducing production costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

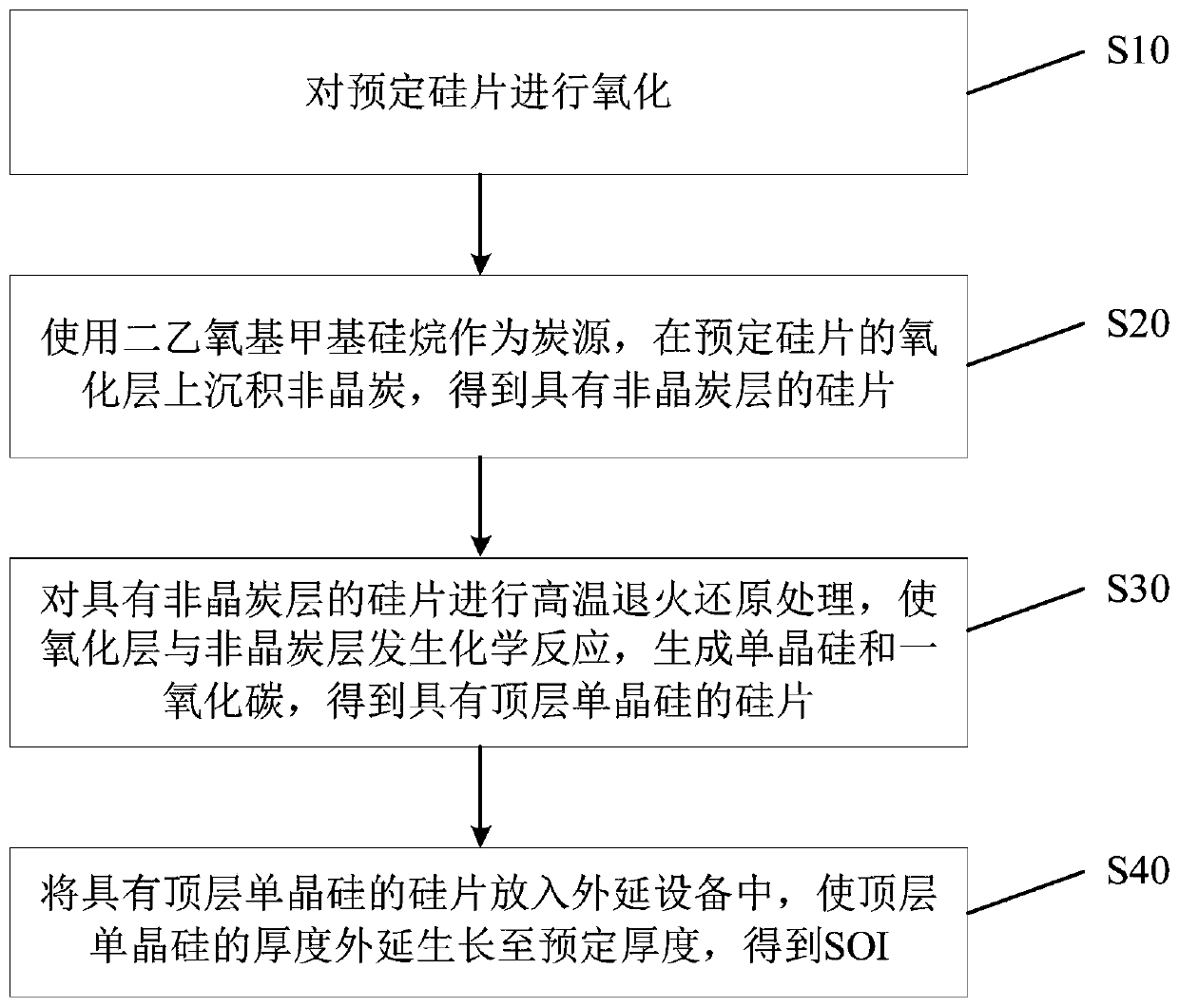

[0025] refer to Figure 1 to Figure 4 , in step S10, the predetermined silicon wafer 100 is oxidized.

[0026] Preferably, the predetermined silicon wafer 100 is a P-type silicon wafer with a resistivity of 8.5-11.5 ohm.cm and a crystal orientation.

[0027] As an example, dry oxygen and / or wet oxygen oxidation may be used to oxidize the predetermined silicon wafer 100 .

[0028] Preferably, the predetermined silicon wafer 100 is oxidized under the oxidation conditions of an oxygen flow rate of 500 sccm, an air pressure of 230 torr, and a temperature of 900° C. to obtain a silicon wafer with an oxide layer 102 having a thickness of 1 μm.

[0029] In step S20, use diethoxymethylsilane (DEMS) as a carbon source (i.e., C source), deposit amorphous carbon on the oxide layer 102 of the predetermined silicon wafer 100, and obtain a silicon wafer with an amorphous carbon layer 104 .

[0030] Preferably, under the deposition conditions that the flow rate of the carbon source is 1....

Embodiment 2

[0049] This embodiment provides a method for directly growing SOI, including:

[0050] Under the oxidation conditions of an oxygen flow rate of 900 sccm, an air pressure of 460 torr, and a temperature of 950° C., the predetermined silicon wafer 100 is oxidized to obtain a silicon wafer with an oxide layer 102 having a thickness of 1 μm.

[0051] Under the deposition conditions that the flow rate of the carbon source is 4.5g / s and the deposition temperature is 550°C, the chemical vapor deposition method is used to deposit amorphous carbon on the oxide layer 102 of the predetermined silicon wafer 100 to obtain the thickness of the amorphous carbon layer 104 70A silicon wafer.

[0052] Put the silicon wafer with the amorphous carbon layer 104 into a high-temperature furnace, under the conditions of high-temperature annealing reduction treatment with an annealing pressure of 0.8 torr, an annealing temperature of 1300° C., and an annealing time of 6 hours, with helium as protection...

Embodiment 3

[0056] This embodiment provides a method for directly growing SOI, including:

[0057] The predetermined silicon wafer 100 is oxidized under the oxidation conditions of an oxygen flow rate of 1900 sccm, a gas pressure of 760 torr, and a temperature of 1000° C. to obtain a silicon wafer with an oxide layer 102 having a thickness of 1 μm.

[0058] Under the deposition conditions that the flow rate of the carbon source is 3g / s and the deposition temperature is 750°C, the chemical vapor deposition method is used to deposit amorphous carbon on the oxide layer 102 of the predetermined silicon wafer 100, and the thickness of the amorphous carbon layer 104 is obtained. 100A silicon wafer.

[0059] Put the silicon wafer with the amorphous carbon layer 104 into a high-temperature furnace, under the conditions of high-temperature annealing reduction treatment with an annealing pressure of 5 torr, an annealing temperature of 1400° C., and an annealing time of 6 hours, with helium as prote...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| evenness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More