Efficient decoder architecture suitable for 5G LDPC code

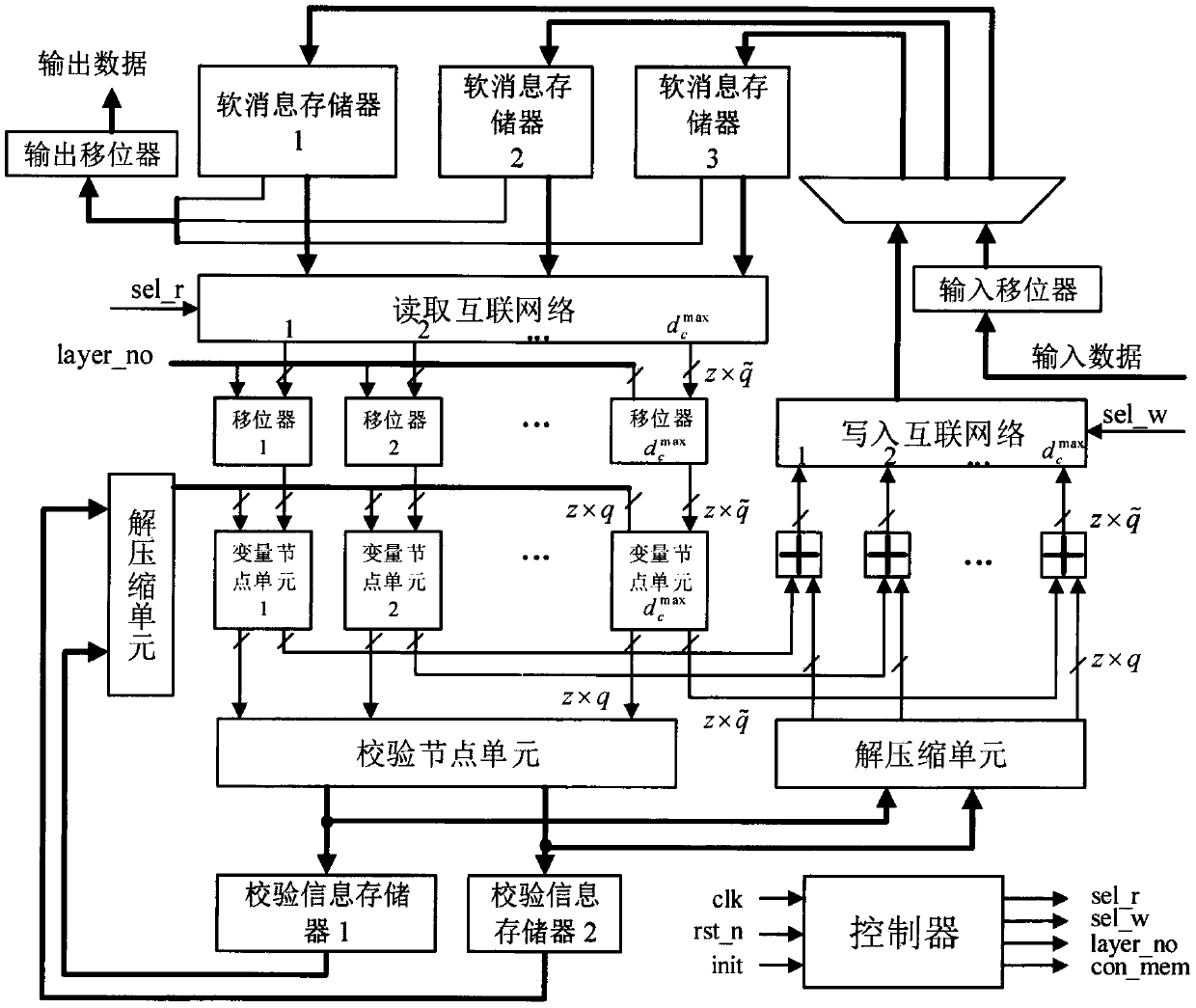

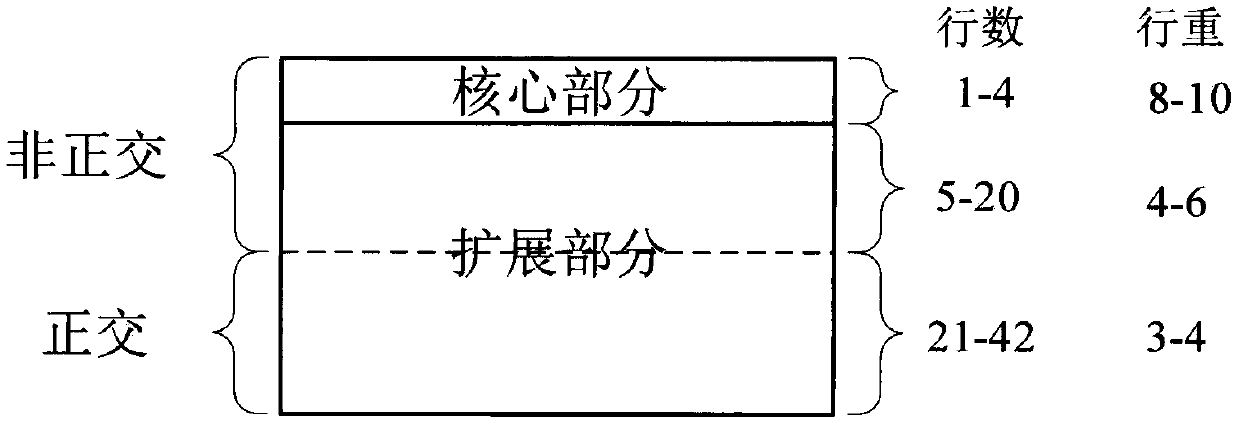

A decoder and decoding technology, applied in the field of high-throughput, low-complexity decoder architecture, can solve problems such as resource waste and unsatisfactory throughput, reduce the number of layers, and improve throughput-area Effects of performance ratio, area reduction and delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

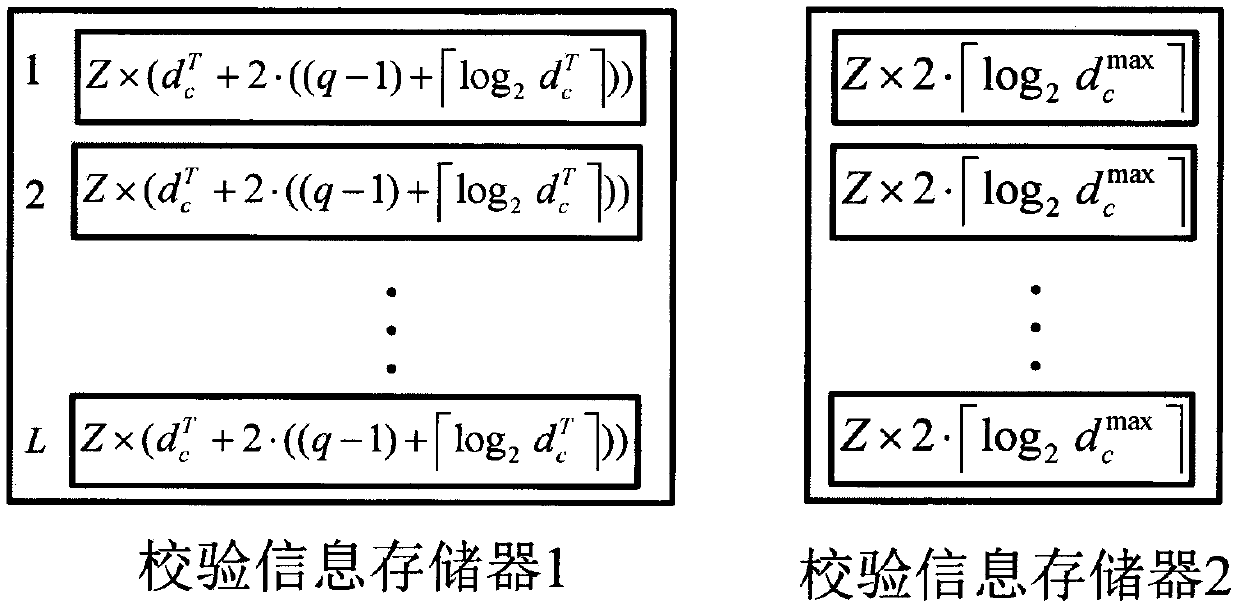

Method used

Image

Examples

Embodiment

[0032] Embodiment: Take the 5G LDPC code defined by BG2 as an example with a code length of 2600 and a code rate of 1 / 5 to implement the decoder architecture disclosed in the present invention. The decoder is described in Verilog language, and the obtained RTL is synthesized with Synopsys tools, and the technology used is TSMC 90nm CMOS technology. The comprehensive results show that after using the optimization method disclosed by the present invention, the operating frequency of the decoder is increased from 121Mhz to 164MHZ, and the area is increased from 1.831mm 2 down to 1.236mm 2 , the throughput rate increased from 524Mbps to 947Mbps. For a more intuitive comparison, we also compare the throughput-to-power ratio. By using the optimization method announced by the present invention, the throughput-power consumption ratio of the decoder is increased by 286.1Mbps / mm 2 Increased to 766.2Mbps / mm 2 , up to 2.68 times of the original.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More